Altera Corporation 2–13

April 2012 Cyclone III FPGA Starter Board Reference Manual

Board Components and Interfaces

Board Specific LEDs

The power LED illuminates when the board’s power is on and working.

The configuration done LED illuminates when the FPGA is configured.

1 Because of the Quartus II software pin placement rules in

various memory banks, you may only be able to use one or two

of the LEDs with DDR designs.

■ Configuration done LED: The Conf_Done LED illuminates when

the FPGA is configured with any design.

■ Flash signal LED: The flash_CE_n LED illuminates when the CE_n

signal to the flash is asserted indicating the flash is being accessed.

■ Power LED: The power LED illuminates when power is applied to

the board.

Memory

The Cyclone III FPGA starter board includes the following memories:

■ Parallel flash

■ DDR SDRAM

■ SSRAM

Parallel Flash

The Cyclone III starter board has a 8M x 16 low voltage parallel flash.

Table 2–11 lists the parallel flash board reference and manufacturing

information.

Table 2–12 shows the parallel flash signal name, corresponding FPGA

pin, signal direction, type, and board reference U6 flash pin.

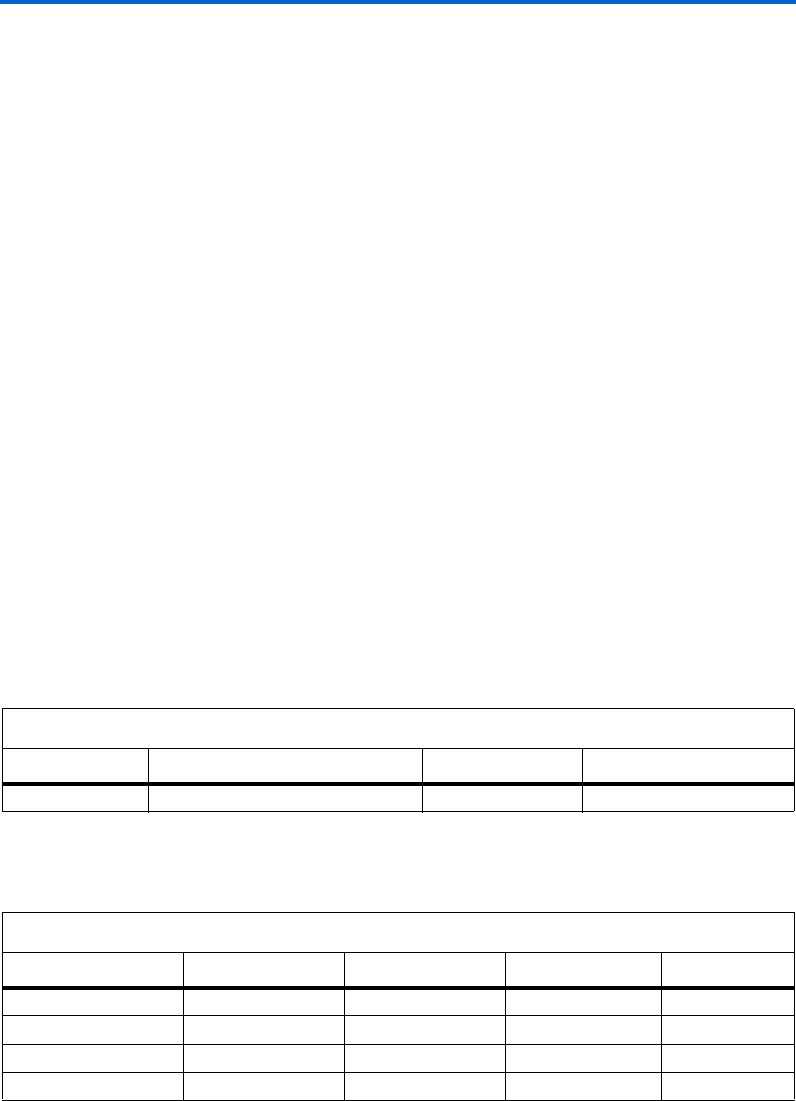

Table 2–11. Parallel Flash Manufacturing Information

Board Reference Description Manufacturer Manufacturer Part Number

U6 8M x16 low voltage parallel flash Intel PC28F128P30BF65

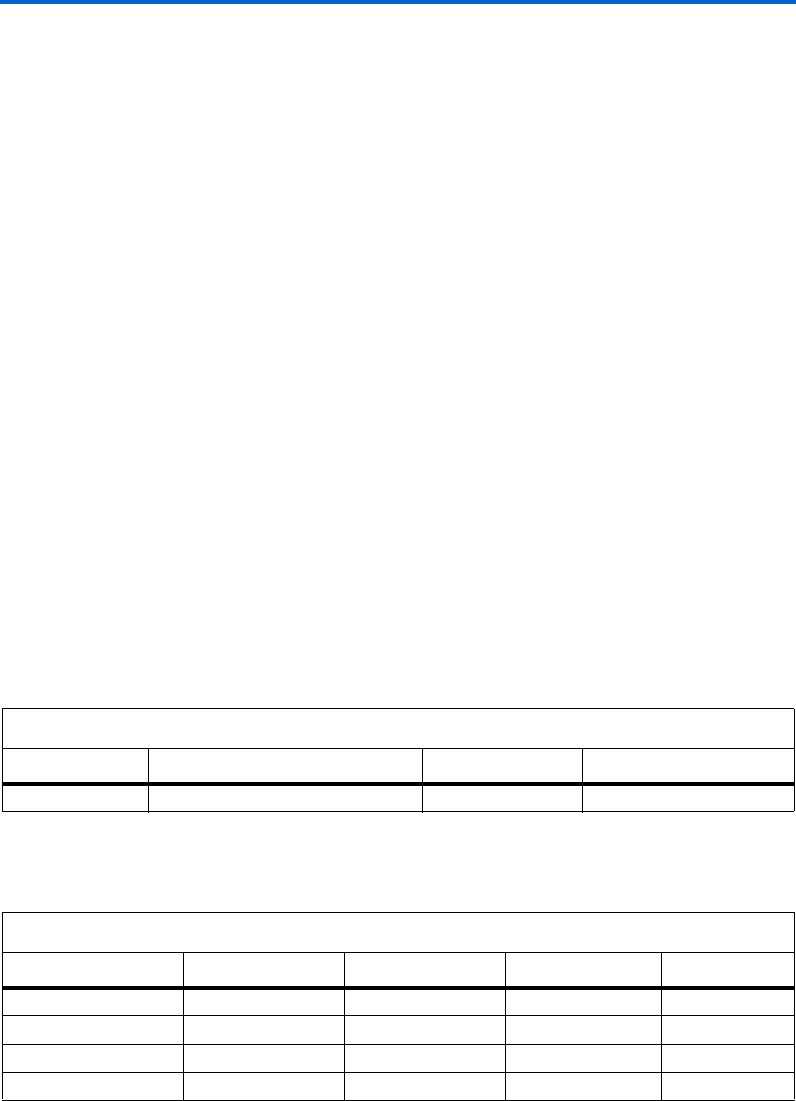

Table 2–12. Parallel Flash Memory Pinout (Part 1 of 3)

Signal Name FPGA Pin Direction Type U6 (Flash) Pin

flash_sram_a1 E12 Output2.5 V A1

flash_sram_a2 A16 Output2.5 V B1

flash_sram_a3 B16 Output2.5 V C1

flash_sram_a4 A15 Output2.5 V D1