2–18 Altera Corporation

Cyclone III FPGA Starter Board Reference Manual April 2012

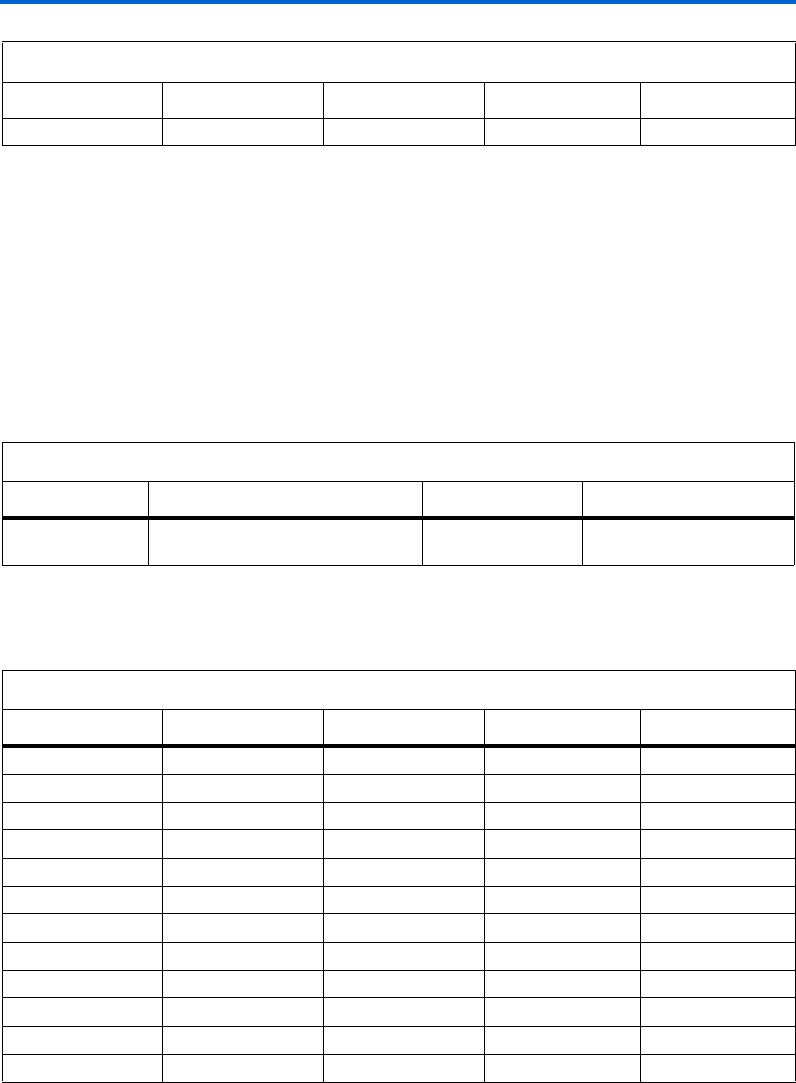

Memory

flash_sram_a14 C10 Output2.5 V 50

flash_sram_a15 D10 Output2.5 V81

flash_sram_a16 E10 Output2.5 V82

flash_sram_a17 C9 Output2.5 V 99

flash_sram_a18 D9 Output2.5 V 100

flash_sram_a19 A7 Output2.5 V 43

flash_sram_a20 A6 Output2.5 V 42

flash_sram_a21 B18 Output2.5 V 39

flash_sram_a22 C17 Output2.5 V 38

flash_sram_dq0 H3 Bidirectional 2.5 V 52

flash_sram_dq1 D1 Bidirectional 2.5 V 53

flash_sram_dq2 A8 Bidirectional 2.5 V 56

flash_sram_dq3 B8 Bidirectional 2.5 V 57

flash_sram_dq4 B7 Bidirectional 2.5 V 58

flash_sram_dq5

C5 Bidirectional 2.5 V 59

flash_sram_dq6 E8 Bidirectional 2.5 V 62

flash_sram_dq7 A4 Bidirectional 2.5 V 63

flash_sram_dq8 B4 Bidirectional 2.5 V 68

flash_sram_dq9 E7 Bidirectional 2.5 V 69

flash_sram_dq10 A3 Bidirectional 2.5 V 72

flash_sram_dq11 B3 Bidirectional 2.5 V 73

flash_sram_dq12 D5 Bidirectional 2.5 V 74

flash_sram_dq13 B5 Bidirectional 2.5 V 75

flash_sram_dq14 A5 Bidirectional 2.5 V 78

flash_sram_dq15 B6 Bidirectional 2.5 V 79

flash_sram_dq16 C16 Bidirectional 2.5 V 2

flash_sram_dq17 D12 Bidirectional 2.5 V 3

flash_sram_dq18 E11 Bidirectional 2.5 V 6

flash_sram_dq19 D2 Bidirectional 2.5 V 7

flash_sram_dq20 E13 Bidirectional 2.5 V8

flash_sram_dq21 E14 Bidirectional 2.5 V 9

flash_sram_dq22 A17 Bidirectional 2.5 V 12

flash_sram_dq23 D16 Bidirectional 2.5 V 13

flash_sram_dq24 C12 Bidirectional 2.5 V 18

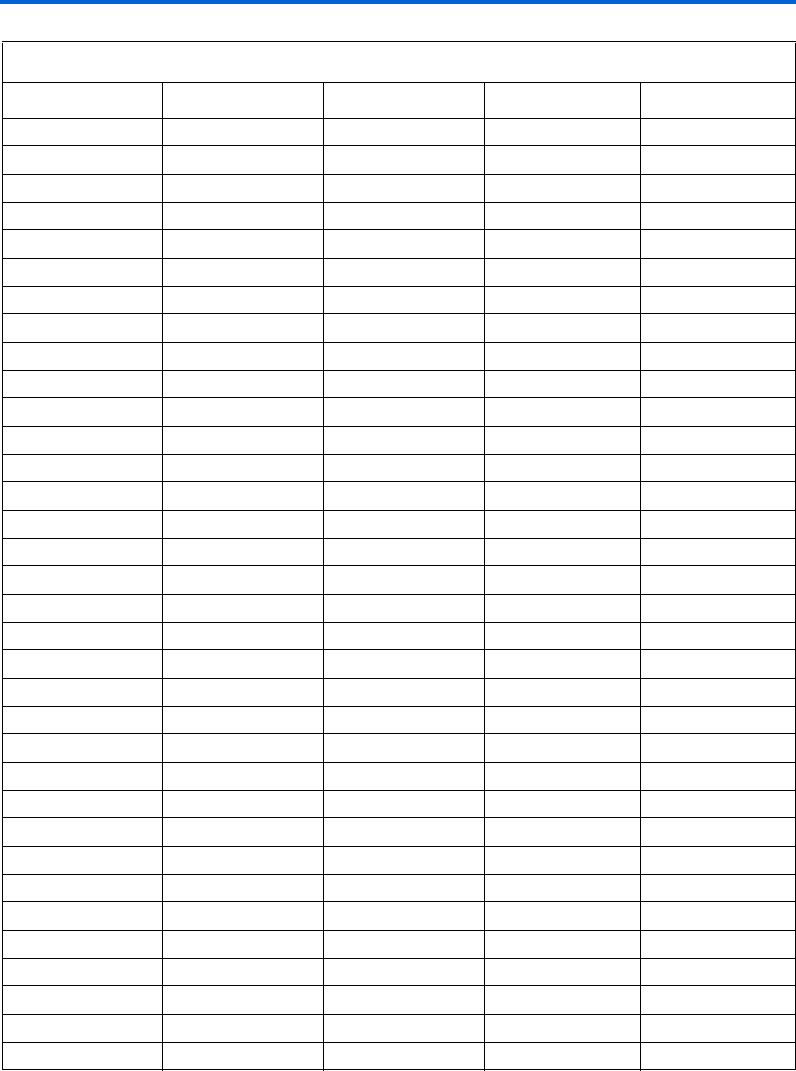

Table 2–16. SSRAM Pinout (Part 2 of 3)

Signal Name FPGA Pin Direction Type U5 (SSRAM) Pin