7

IDT70V631S

High-Speed 3.3V 256K x 18 Asynchronous Dual-Port Static RAM Industrial and Commercial Temperature Ranges

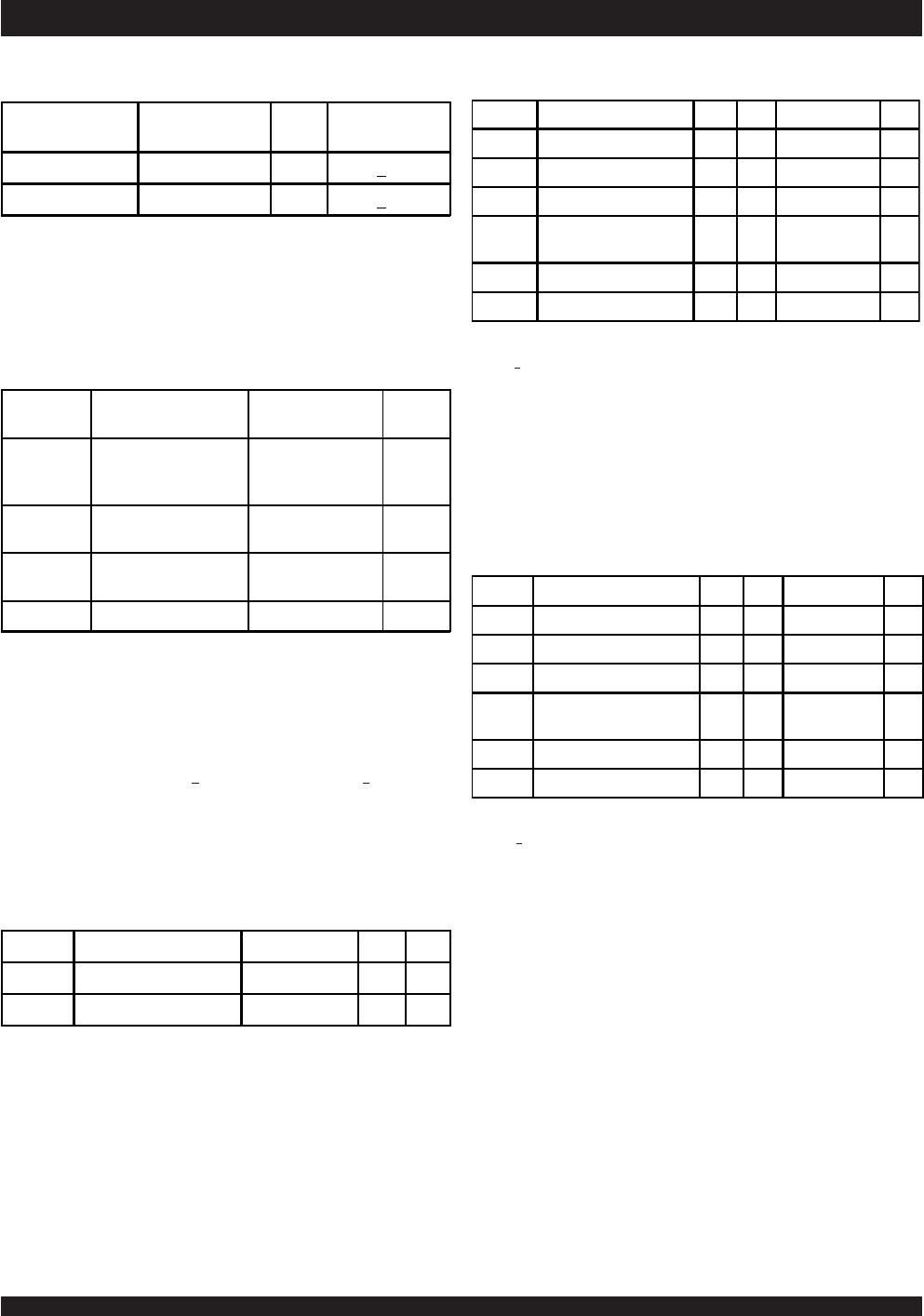

Recommended Operating

Temperature and Supply Voltage

(1)

Recommended DC Operating

Conditions with V

DDQ at 2.5V

Absolute Maximum Ratings

(1)

NOTES:

1. V

IL > -1.5V for pulse width less than 10 ns.

2. V

TERM must not exceed VDDQ + 100mV.

3. To select operation at 2.5V levels on the I/Os and controls of a given port, the

OPT pin for that port must be set to V

IL (0V), and VDDQX for that port must be supplied

as indicated above.

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may

cause permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated

in the operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect reliability.

2. V

TERM must not exceed VDD + 150mV for more than 25% of the cycle time or

4ns maximum, and is limited to

< 20mA for the period of VTERM > VDD + 150mV.

NOTE:

1. This is the parameter T

A. This is the "instant on" case temperature.

Recommended DC Operating

Conditions with V

DDQ at 3.3V

NOTES:

1. V

IL > -1.5V for pulse width less than 10 ns.

2. V

TERM must not exceed VDDQ + 150mV.

3. To select operation at 3.3V levels on the I/Os and controls of a given port, the

OPT pin for that port must be set to V

IH (3.3V), and VDDQX for that port must be

supplied as indicated above.

Grade

Ambient

Temperature GND V

DD

Commercial 0

O

C to +70

O

C0V3.3V

+

150mV

Industrial -40

O

C to +85

O

C0V3.3V

+

150mV

5622 tbl 04

Symbol Rating Commercial

& Industrial

Unit

V

TE R M

(2)

Terminal Voltage

with Respect to

GND

-0.5 to +4.6 V

T

BIAS

Tem p e r at ur e

Under Bias

-55 to +125

o

C

T

STG

Storage

Tem p e r at ur e

-65 to +150

o

C

I

OUT

DC Output Current 50 mA

5622 tbl 05

Symbol Parameter Min. Typ. Max. Unit

V

DD

Core Supply Voltage 3.15 3.3 3.45 V

V

DDQ

I/O Supply Voltage

(3)

2.4 2.5 2.6 V

V

SS

Ground 0 0 0 V

V

IH

Input High Voltage

(3 )

(Address & Control Inputs)

1.7

____

V

DDQ

+ 100mV

(2 )

V

V

IH

Input High Voltage - I/O

(3 )

1.7

____

V

DDQ

+ 100mV

(2 )

V

V

IL

Input Low Voltage -0.5

(1 )

____

0.7 V

5622 tbl 06

Symbol Parameter Min. Typ. Max. Unit

V

DD

Core Supply Voltage 3.15 3.3 3.45 V

V

DDQ

I/O Supply Voltage

(3)

3.15 3.3 3.45 V

V

SS

Ground 0 0 0 V

V

IH

Input High Voltage

(Address & Control Inputs)

(3)

2.0

____

V

DDQ

+ 150mV

(2)

V

V

IH

Input High Voltage - I/O

(3)

2.0

____

V

DDQ

+ 150mV

(2)

V

V

IL

Input Low Voltage -0.3

(1)

____

0.8 V

5622 tbl 07

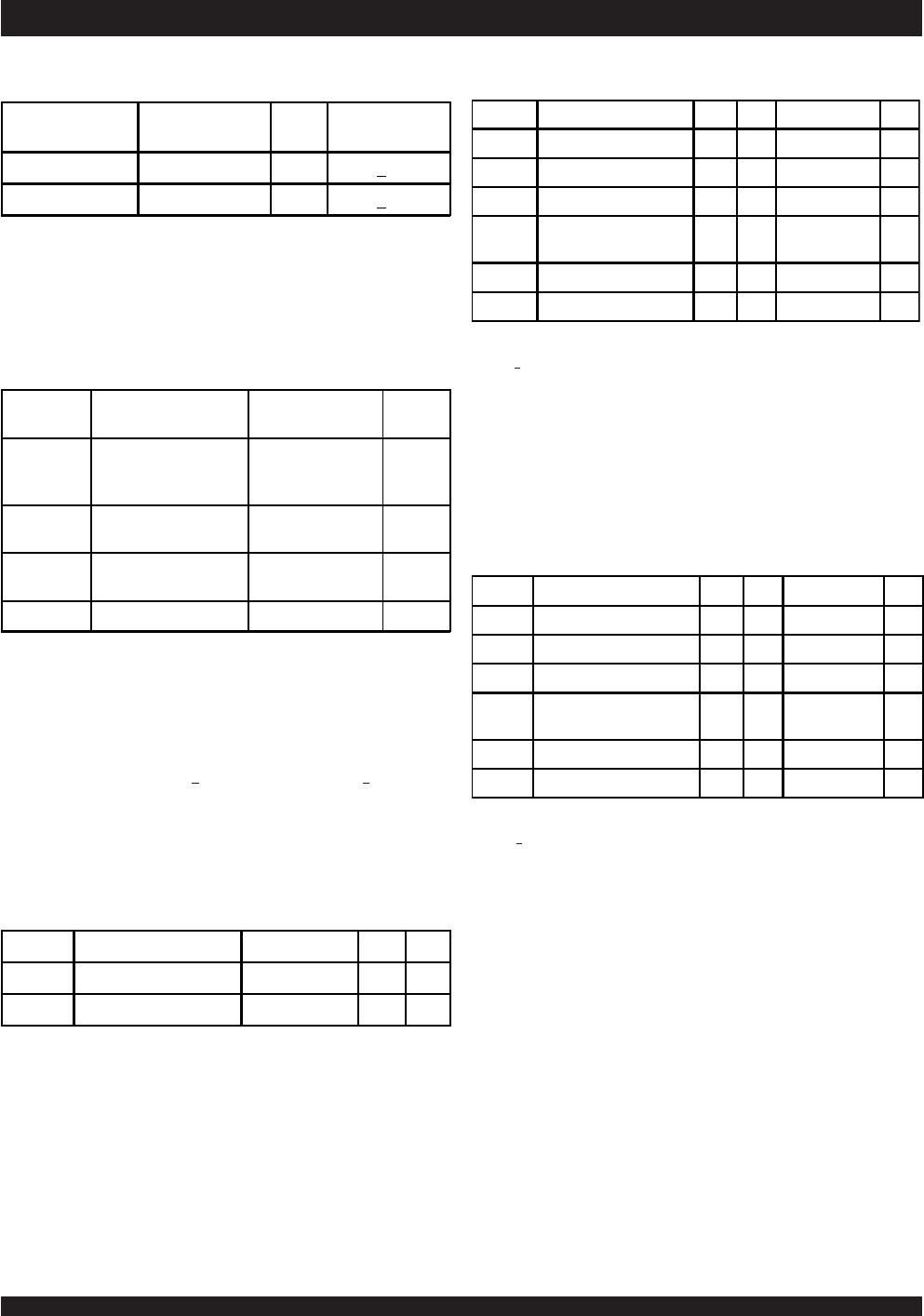

NOTES:

1. These parameters are determined by device characterization, but are not

production tested.

2. 3dV references the interpolated capacitance when the input and output switch

from 0V to 3V or from 3V to 0V.

3. C

OUT also references CI/O.

Capacitance

(1)

(TA = +25°C, F = 1.0MHZ) TQFP ONLY

Symbol Parameter Conditions

(2 )

Max. Unit

C

IN

Input Capacitance V

IN

= 3dV 8 pF

C

OUT

(3)

Output Capacitance V

OUT

= 3dV 10.5 pF

5622 tbl 08