32MB, 64MB, 128MB (x64, SR)

144-PIN SDRAM SODIMM

09005aef80748a77 Micron Technology, Inc., reserves the right to change products or specifications without notice.

SD4C4_8_16X64HG.fm - Rev. C 6/04 EN

12 ©2004 Micron Technology, Inc. All rights reserved.

Absolute Maximum Ratings

Stresses greater than those listed may cause perma-

nent damage to the device. This is a stress rating only,

and functional operation of the device at these or any

other conditions above those indicated in the opera-

tional sections of this specification is not implied.

Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

Voltage on V

DD Supply

Relative to Vss . . . . . . . . . . . . . . . . . . . .-1V to +4.6V

Voltage on Inputs, NC or I/O Pins

Relative to Vss . . . . . . . . . . . . . . . . . . . .-1V to +4.6V

Operating Temperature

T

OPR

(Commercial - ambient) . . . . . 0°C to + 65°C

T

OPR

(Industrial - ambient). . . . . . --40°C to +85°C

Storage Temperature (plastic) . . . . . .-55°C to +150°C

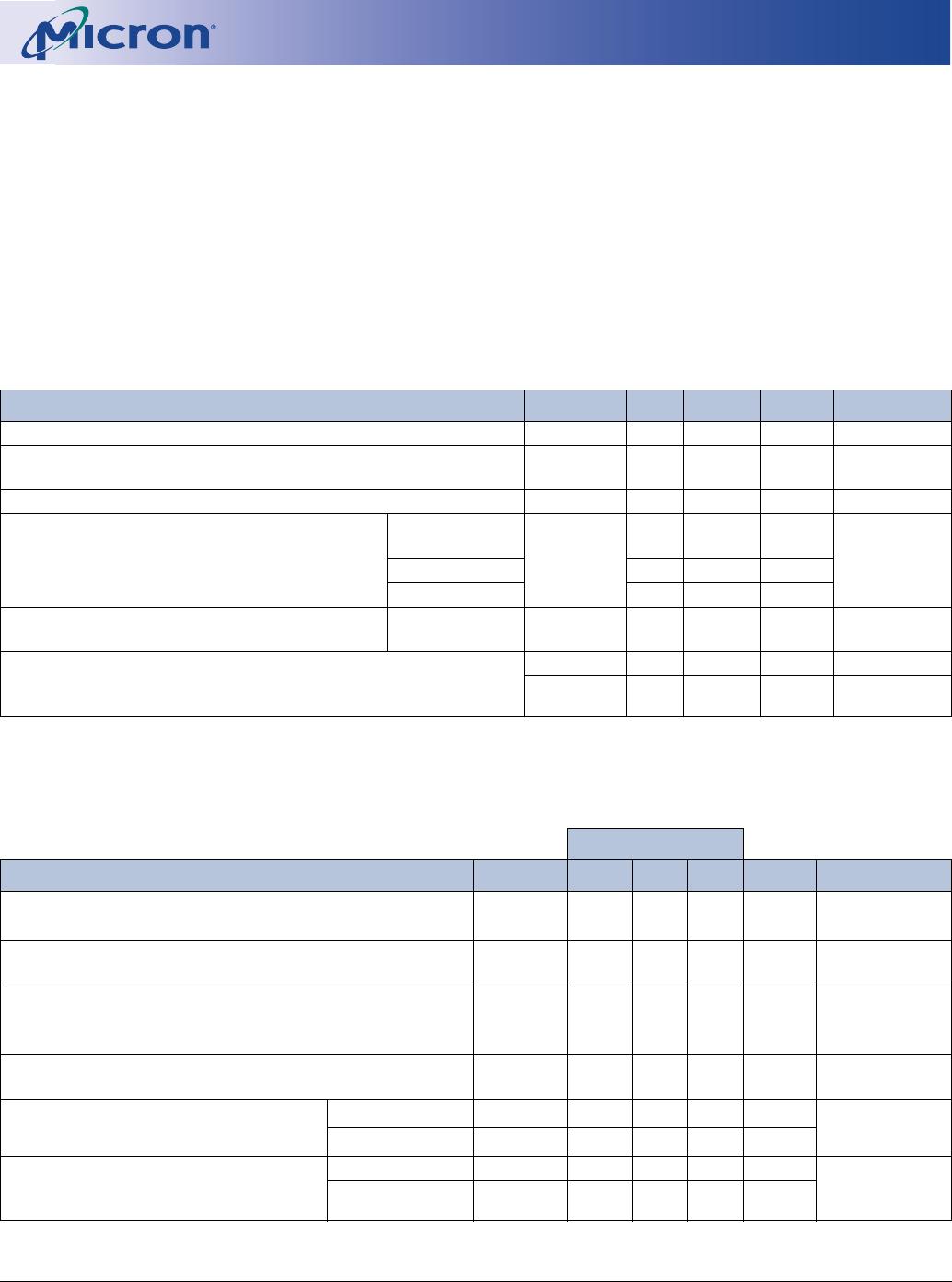

Table 9: DC Electrical Characteristics and Operating Conditions

Notes: 1, 5, 6; notes appear on page 16; VDD, VDDQ = +3.3V ±0.3V

PARAMETER/CONDITION SYMBOL MIN MAX UNITS NOTES

SUPPLY VOLTAGE

V

DD, VDDQ3 3.6 V

INPUT HIGH VOLTAGE: Logic 1; All inputs

V

IH 2VDD +

0.3

V22

INPUT LOW VOLTAGE: Logic 0; All inputs

V

IL -0.3 0.8 V 22

INPUT LEAKAGE CURRENT:

Any input 0V ≤ VIN ≤ VDD

(All other pins not under test = 0V)

Command and

Address Inputs

II

-20 20 µA

33

CK, S#

-20 20 µA

DQMB

-5 5 µA

OUTPUT LEAKAGE CURRENT: DQ pins are

disabled; 0V ≤ V

OUT ≤ VDDQ

DQ

I

OZ

-5 5 µA

33

OUTPUT LEVELS:

Output High Voltage (I

OUT = -4mA)

Output Low Voltage (I

OUT = 4mA)

V

OH 2.4 – V

VOL –0.4 V

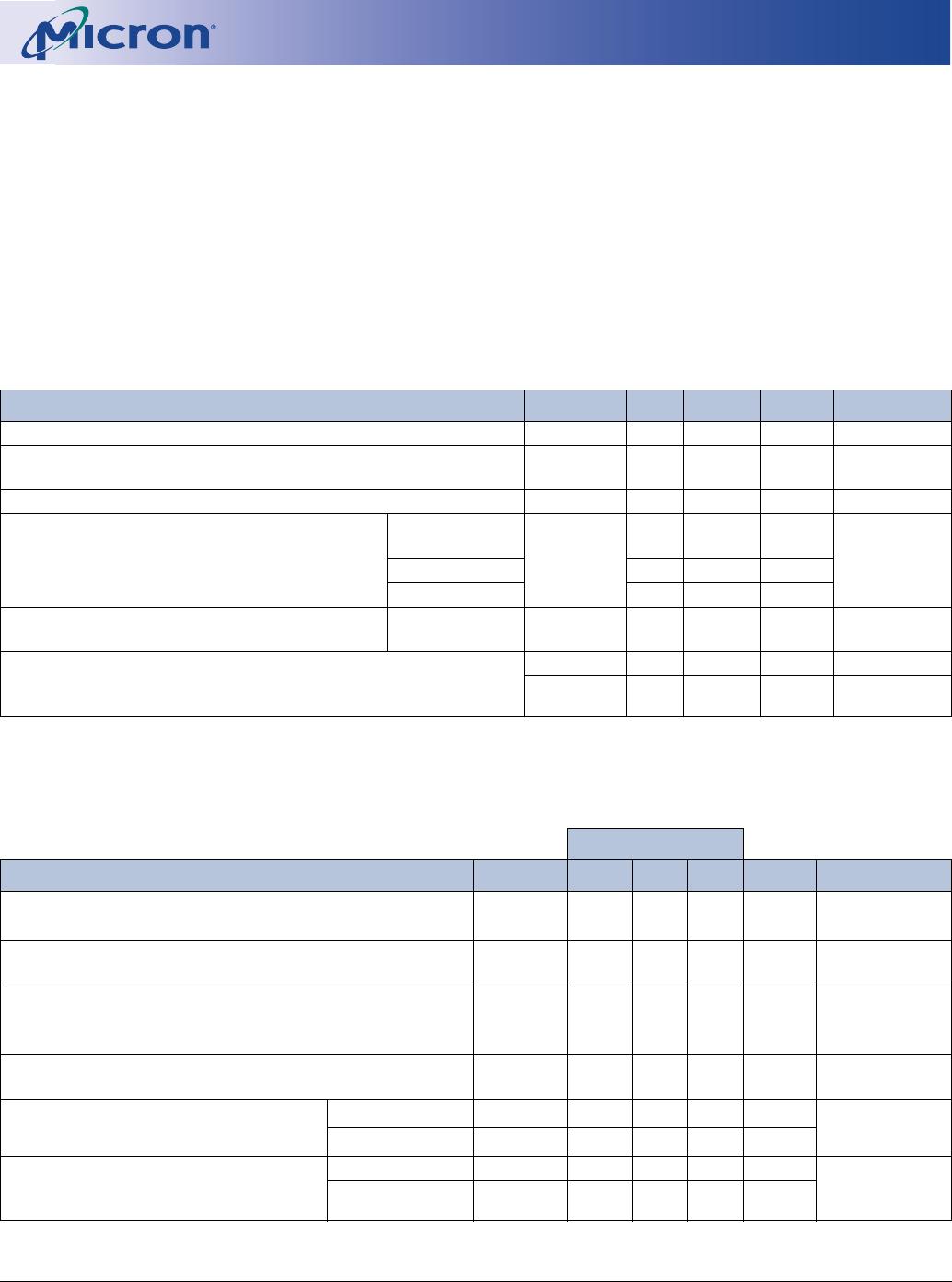

Table 10: IDD Specifications and Conditions – 32MB

Notes: 1, 5, 6, 11, 13; notes appear on page 16; VDD, VDDQ = +3.3V ±0.3V

MAX

PARAMETER/CONDITION SYMBOL -13E -133 -10E UNITS NOTES

OPERATING CURRENT: Active Mode; Burst = 2; READ or

WRITE;

t

RC =

t

RC (MIN)

I

DD1 500 460 380 mA 3, 18, 19, 29

STANDBY CURRENT: Power-Down Mode; All device device

banks idle; CKE = LOW

I

DD2 888mA 29

STANDBY CURRENT: Active Mode; CKE = HIGH; CS# = HIGH;

All device banks active after

t

RCD met; No accesses in

progress

I

DD3 180 180 140 mA 3, 12, 19, 29

OPERATING CURRENT: Burst Mode; Continuous burst; READ

or WRITE; All device banks active

I

DD4 600 560 480 mA 3, 18, 19, 29

AUTO REFRESH CURRENT

t

RFC =

t

RFC (MIN)

I

DD5 920 840 760 mA 3, 12, 18,

19, 29,30

CKE = HIGH; S# = HIGH

t

RFC = 15.625µs

I

DD6 12 12 12 mA

SELF REFRESH CURRENT: CKE ≤ 0.2V

(Low power not available with industrial

temperature option)

Standard I

DD7 444mA 3

Low Power (L) I

DD7 222mA