LTC5598

13

5598f

Table 7. RF Output Impedance vs Frequency for EN = High

FREQUENCY

(MHz)

RF OUTPUT

IMPEDANCE

REFLECTION COEFFICIENT

MAG ANGLE

0.1 59.0 – j0.6 0.083 –3.6

1 58.5 – j2.1 0.081 –12.7

2 57.3 – j3.5 0.076 –23.6

4 54.6 – j4.5 0.061 –41.6

8 51.9 – j3.6 0.040 –60.8

16 50.5 – j2.1 0.022 –74.8

30 50.2 – j1.1 0.011 –80

60 50 – j0.5 0.005 –86.5

100 50 – j0.2 0.002 –84.9

200 49.7 + j0 0.003 177.4

400 48.9 + j0.3 0.011 162

800 46.1 + j0.4 0.041 173.3

1000 44.5 + j0.2 0.058 178

1250 42.8 + j0 0.077 –179.7

1500 41.2 – j0.1 0.097 –179.4

1800 39.9 + j0.4 0.113 177.4

The RF port output impedance for EN = Low is given in Table

8. It is roughly equivalent to a 1.3pF capacitor to ground.

Table 8. RF Output Impedance vs Frequency for EN = Low

FREQUENCY

(MHz)

LO INPUT

IMPEDANCE

REFLECTION COEFFICIENT

MAG ANGLE

100 82.3 – j1223 0.995 –4.6

200 51.1 – j618 0.987 –9.2

400 35.3 – j310 0.965 –18.1

800 24.4 – j148 0.906 –36.6

1000 20.4 – j114 0.878 –46.4

1250 17 – j87 0.847 –58.4

1500 14.7 – j68 0.818 –70.7

1800 13.1 – j54 0.785 –84.3

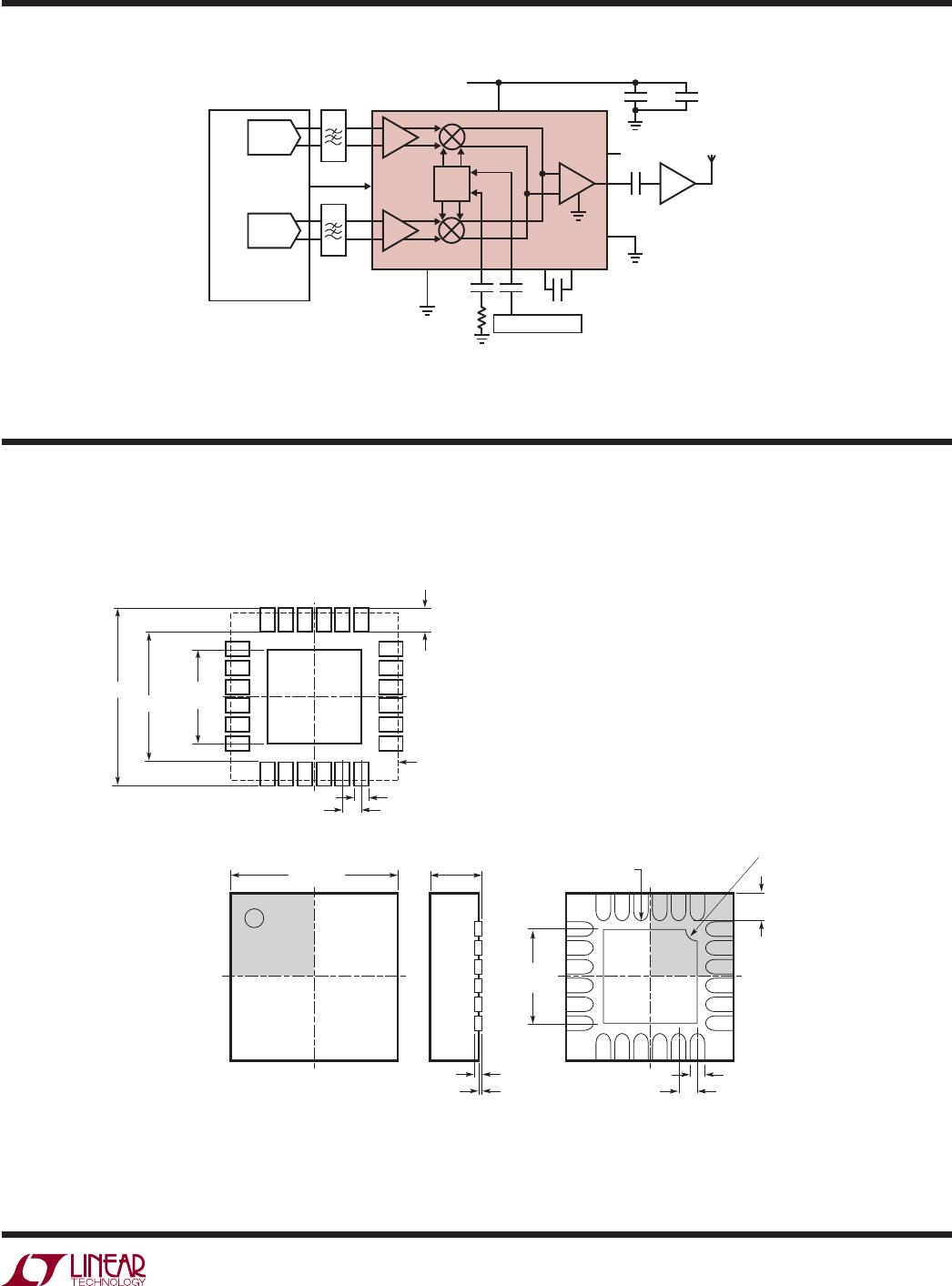

In Figure 7 the simplifi ed circuit schematic of the RF

output buffer is drawn. A plot of the RF port return loss vs

frequency is drawn in Figure 8 for EN = High and Low.

Enable Interface

Figure 9 shows a simplifi ed schematic of the EN pin

interface. The voltage necessary to turn on the LTC5598

is 2V. To disable (shut down) the chip, the enable voltage

must be below 1V. If the EN pin is not connected, the chip

is enabled. This EN = High condition is assured by the 125k

on-chip pull-up resistor. It is important that the voltage at

the EN pin does not exceed V

CC

by more than 0.3V. Should

APPLICATIONS INFORMATION

RF

1k

1.8V

4.6V

48Ω

48Ω

1k

1V

2.8V

FROM

INTERNAL

MIXERS

INTERNAL

BIAS

5598 F07

V

CC2

Figure 7. Simplifi ed Circuit Schematic of the RF Output

FREQUENCY (MHz)

1

RETURN LOSS (dB)

–10

–30

–20

–40

100 1000

10

–60

–50

0

5598 F08

EN = LOW

EN = HIGH

C6 = 220nF, SEE FIGURE 10

Figure 8. RF Port Return Loss vs Frequency

EN

V

CC1

125k

50k

2V

3V

INTERNAL

ENABLE

CIRCUIT

5598 F09

Figure 9: EN Pin Interface