ZL30410 Data Sheet

7

Zarlink Semiconductor Inc.

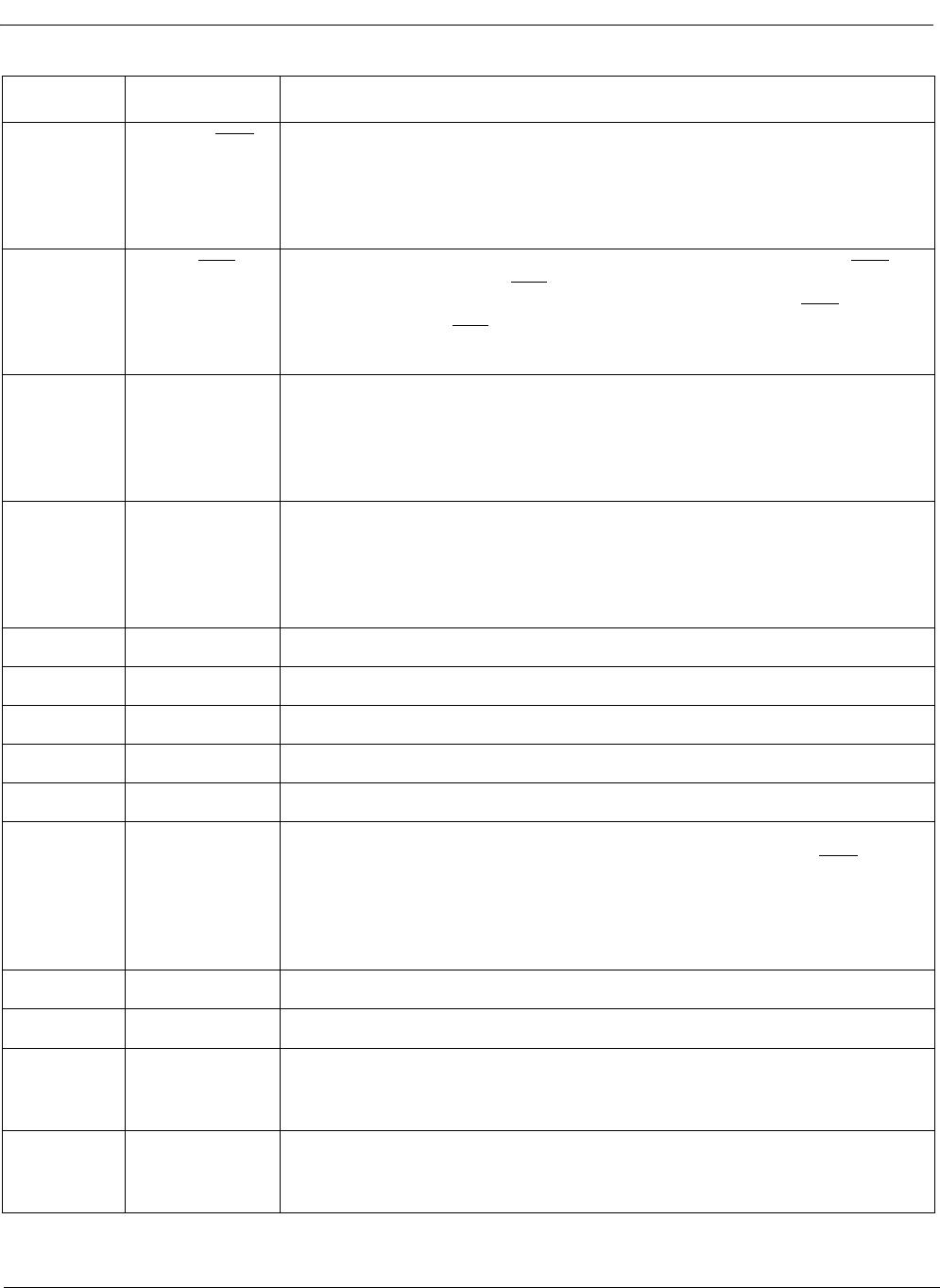

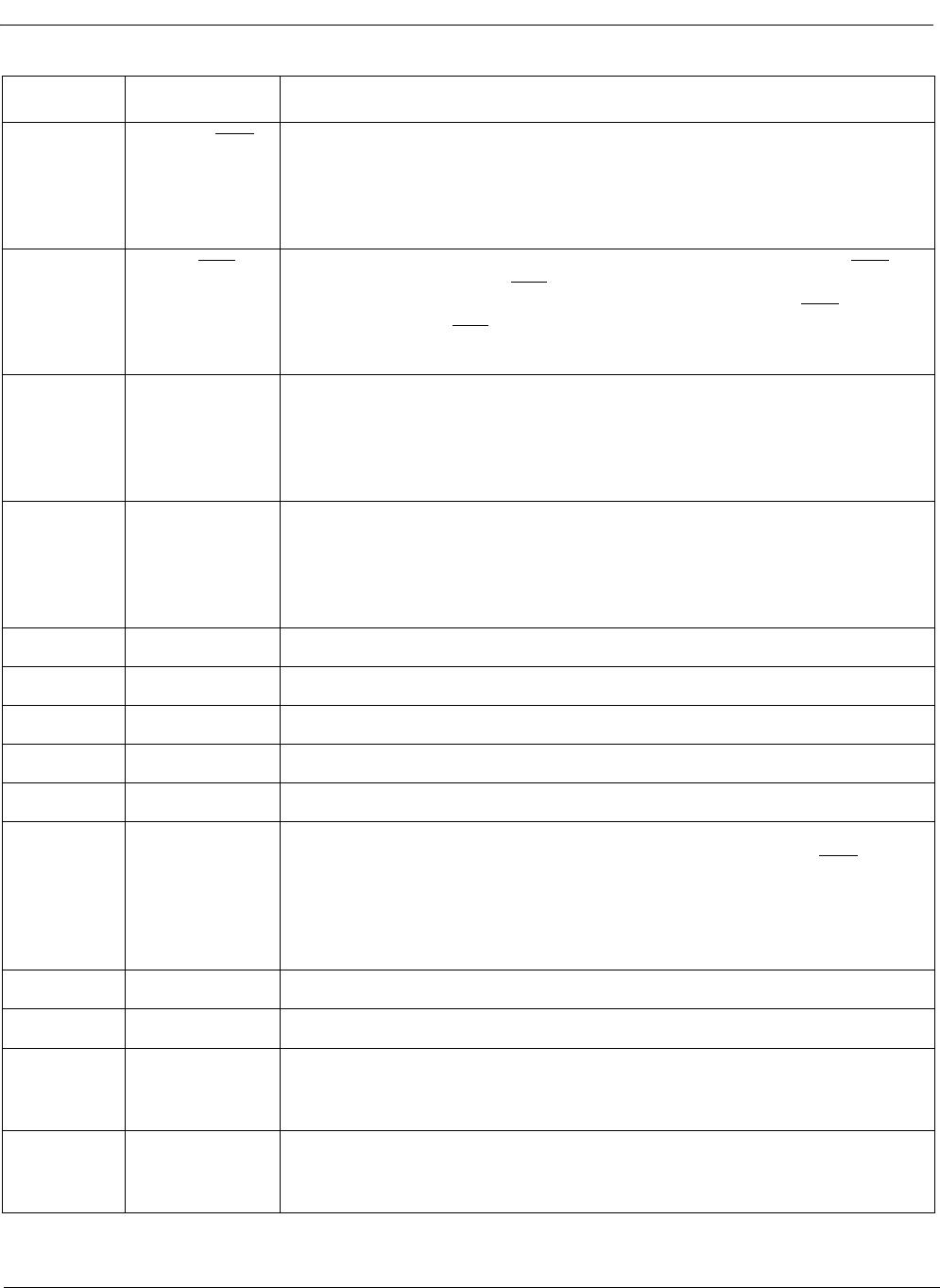

21 E3DS3/OC3 E3DS3 or OC3 Selection (Input). In Hardware Control, a logic low on this pin

enables the C155P/N outputs (pin 30 and pin 31) and sets the C34/C44 output

(pin 53) to provide C8 or C11 clocks. Logic high at this input disables the C155

clock outputs (high impedance) and sets C34/C44 output to provide C34 and

C44 clocks.

22 E3/DS3

E3 or DS3 Selection (Input). In Hardware Control, when the E3DS3/OC3 pin

is set high, logic low on E3/DS3

pin selects a 44.736 MHz clock on C34/C44

output and logic high selects 34.368 MHz clock. When E3DS3/OC3

pin is set

low, logic low on E3/DS3

pin selects 11.184 MHz clock on C34/C44 output and

logic high selects 8.592 MHz clock.

23 SEC Secondary Reference (Input). This input is used as a secondary reference

source for synchronization. The ZL30410 can synchronize to the falling edge

of the 8 kHz, 1.544 MHz or 2.048 MHz clocks and the rising edge of the

19.44 MHz clock. In Hardware Control, selection of the input reference is

based upon the RefSel control input. This pin is internally pulled up to VDD.

24 PRI Primary Reference (Input). This input is used as a primary reference source

for synchronization. The ZL30410 can synchronize to the falling edge of the

8 kHz, 1.544 MHz or 2.048 MHz clocks and the rising edge of the 19.44 MHz

clock. In Hardware Control, selection of the input reference is based upon the

RefSel control input. This pin is internally pulled up to VDD.

25 GND Ground

26 IC Internal Connection. Leave unconnected.

27 GND Ground

28 AVDD Positive Analog Power Supply. Connect this pin to VDD.

29 VDD Positive Power Supply.

30

31

C155N

C155P

Clock 155.52 MHz (LVDS output). Differential outputs for the 155.52 MHz

clock. These outputs are enabled by applying logic low to E3DS3/OC3

input or

they can be disabled by applying logic high. In the disabled state the LVDS

outputs are internally terminated with an integrated 100 Ω resistor (two 50Ω

resistors connected in series). The middle point of these resistors is internally

biased from a 1.25 V LVDS bias source.

32 GND Ground

33 NC No internal bonding Connection. Leave unconnected.

34 Tdo IEEE1149.1a Test Data Output (CMOS output). JTAG serial data is output on

this pin on the falling edge of Tclk clock. If not used, this pin should be left

unconnected.

35 Tms IEEE1149.1a Test Mode Selection (3.3 V input). JTAG signal that controls the

state transition on the TAP controller. This pin is internally pulled up to VDD. If

not used, this pin should be left unconnected.

Pin Description (continued)

Pin # Name Description