REV. B

–30–

AD7858/AD7858L

APPLICATION HINTS

Grounding and Layout

The analog and digital supplies to the AD7858/AD7858L are

independent and separately pinned out to minimize coupling

between the analog and digital sections of the device. The part

has very good immunity to noise on the power supplies as can

be seen by the PSRR vs. Frequency graph. However, care

should still be taken with regard to grounding and layout.

The printed circuit board that houses the AD7858/AD7858L

should be designed such that the analog and digital sections are

separated and confined to certain areas of the board. This facili-

tates the use of ground planes that can be separated easily. A

minimum etch technique is generally best for ground planes as

it gives the best shielding. Digital and analog ground planes

should only be joined in one place. If the AD7858/AD7858L is

the only device requiring an AGND to DGND connection,

then the ground planes should be connected at the AGND and

DGND pins of the AD7858/AD7858L. If the AD7858/

AD7858L is in a system where multiple devices require AGND

to DGND connections, the connection should still be made at

one point only, a star ground point which should be established

as close as possible to the AD7858/AD7858L.

Avoid running digital lines under the device as these will couple

noise onto the die. The analog ground plane should be allowed

to run under the AD7858/AD7858L to avoid noise coupling.

The power supply lines to the AD7858/AD7858L should use as

large a trace as possible to provide low impedance paths and

reduce the effects of glitches on the power supply line. Fast

switching signals like clocks should be shielded with digital

ground to avoid radiating noise to other sections of the board,

and clock signals should never be run near the analog inputs.

Avoid crossover of digital and analog signals. Traces on oppo-

site sides of the board should run at right angles to each other.

This will reduce the effects of feedthrough through the board. A

microstrip technique is by far the best but is not always possible

with a double-sided board. In this technique, the component

side of the board is dedicated to ground planes while signals are

placed on the solder side.

Good decoupling is also important. All analog supplies should

be decoupled with 10 µF tantalum in parallel with 0.1 µF ca-

pacitors to AGND. All digital supplies should have a 0.1 µF

disc ceramic capacitor to AGND. To achieve the best from

these decoupling components, they must be placed as close as

possible to the device, ideally right up against the device. In

systems where a common supply voltage is used to drive both

the AV

DD

and DV

DD

of the AD7858/AD7858L, it is recom-

mended that the system’s AV

DD

supply be used. In this case

there should be a 10 Ω resistor between the AV

DD

pin and

DV

DD

pin. This supply should have the recommended analog

supply decoupling capacitors between the AV

DD

pin of the

AD7858/AD7858L and AGND and the recommended digital

supply decoupling capacitor between the DV

DD

pin of the

AD7858/AD7858L and DGND.

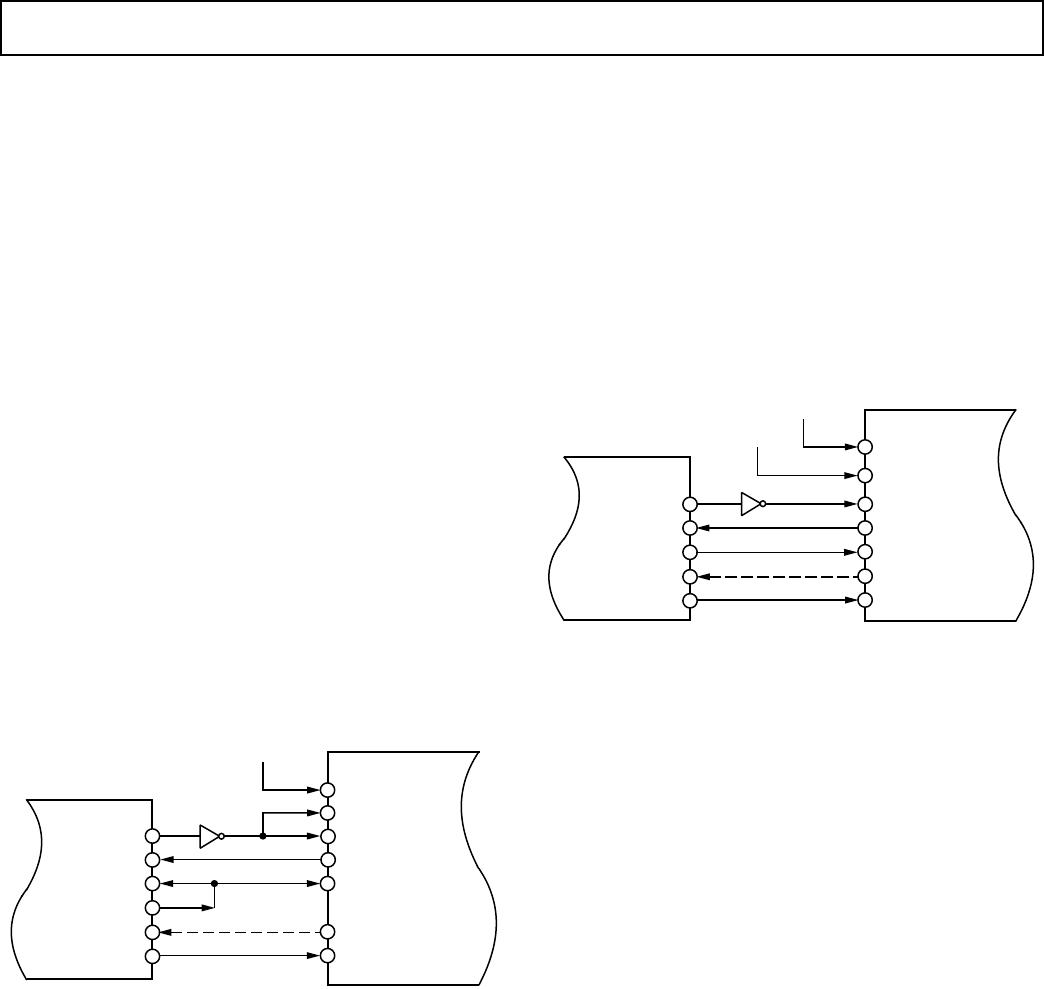

Evaluating the AD7858/AD7858L Performance

The recommended layout for the AD7858/AD7858L is out-

lined in the evaluation board for the AD7858/AD7858L. The

evaluation board package includes a fully assembled and tested

evaluation board, documentation, and software for controlling

the board from the PC via the EVAL-CONTROL BOARD.

The EVAL-CONTROL BOARD can be used in conjunction

with the AD7858/AD7858L Evaluation board, as well as many

other Analog Devices evaluation boards ending in the CB desig-

nator, to demonstrate/evaluate the ac and dc performance of the

AD7858/AD7858L.

The software allows the user to perform ac (fast Fourier trans-

form) and dc (histogram of codes) tests on the AD7858/

AD7858L. It also gives full access to all the AD7858/AD7858L

on-chip registers allowing for various calibration and power-

down options to be programmed.

AD785x Family

All parts are 12 bits, 200 kSPS, 3.0 V to 5.5 V.

AD7853 – Single Channel Serial

AD7854 – Single Channel Parallel

AD7858 – Eight Channel Serial

AD7859 – Eight Channel Parallel