LTC2450-1

10

24501fc

APPLICATIONS INFORMATION

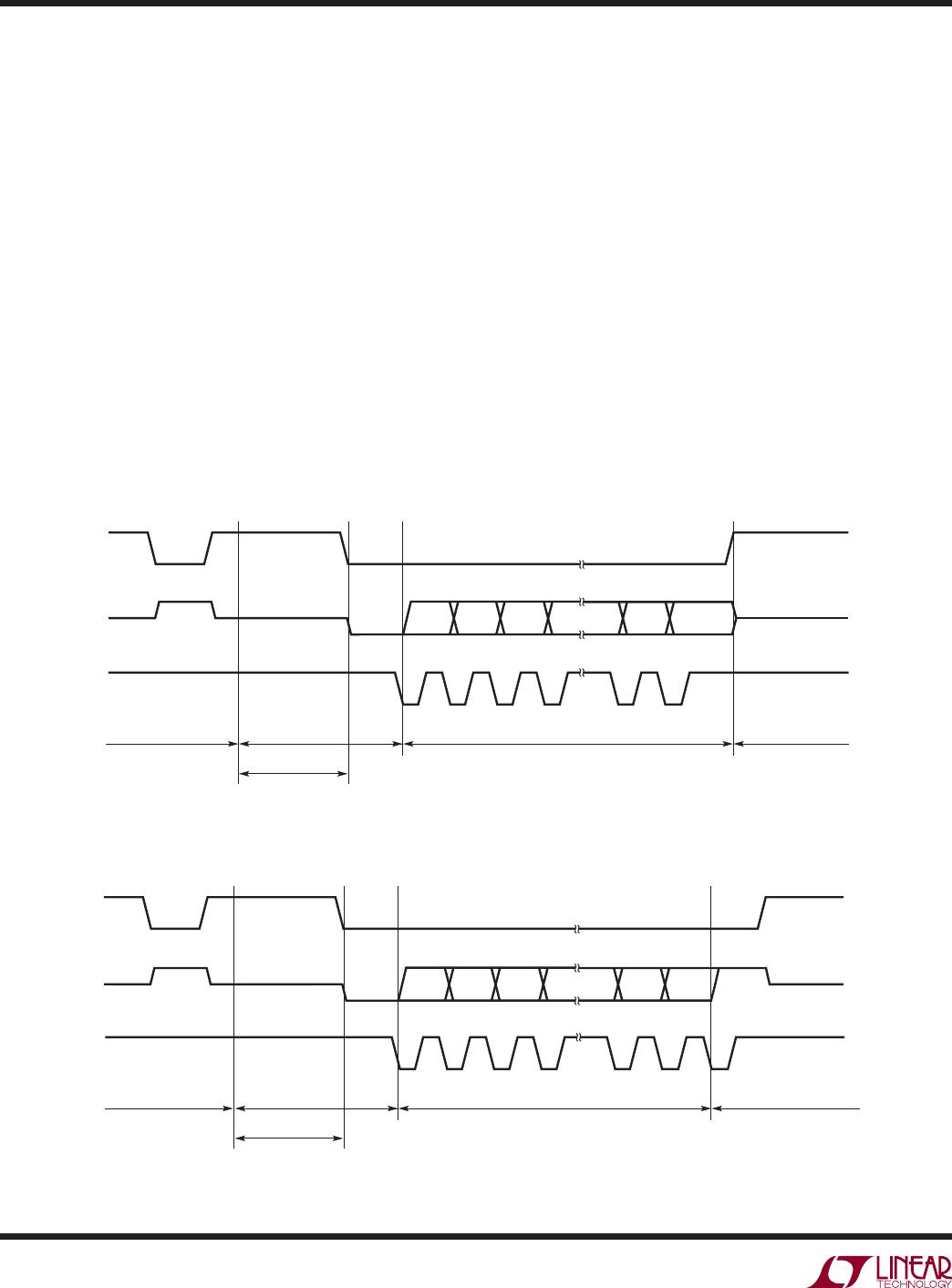

Serial Clock Idle-High (CPOL = 1) Examples

In Figure 5, following a conversion cycle the LTC2450-1

automatically enters the low power sleep mode. The user

can monitor the conversion status at convenient intervals

using CS and SDO.

CS is pulled LOW while SCK is HIGH to test whether or not

the chip is in the CONVERT state. While in the CONVERT

state, SDO is HIGH while CS is LOW. In the SLEEP state,

SDO is LOW while CS is LOW. These tests are not required

operational steps but may be useful for some applications.

When the data is available, the user applies 16 clock cycles

to transfer the result. The CS rising edge is then used to

initiate a new conversion.

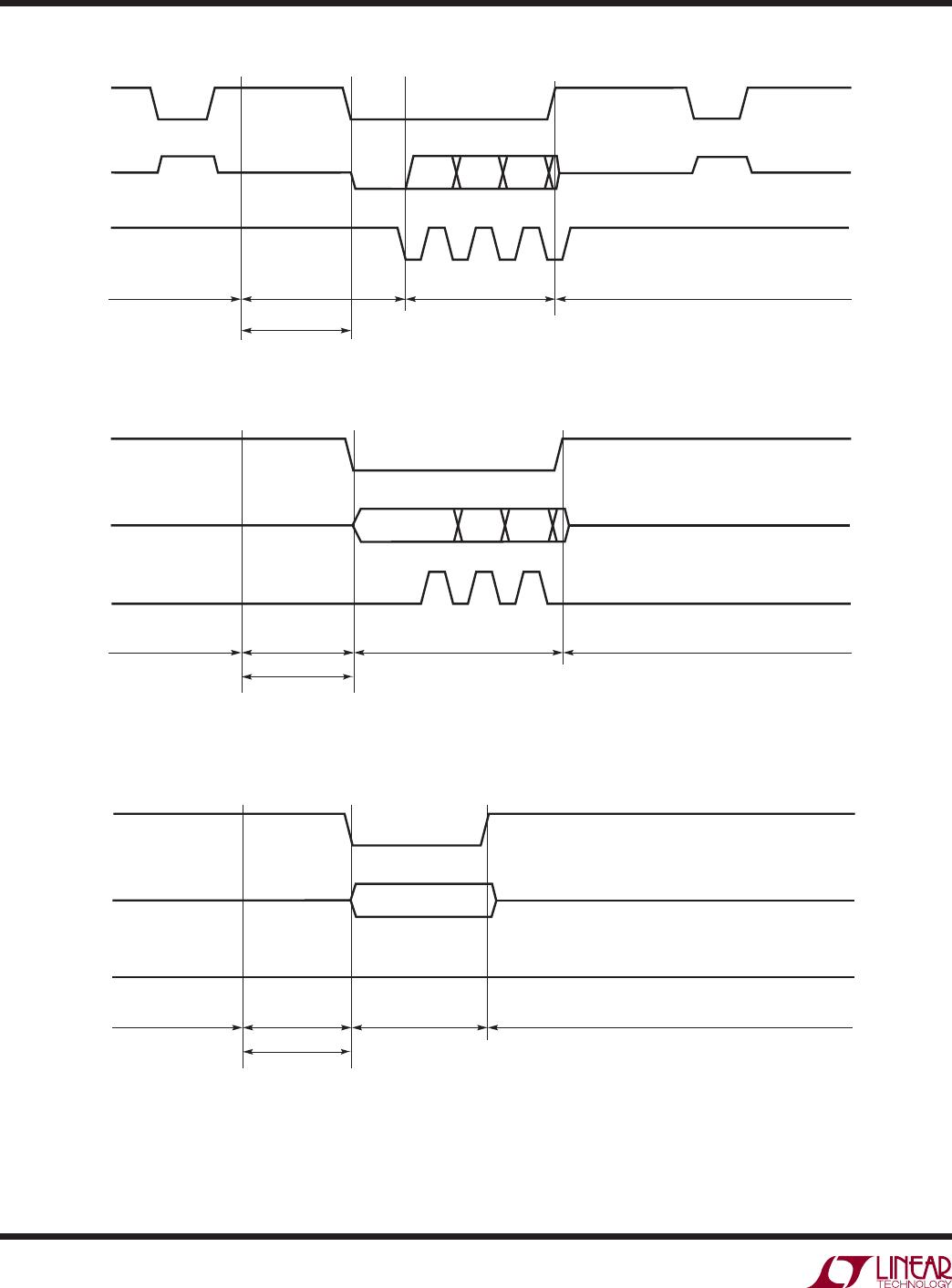

The operation example of Figure 6 is identical to that of

Figure 5, except the new conversion cycle is triggered by

the falling edge of the serial clock (SCK). A 17th clock

pulse is used to trigger a new conversion cycle.

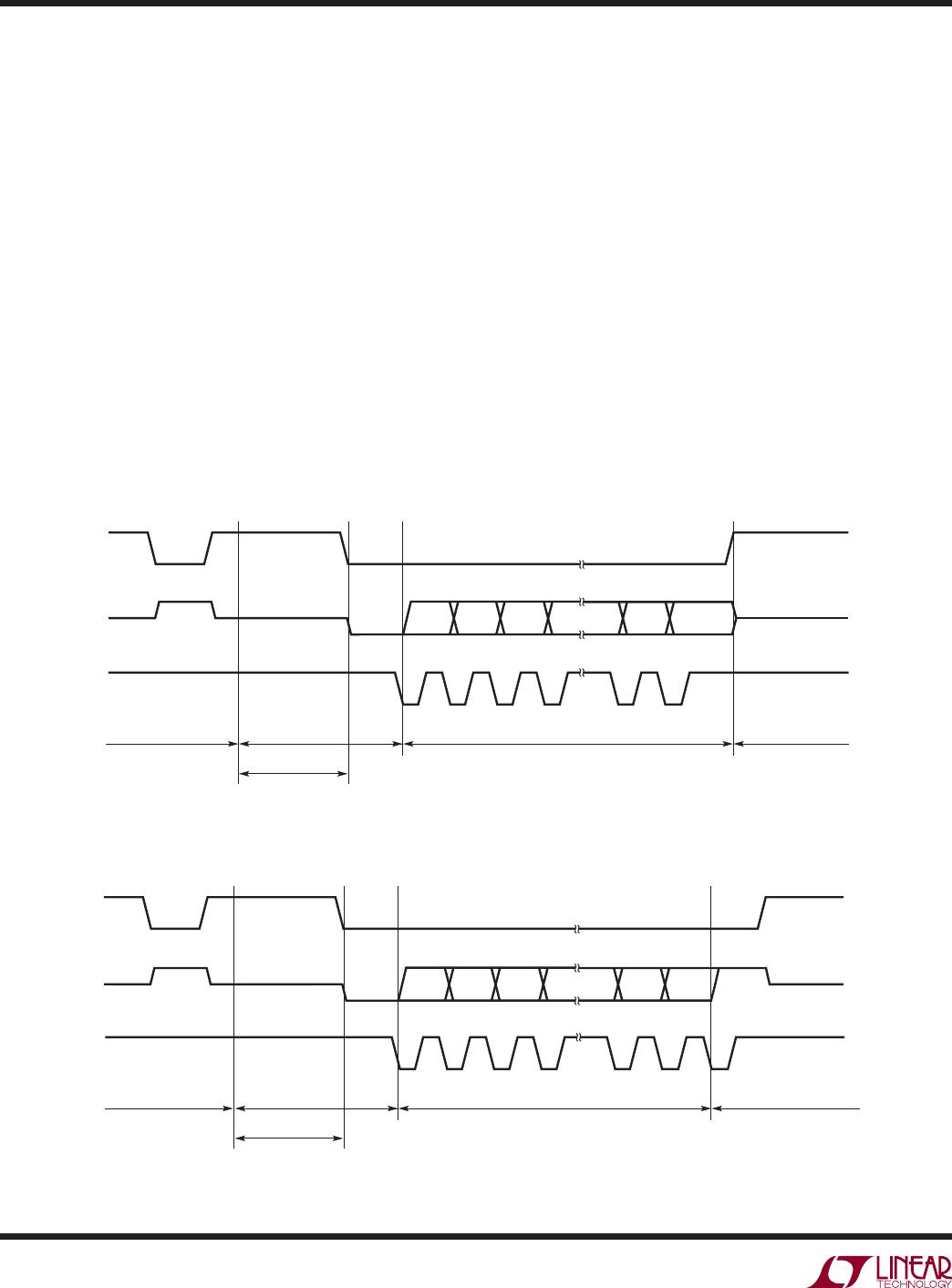

Serial Clock Idle-Low (CPOL = 0) Examples

In Figure 7, following a conversion cycle the LTC2450-1

automatically enters the low power sleep state. The user

determines data availability (and the end of conversion)

based upon external timing. The user then pulls CS low

(CS = ↓) and uses 16 clock cycles to transfer the result.

Following the 16th rising edge of the clock, CS is pulled high

(CS = ↑), which triggers a new conversion.

The timing diagram in Figure 8 is identical to that of Figure 7,

except in this case a new conversion is triggered by SCK.

The 16th SCK falling edge triggers a new conversion cycle

and the CS signal is subsequently pulled high.

Figure 5. Idle-High (CPOL = 1) Serial Clock Operation Example.

The Rising Edge of CS Starts a New Conversion

Figure 6. Idle-High (CPOL = 1) Clock Operation Example.

A 17th Clock Pulse is Used to Trigger a New Conversion Cycle

D

15

clk

1

clk

2

clk

3

clk

4

clk

15

clk

16

D

14

D

13

D

12

D

2

D

1

D

0

SD0

SCK

CONVERT CONVERTSLEEP

LOW I

CC

DATA OUTPUT

24501 F05

CS

D

15

D

14

D

13

D

12

D

2

D

1

D

0

SD0

clk

1

clk

2

clk

3

clk

4

clk

15

clk

16

clk

17

SCK

CONVERT CONVERTSLEEP

LOW I

CC

DATA OUTPUT

24501 F06

CS