AT17LV65A/128A/256A/512A/002A [DATASHEET]

Atmel-2322I-FPGA-AT17LV65A-128A-256A-512A-002A-Datasheet_102014

12

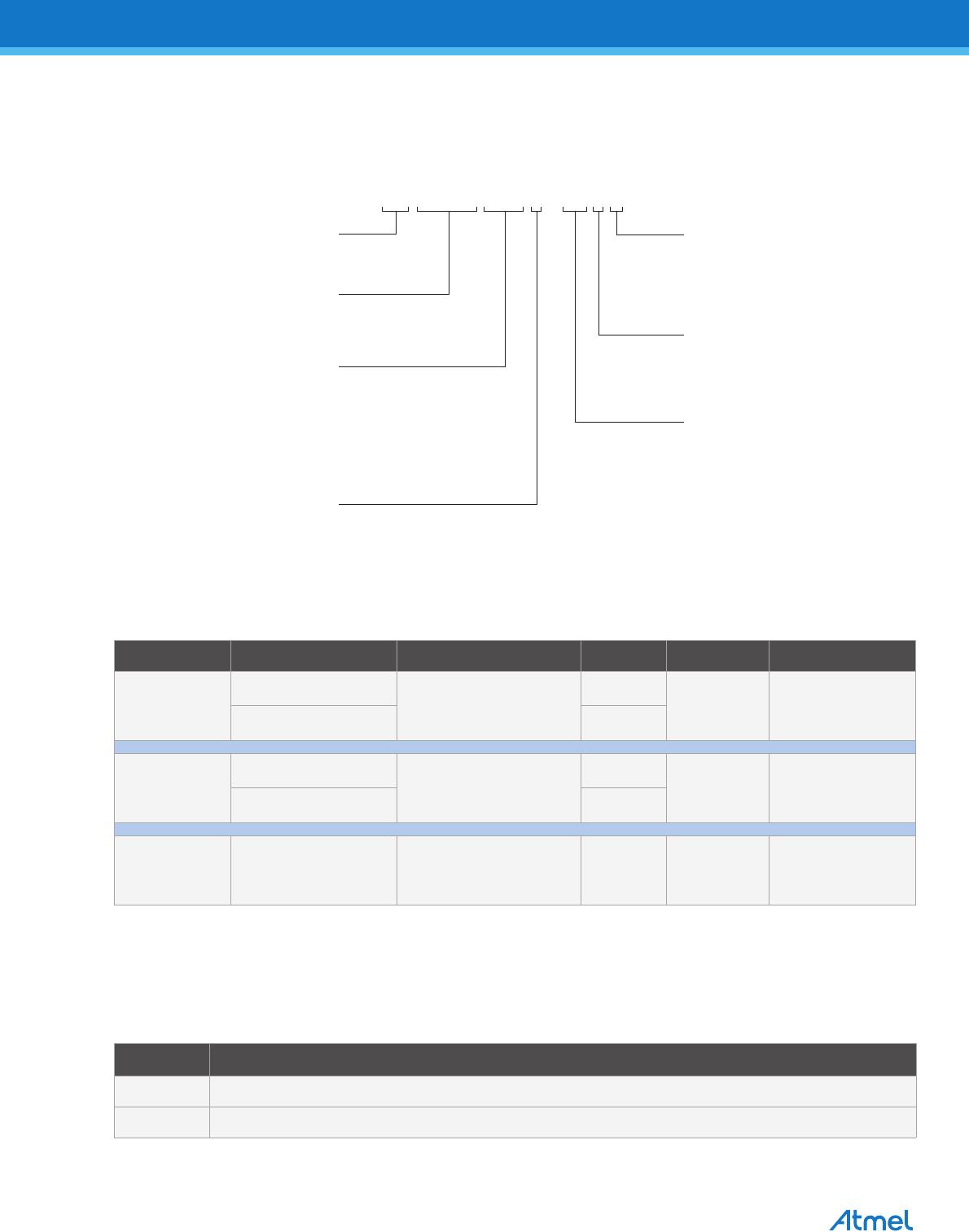

11. Ordering Information

11.1 Ordering Code Detail

11.2 Ordering Information

Notes: 1. Use 512-Kbit density parts to replace Altera EPC1441.

2. Use 1-Mbit density parts to replace Altera EPC1

3. Use 2-Mbit density parts to replace Altera EPC2.

4. The AT17LVxxxA do not support JTAG programming. They use a 2-wire serial interface for in-system

programming.

AT17LV512A-10PU

Atmel Designator

Product Family

Device Density

Special Pinouts

Product Variation

65 = 65 kilobit

128 = 128 kilobit

256 = 256 kilobit

512 = 512 kilobit

010 = 1 Mbit

002 = 2 Mbit

A = Altera

Blank = Xilinx/Atmel/Other

17LV = FPGA EEPROM

Configuration Memory

Package Device Grade

U = Green, Industrial

Temperature Range

(-40°C to +85°C)

10 = Default Value

Package Option

P = 8P3, 8-lead PDIP

J = 20J, 20-lead PLCC

Memory Size Atmel Ordering Code Lead Finish Package Voltage Operation Range

512-Kbit

(1)(4)

AT17LV512A-10JU

Sn

(Lead-free/Halogen-free)

20J

3.0V to 5.5V

Industrial

(-40C to 85C)

AT17LV512A-10PU 8P3

1-Mbit

(2)(4)

AT17LV010A-10JU

Sn

(Lead-free/Halogen-free)

20J

3.0V to 5.5V

Industrial

(-40C to 85C)

AT17LV010A-10PU 8P3

2-Mbit

(1)(4)

AT17LV002A-10JU

Sn

(Lead-free/Halogen-free)

20J 3.0V to 5.5V

Industrial

(-40C to 85C)

Package Type

8P3 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)

20J 20-lead, Plastic J-leaded Chip Carrier (PLCC)