5

AT17LV65A/128A/256A/512A/002A [DATASHEET]

Atmel-2322I-FPGA-AT17LV65A-128A-256A-512A-002A-Datasheet_102014

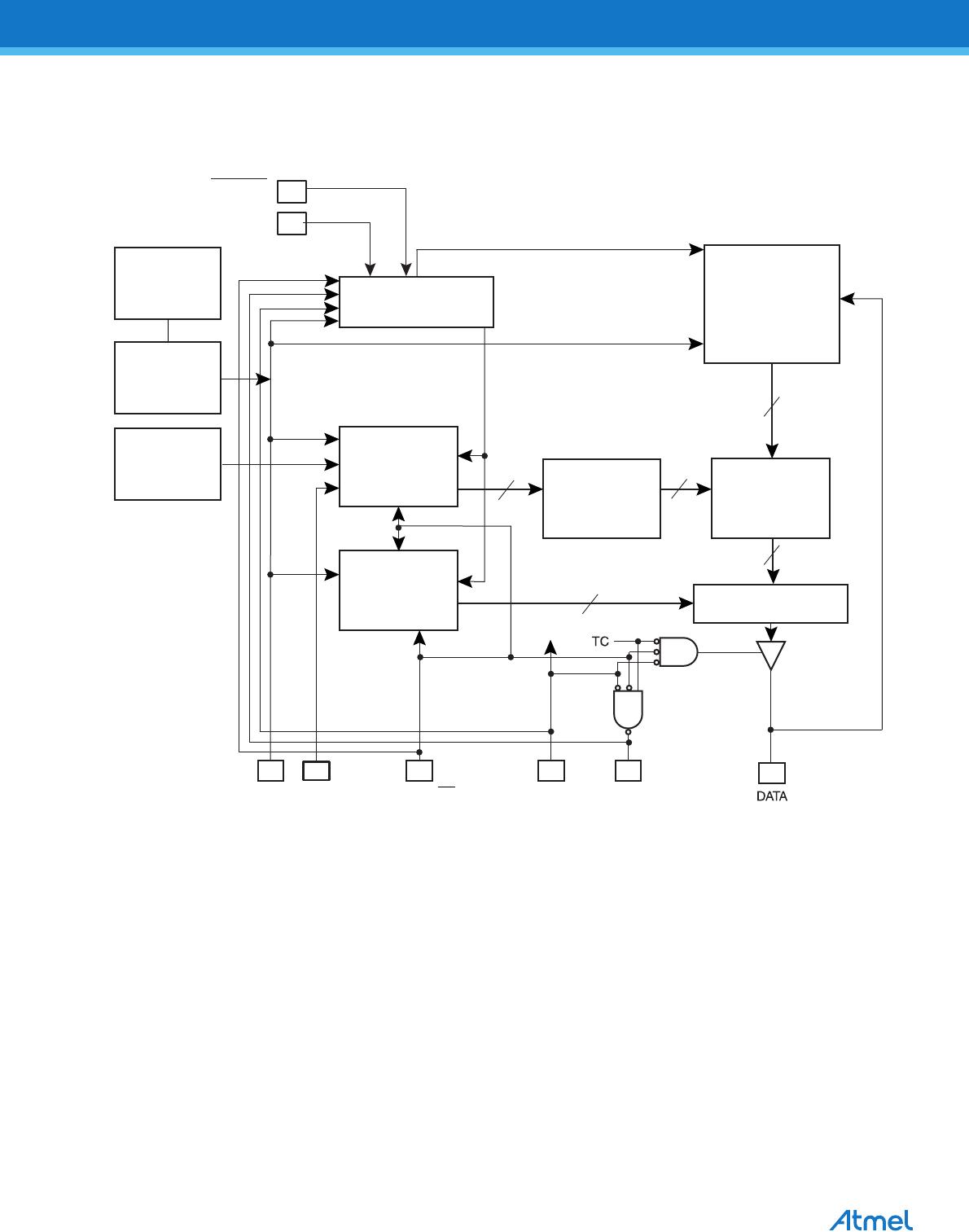

3. Device Description

The control signals for the configuration EEPROM (nCS, RESET/OE and DCLK) interface directly with the

FPGA device control signals. All FPGA devices can control the entire configuration process and retrieve data

from the configuration EEPROM without requiring an external controller.

The configuration EEPROM’s RESET/OE and nCS pins control the tri-state buffer on the DATA output pin and

enable the address counter and the oscillator. When RESET/OE is driven Low, the configuration EEPROM

resets its address counter and tri-states its DATA pin. The nCS pin also controls the output of the AT17LVxxxA

configurator. If nCS is held High after the RESET/OE pulse, the counter is disabled and the DATA output pin is

tri-stated. When nCS is driven subsequently Low, the counter and the DATA output pin are enabled. When

RESET/OE is driven Low again, the address counter is reset and the DATA output pin is tri-stated, regardless of

the state of the nCS.

When the configurator has driven out all of its data and nCASC is driven Low, the device tri-states the DATA pin

to avoid contention with other configurators. Upon power-up, the address counter is automatically reset.

This is the default setting for the device. Since almost all FPGAs use RESET Low and OE High, this document

will describe RESET/OE.

4. FPGA Master Serial Mode Summary

The I/O and logic functions of any SRAM-based FPGA are established by a configuration program. The

program is loaded either automatically upon power-up, or on command, depending on the state of the FPGA

mode pins. In Master mode, the FPGA automatically loads the configuration program from an external memory.

The AT17LVxxxA Serial Configuration EEPROM has been designed for compatibility with the Master Serial

mode.

This document discusses the Altera FLEX FPGA device interfaces.

5. Control of Configuration

Most connections between the FPGA device and the AT17LVxxxA Serial EEPROM are simple and self-

explanatory.

The DATA output of the AT17LVxxxA configurator drives DIN of the FPGA devices.

The master FPGA DCLK output or external clock source drives the DCLK input of the AT17LVxxxA

configurator.

The nCASC output of any AT17LVxxxA configurator drives the nCS input of the next configurator in a

cascaded chain of EEPROMs.

SER_EN must be connected to V

CC

(except during ISP).