ADMV1012 Data Sheet

Rev. A | Page 14 of 19

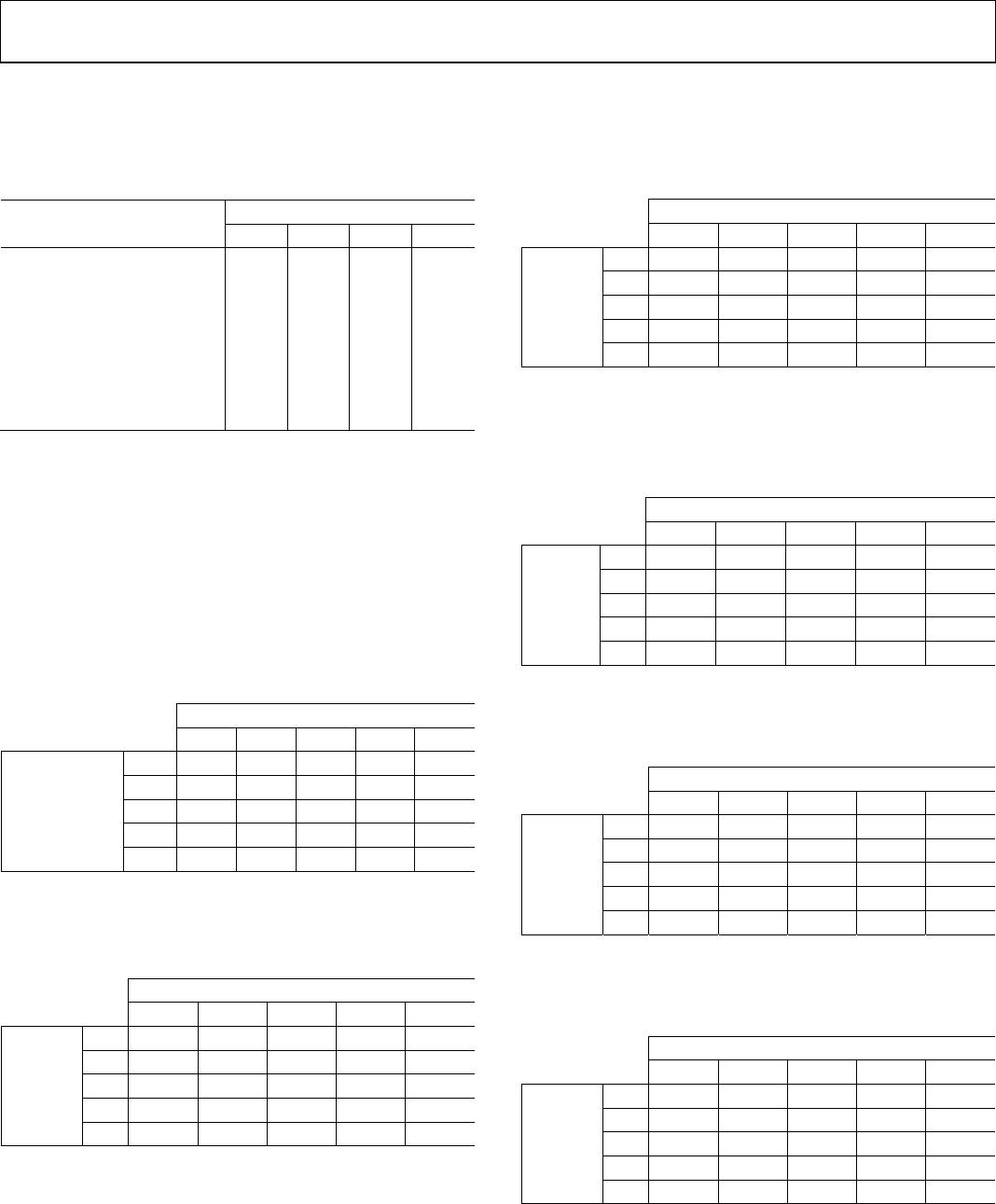

THEORY OF OPERATION

The ADMV1012 is a compact GaAs, MMIC, double sideband

(DSB) downconverter in a RoHS compliant package optimized

for both upper sideband and lower sideband point to point

microwave radio applications operating in the 17.5 GHz to

24 GHz input frequency range. The ADMV1012 supports

LO input frequencies of 7 GHz to 13.5 GHz and IF output

frequencies of 2.5 GHz to 3.5 GHz.

The ADMV1012 uses a RF LNA followed by an I/Q double

balanced mixer, where a driver amplifier drives the LO (see

Figure 1). This combination of design, process, and packaging

technology allows the functions of these subsystems to be

integrated into a single die, using mature packaging and

interconnection technologies to provide a high performance,

low cost design with excellent electrical, mechanical, and

thermal properties. In addition, the need for external

components is minimized, optimizing cost and size.

LO DRIVER AMPLIFIER

The LO driver amplifier takes a single LO input and doubles the

frequency and amplifies it to the desired LO signal level for the

mixer to operate optimally. The LO driver amplifier is self

biased, and it requires only a single dc bias voltage (VDLO),

which draws approximately 170 mA at 3 V under the LO drive.

The LO amplitude range of −4 dBm to +4 dBm makes it

compatible with the Analog Devices, Inc., wideband synthesizer

portfolio without the need for an external LO driver amplifier.

MIXER

The mixer is an I/Q double balanced mixer, and this mixer

topology reduces the need for filtering unwanted sideband.

An external 90° hybrid is required to select the upper sideband

of operation. The ADMV1012 has been optimized to work with

the Mini-Circuits QCN-45+ RF 90° hybrid.

LNA

The LNA requires a single dc bias voltage (VDRF) and a single

dc gate bias (VGRF) to operate. Starting at −1.8 V at the gate

supply (VGRF), the LNA is biased at +3 V (VDRF). Then, the

gate bias (VGRF) is varied until the desired LNA bias current

(IDRF) is achieved. The desired LNA bias current is 68 mA at

3 V under small signal conditions.

The typical application circuit (see Figure 34) shows the

necessary external components on the bias lines to eliminate

any undesired stability problems for the RF amplifier and the

LO amplifier.

The ADMV1012 is a much smaller alternative to hybrid style

image reject converter assemblies, and it eliminates the need

for wire bonding by allowing the use of surface-mount

manufacturing assemblies.

The ADMV1012 downconverter comes in a compact, thermally

enhanced, 4.9 mm × 4.9 mm, 32-terminal ceramic leadless chip

carrier (LCC) package. The ADMV1012 operates over the

−40°C to +85°C temperature range.