IDT1339

REAL-TIME CLOCK WITH SERIAL I

2

C INTERFACE RTC

IDT®

REAL-TIME CLOCK WITH SERIAL I

2

C INTERFACE 16

IDT1339 REV S 031014

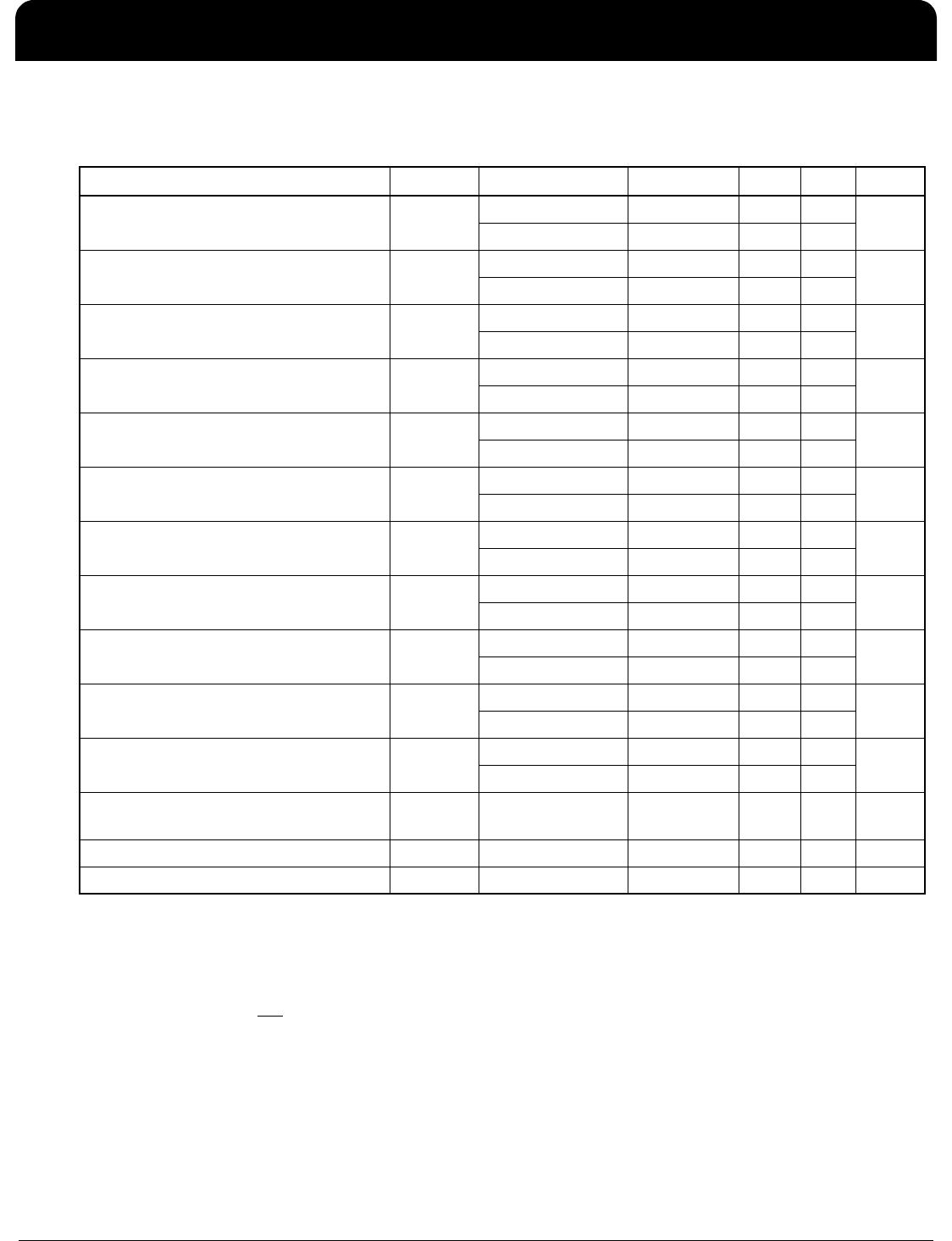

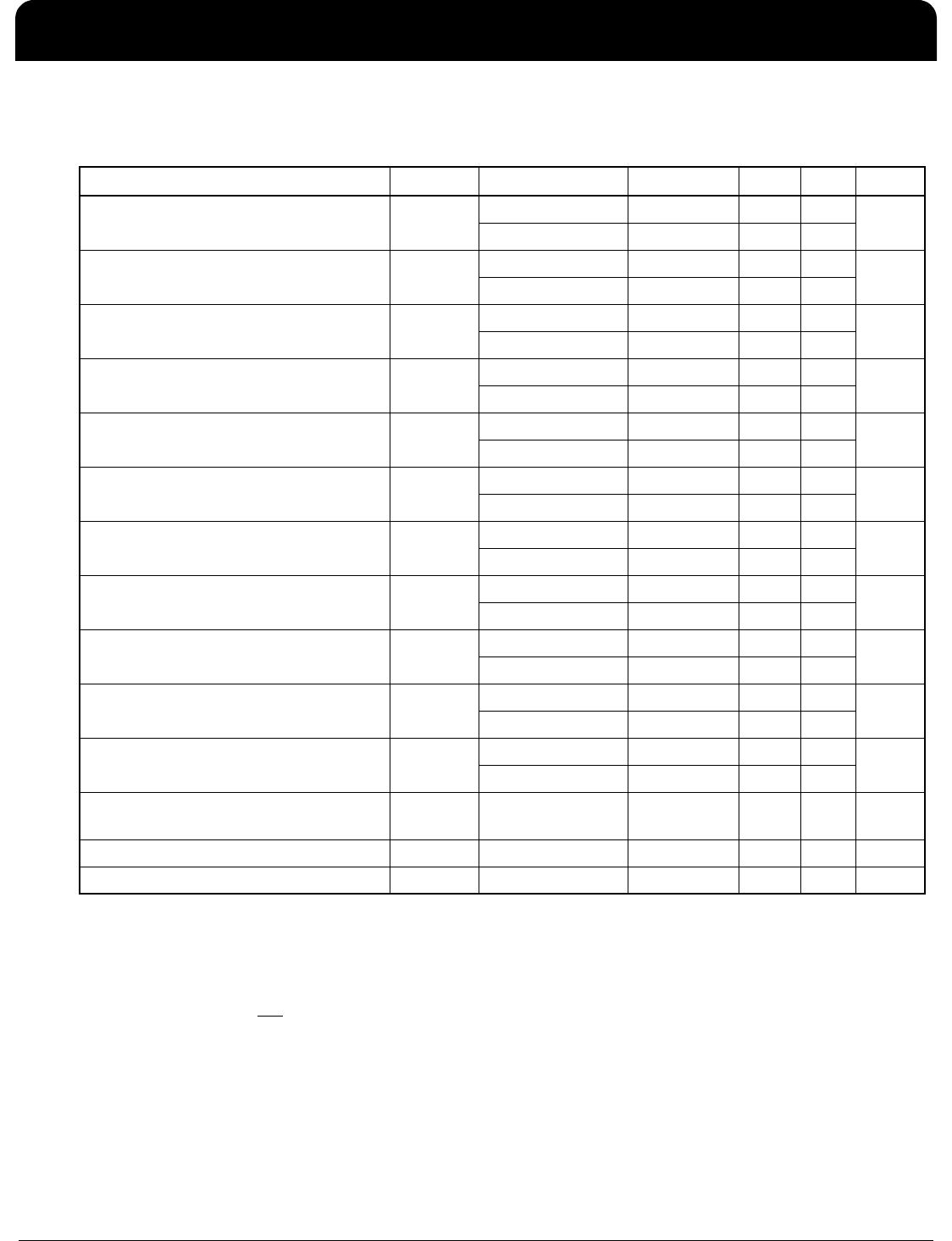

AC Electrical Characteristics

Unless stated otherwise, V

CC

= MIN to MAX, Ambient Temperature -40 to +85C, Note 13

WARNING: Under no circumstances are negative undershoots, of any amplitude, allowed when device is in

battery-backup mode.

Note 1: Limits at -40°C are guaranteed by design and are not production tested.

Note 2: SCL only.

Note 3: SDA and SQW/INT

.

Note 4: I

CCA

—SCL at f

SC

max, VIL = 0.0V, VIH = V

CC

, trickle charger disabled.

Note 5: Specified with the I

2

C bus inactive, VIL = 0.0V, VIH = V

CC

, trickle charger disabled.

Note 6:

V

CC

must be less than 3.63 V if the 250 resistor is selected.

Parameter Symbol Conditions Min. Typ. Max. Units

SCL Clock Frequency f

SCL

Fast Mode 100 400 kHz

Standard Mode 100

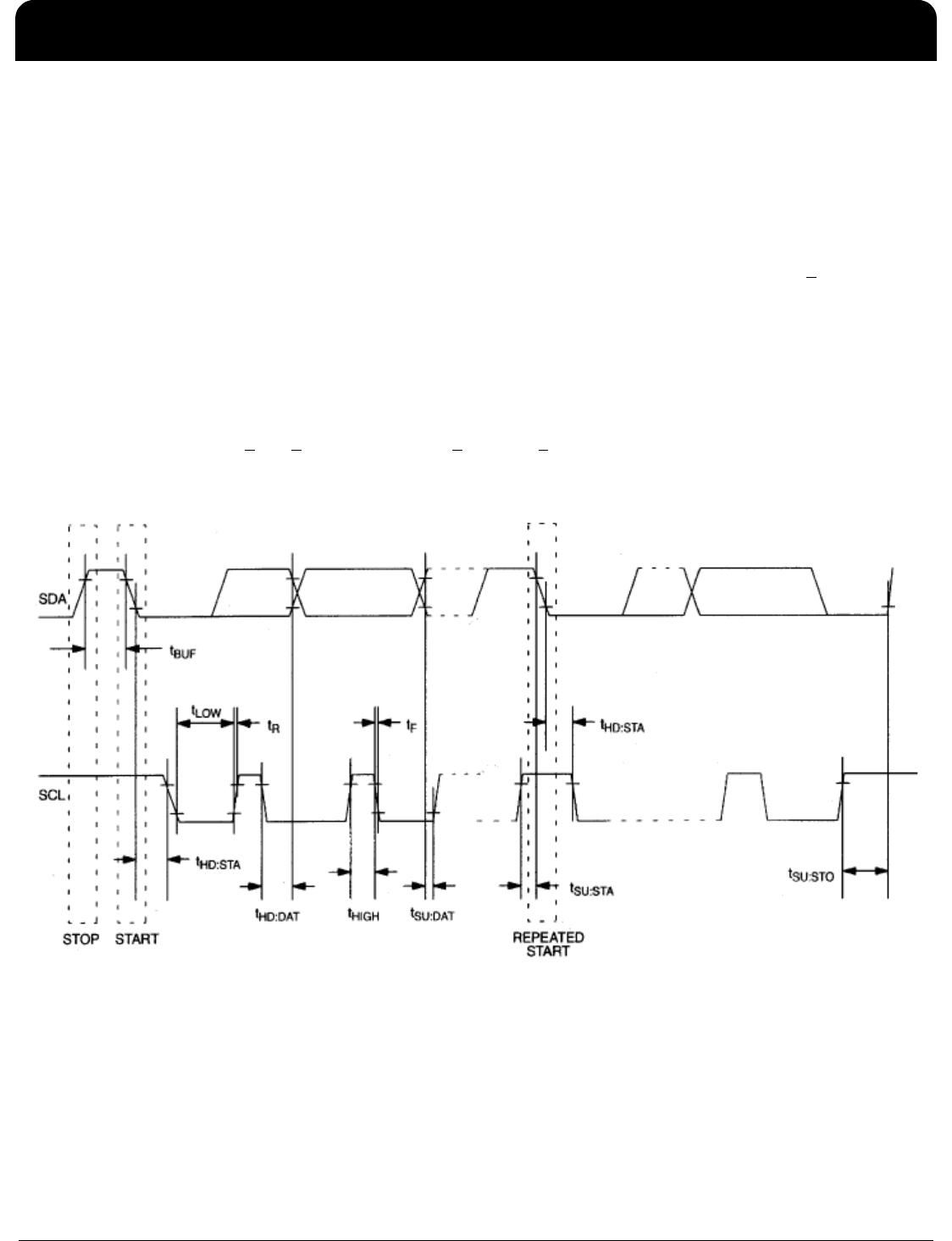

Bus Free Time Between a STOP and

START Condition

t

BUF

Fast Mode 1.3 µs

Standard Mode 4.7

Hold Time (Repeated) START

Condition, Note 8

t

HD:STA

Fast Mode 0.6 µs

Standard Mode 4.0

Low Period of SCL Clock t

LOW

Fast Mode 1.3 µs

Standard Mode 4.7

High Period of SCL Clock t

HIGH

Fast Mode 0.6 µs

Standard Mode 4.0

Setup Time for a Repeated START

Condition

t

SU:STA

Fast Mode 0.6 µs

Standard Mode 4.7

Data Hold Time, Notes 9, 10 t

HD:DAT

Fast Mode 0 0.9 µs

Standard Mode 0

Data Setup Time, Note 11 t

SU:DAT

Fast Mode 100 ns

Standard Mode 250

Rise Time of Both SDA and SCL

Signals, Note 12

t

R

Fast Mode 20 + 0.1C

B

300 ns

Standard Mode 20 + 0.1C

B

1000

Fall Time of Both SDA and SCL Signals,

Note 12

t

F

Fast Mode 20 + 0.1C

B

300 ns

Standard Mode 20 + 0.1C

B

300

Setup Time for STOP Condition t

SU:STO

Fast Mode 0.6 µs

Standard Mode 4.0

Capacitive Load for Each Bus Line,

Note 12

C

B

400 pF

I/O Capacitance (SDA, SCL) C

I/O

Note 13 10 pF

Oscillator Stop Flag (OSF) Delay t

OSF

Note 14 100 ms