Functional description of the SPI L9954LXP

24/35 Doc ID 16186 Rev 3

4 Functional description of the SPI

4.1 Serial Peripheral Interface (SPI)

This device uses a standard SPI to communicate with a microcontroller. The SPI can be

driven by a microcontroller with its SPI peripheral running in following mode: CPOL = 0 and

CPHA = 0.

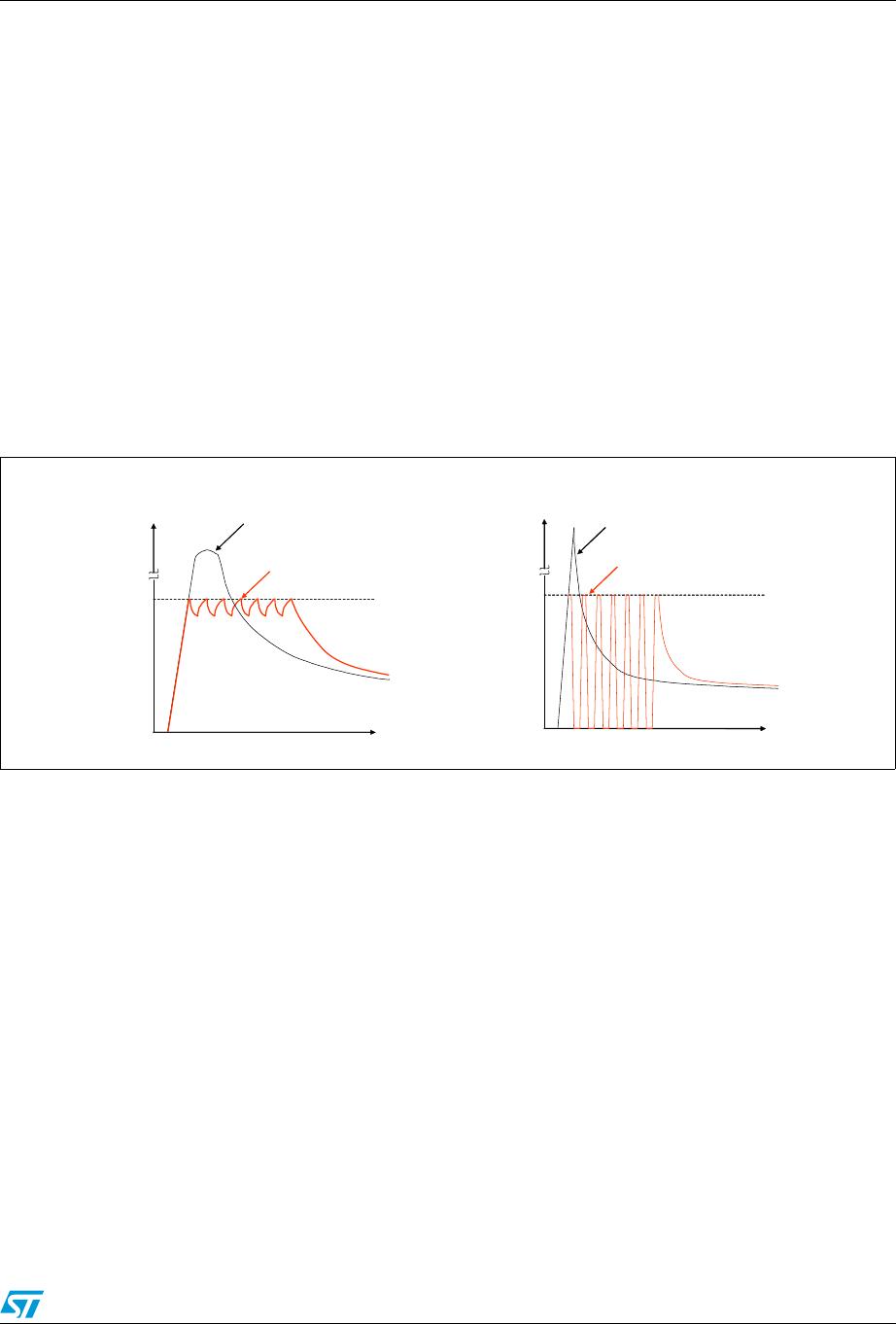

For this mode, input data is sampled by the low to high transition of the clock CLK, and

output data is changed from the high to low transition of CLK.

This device is not limited to microcontroller with a build-in SPI. Only three CMOS compatible

output pins and one input pin are needed to communicate with the device. A fault condition

can be detected by setting CSN to low. If CSN = 0, the DO pin reflects the status bit 0 (fault

condition) of the device which is a logical-or of all bits in the status registers 0 and 1. The

microcontroller can poll the status of the device without the need of a full SPI communication

cycle.

Note: In contrast to the SPI standard the least significant bit (LSB) is transferred first

(see Figure 3).

4.2 Chip Select Not (CSN)

The input pin is used to select the serial interface of this device. When CSN is high, the

output pin (DO) is in high impedance state. A low signal activates the output driver and a

serial communication can be started. The state when CSN is going low until the rising edge

of CSN is called a communication frame.

4.3 Serial Data In (DI)

The input pin is used to transfer data serial into the device. The data applied to the DI is

sampled at the rising edge of the CLK signal and shifted into an internal 24 bit shift register.

At the rising edge of the CSN signal the contents of the shift register is transferred to data

input register. The writing to the selected data input register is only enabled if exactly 24 bits

are transmitted within one communication frame (i.e. CSN low). If more or less clock pulses

are counted within one frame the complete frame is ignored. This safety function is

implemented to avoid an activation of the output stages by a wrong communication frame.

Note: Due to this safety functionality a daisy chaining of SPI is not possible. Instead, a parallel

operation of the SPI bus by controlling the CSN signal of the connected ICs is

recommended.

4.4 Serial Data Out (DO)

The data output driver is activated by a logical low-level at the CSN input and goes from high

impedance to a low or high-level depending on the status bit 0 (fault condition). The first

rising edge of the CLK input after a high to low transition of the CSN pin transfers the

content of the selected status register into the data out shift register. Each subsequent

falling edge of the CLK shifts the next bit out.