20©2016 Integrated Device Technology, Inc. Revision D September 27, 2016

83905 Datasheet

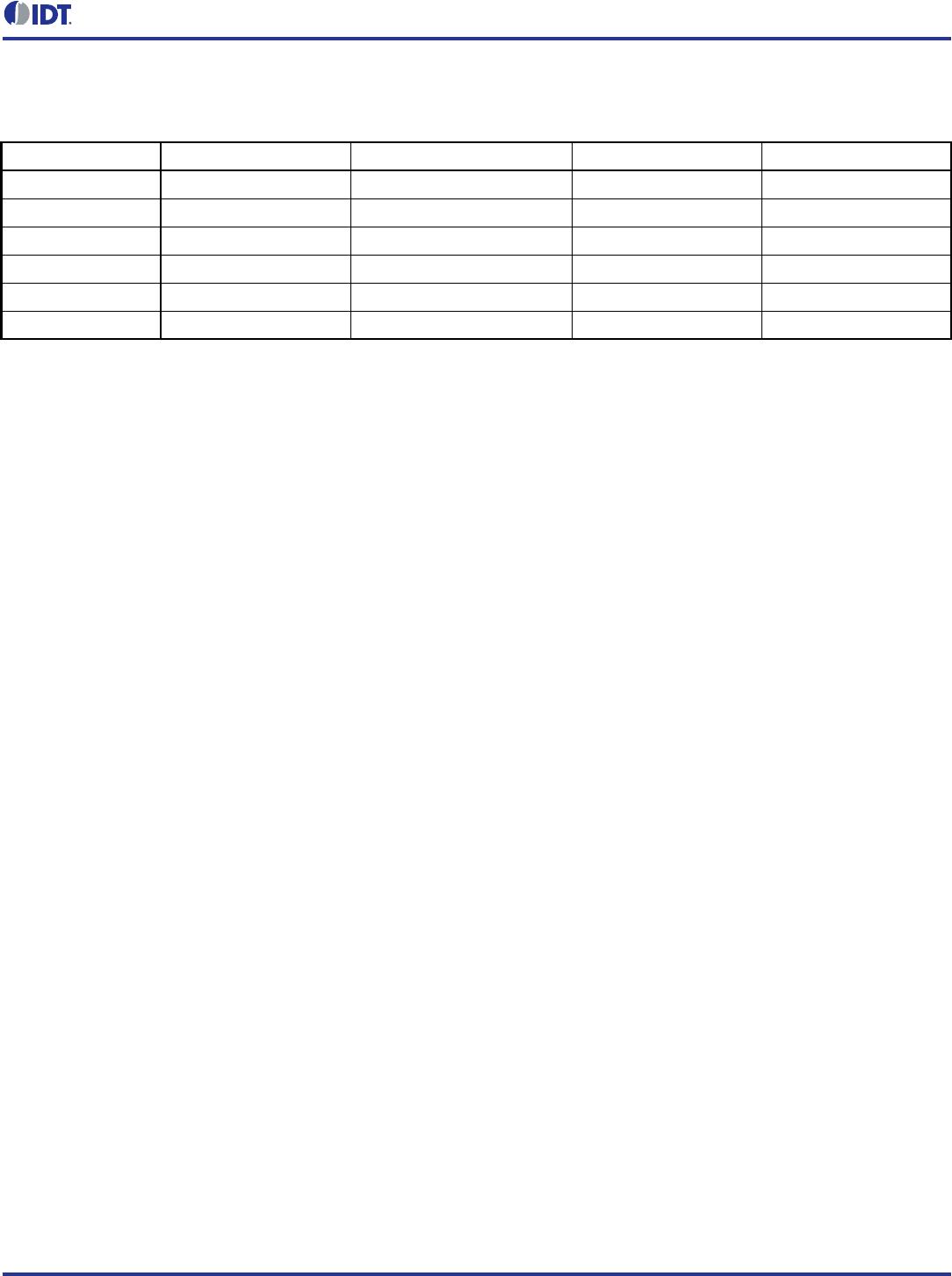

Revision History Sheet

Rev Table Page Description of Change Date

A 2 Added Enable Timing Diagram. 3/28/05

BT6A - T6F

1

5 - 7

8

Features Section - added RMS Phase Jitter bullet.

AC Characteristics Tables - added RMS Phase Jitter specs.

Added Phase Noise Plot.

4/8/05

B T9 14 Ordering Information Table - added TSSOP, non-LF part number. 4/25/05

B

11

12

Added Crystal Input Interface in Application Section.

Added Schematic layout.

5/16/05

B

3

11

13

Absolute Maximum Ratings - corrected 20-Lead VFQFN package Thermal

Impedance.

Added Recommendations for Unused Input and Output Pins.

Corrected Theta JA Air Flow Table for 20-Lead VFQFN.

10/2/06

B

T9

11

12

17

Added LVCMOS to XTAL Interface section.

Added Thermal Release Path section.

AC Characteristics Table - added lead-free marking for 20-Lead VFQFN package.

7/9/07

B

T7B - T7C

3

12

14

16

Absolute Maximum Ratings - updated TSSOP and VFQFN Thermal Impedance.

Updated Thermal Release Path section.

Updated TSSOP and VFQFN Thermal Impedance.

Added note to VFQFN Package Outline.

1/24/08

B

15 Added Power Considerations section.

Converted datasheet format.

7/20/09

B T10 19 Removed leaded order-able parts from Ordering Information table 11/14/12

C

T6D

T9A

T11

1, 15

1

7

14

17

18

19

Deleted HiPerClockS references.

Features, last bullet: updated packaging note.

Mixed AC Characteristics Table - corrected typo, switched Output Rise/Fall Time

spec with Output Duty Cycle spec.

Replaced schematic.

16-Lead TSSOP Package Table - corrected dimension A1 Minimum = 0.05.

Updated VFQFN package outline page.

Ordering Information table - deleted Lead-free note, and quantity from Tape and

Reel.

4/18/13

C 1 Pin Assignment: Corrected 20-Lead illustration cut-off text 2/27/14

C

T6A - T6F

T10

1

6 - 8

9

11

18

21

Pin Assignment, 20-Lead VFQFN: removed the Epad dimensions.

Changed NOTE 1to XTAL_IN can be overdriven by a single-ended LVCMOS signal.

Please refer to Application Information section.

Deleted 3.3V Phase Noise Plot

Deleted RMS Phase Jitter graph.

Modified dimensions to reflect tightened tolerances.

Updated contact information.

8/6/14

D

2 Figure 1 corrected.

Updated datasheet header/footer.

Deleted “ICS” prefix from part number throughout the datasheet

9/27/16