HIGH RIPPLE-REJECTION LOW DROPOUT CMOS VOLTAGE REGULATOR

Rev.4.1_02

S-1165 Series

13

3. ON/OFF pin

This pin starts and stops the regulator.

When the ON/OFF pin is set to OFF level, the entire internal circuit stops operating, and the built-in P-

channel MOS FET output transistor between the VIN pin and the VOUT pin is turned off, reducing current

consumption significantly. The VOUT pin becomes the Vss level due to the internally divided resistance

of several hundreds k between the VOUT pin and the VSS pin.

The structure of the ON/OFF pin is as shown in Figure 12. Since the ON/OFF pin is neither pulled

down nor pulled up internally, do not use it in the floating status. In addition, note that the current

consumption increases if a voltage of 0.3 V to V

IN

– 0.3 V is applied to the ON/OFF pin. When not using

the ON/OFF pin, connect it to the VSS pin in the product A type, connect it to the VIN pin in B type.

Table 5

Product Type ON/OFF Pin Internal Circuit VOUT Pin Voltage Current Consumption

A “L”: ON Operate Set value I

SS1

A “H”: OFF Stop V

SS

level I

SS2

B “L”: OFF Stop V

SS

level I

SS2

B “H”: ON Operate Set value I

SS1

VSS

ON/OFF

VIN

Figure 12

Selection of Output Capacitor (C

L

)

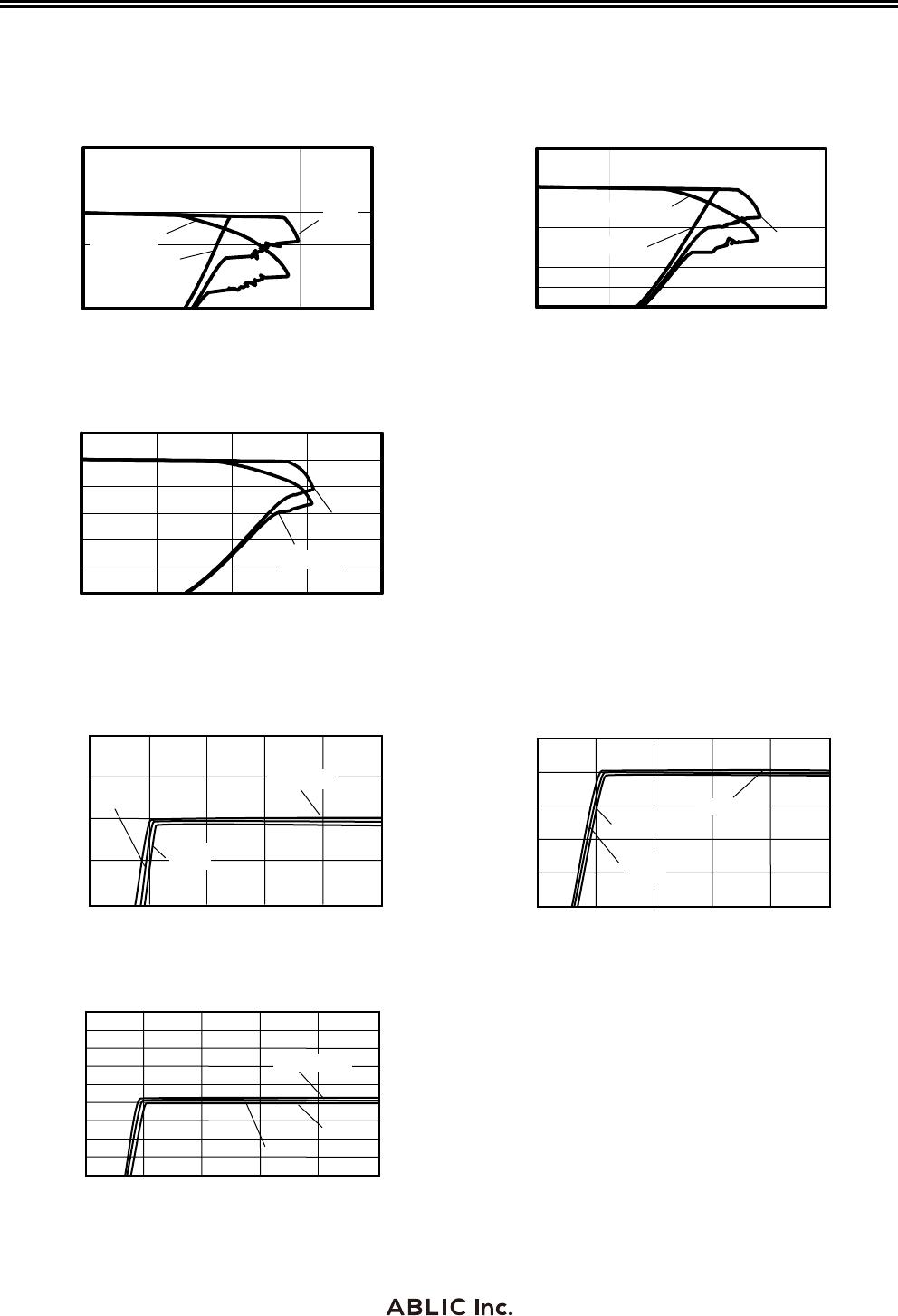

The S-1165 Series performs phase compensation using the internal phase compensator in the IC and the

ESR (Equivalent Series Resistance) of the output capacitor to enable stable operation independent of

changes in the output load. Therefore, always place a capacitor (C

L

) of 2.2 F or more between the

VOUT pin and the VSS pin.

For stable operation of the S-1165 Series, it is essential to employ a capacitor whose ESR is within an

optimum range. Using a capacitor whose ESR is outside the optimum range (approximately 0.5 to

5 ), whether larger or smaller, may cause an unstable output, resulting in oscillation. For this reason, a

tantalum electrolytic capacitor is recommended.

When a ceramic capacitor or an OS capacitor with a low ESR is used, it is necessary to connect an

additional resistor that serves as the ESR in series with the output capacitor. The required resistance

value is approximately 0.5 to 5 , which varies depending on the usage conditions, so perform sufficient

evaluation for selection. Ordinarily, around 1.0 is recommended.

Note that an aluminum electrolytic capacitor may increase the ESR at a low temperature, causing

oscillation. When using this kind of capacitor, perform thorough evaluation, including evaluation of

temperature characteristics.