LTC2943

16

2943fa

For more information www.linear.com/LTC2943

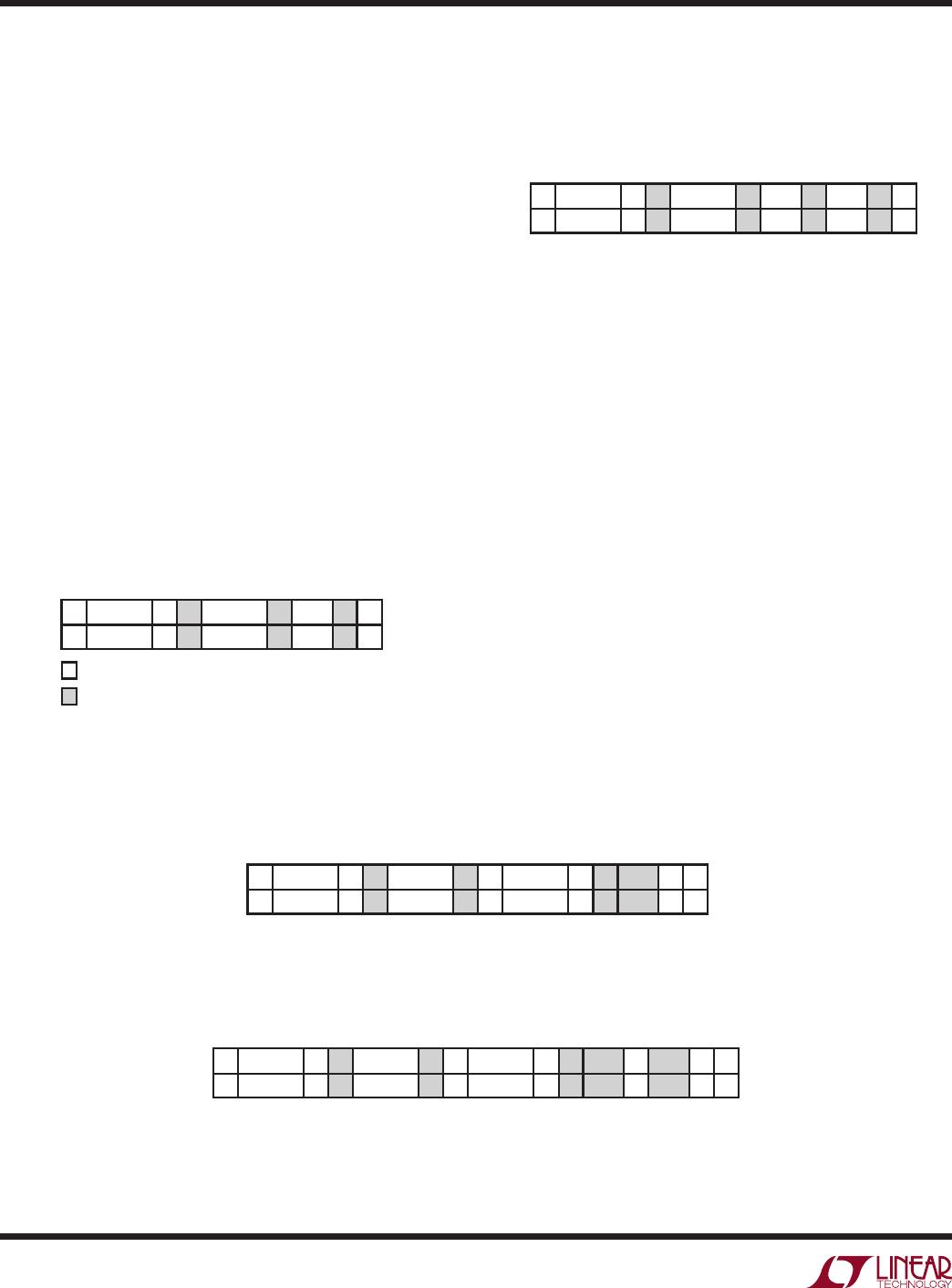

Figure 5. Writing FCh to the LTC2943 Control Register (B)

transitioning SDA from low to high while SCL is high. The

bus is then free for another transmission. When the bus

is in use, it stays busy if a repeated START (Sr) is gener

-

ated instead of a STOP condition. The repeated START

(Sr) conditions are functionally identical to the START (S).

Write Protocol

The master begins a write operation with a START condition

followed by the seven bit slave address 1100100 and the

R/W bit set to zero, as shown in Figure 5. The LTC2943

acknowledges this by pulling SDA low and the master

sends a command byte which indicates which internal

register the master is to write. The LTC2943 acknowledges

and latches the command byte into its internal register

address pointer. The master delivers the data byte, the

LTC2943 acknowledges once more and latches the data

into the desired register. The transmission is ended when

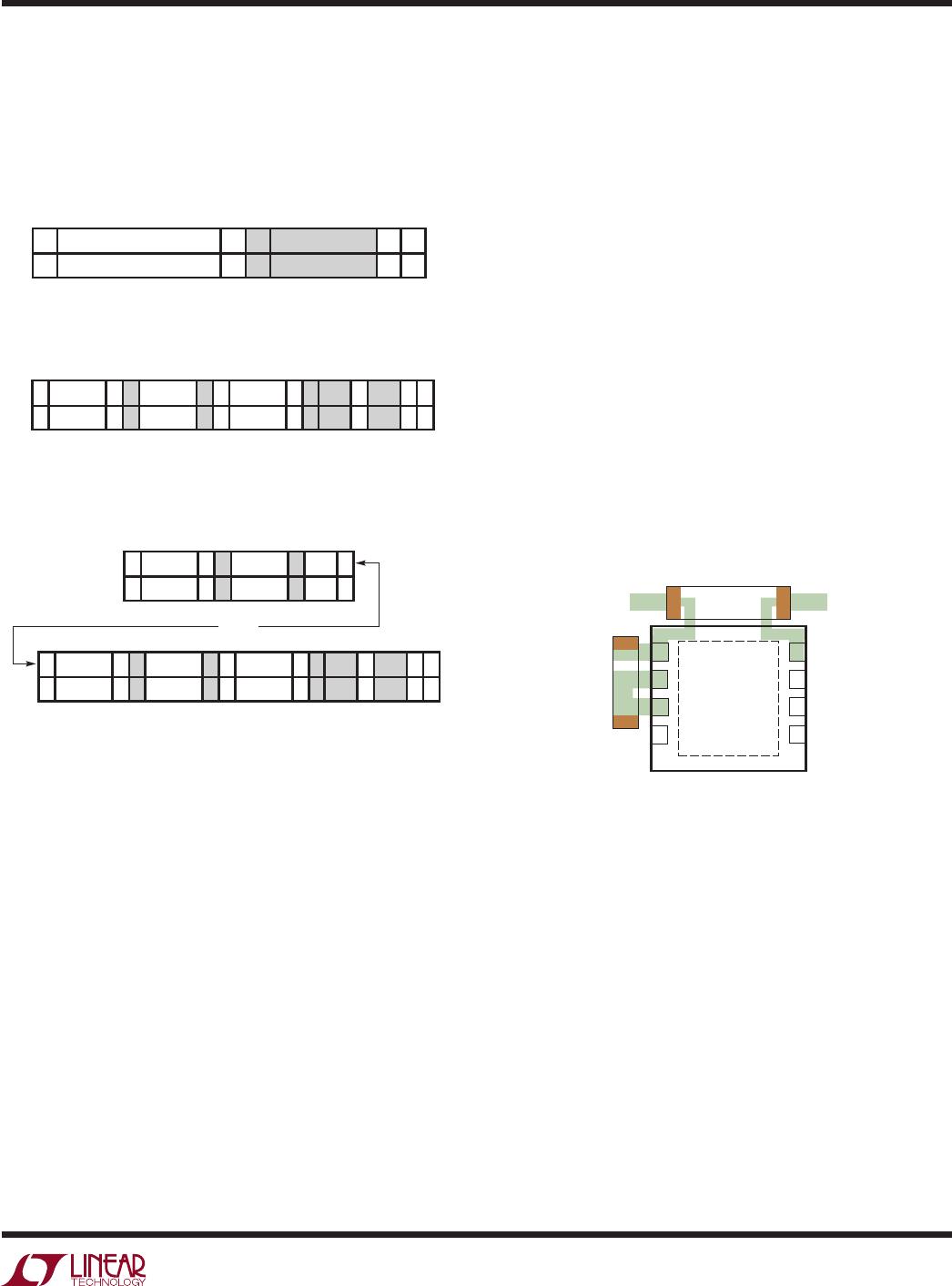

the master sends a STOP condition. If the master contin

-

ues by

sending a second data byte instead of a stop, the

APPLICATIONS INFORMATION

LTC2943 acknowledges again, increments its address

pointer and latches the second data byte in the following

register, as

shown in Figure 6.

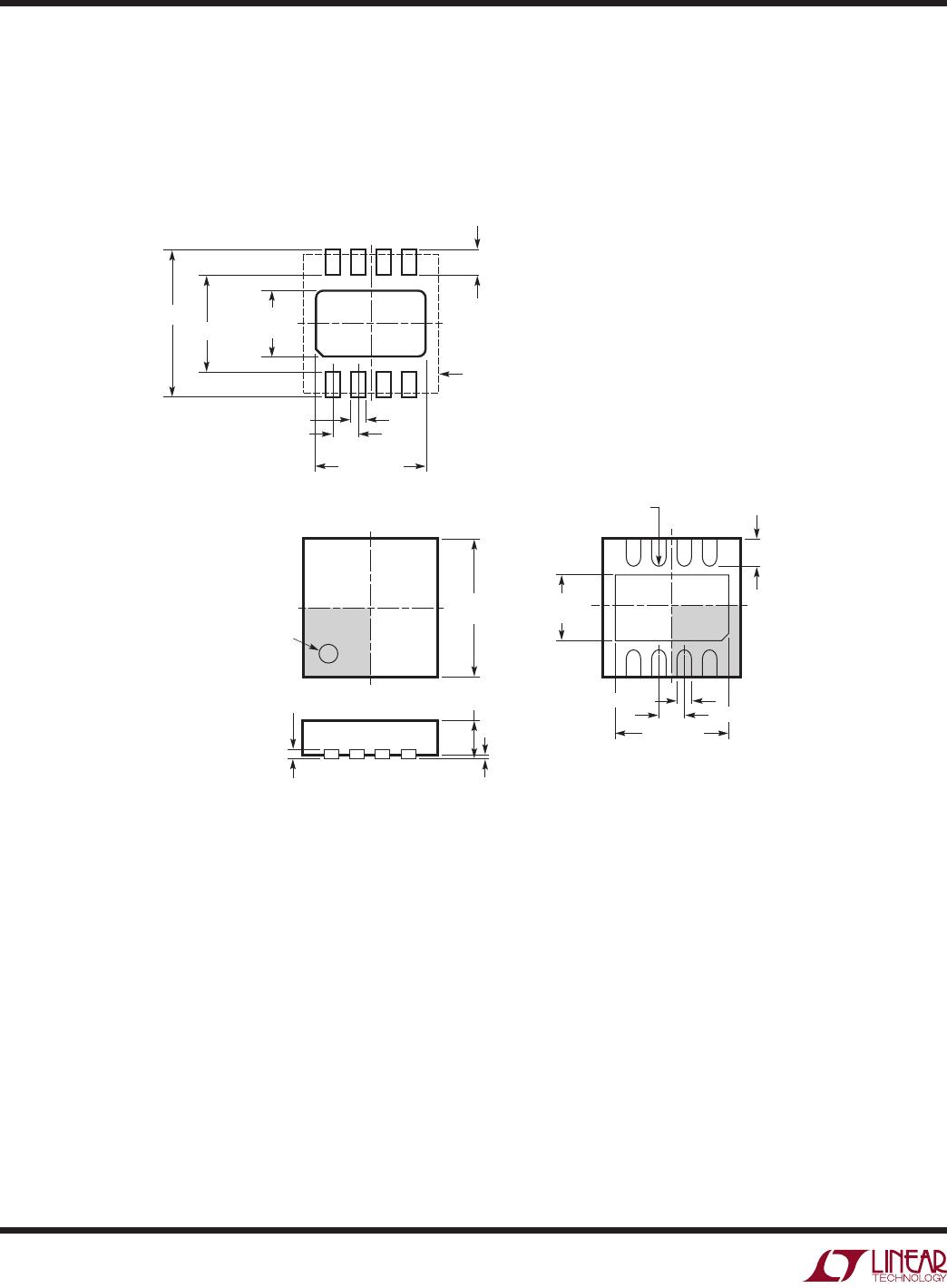

Read Protocol

The

master begins a read operation with a START condition

followed by the seven bit slave address 1100100 and the

R/W bit set to zero, as shown in Figure 7. The LTC2943

acknowledges and the master sends a command byte

which indicates which internal register the master is to

read. The LTC2943 acknowledges and then latches the

command byte into its internal register address pointer.

The master then sends a repeated START condition fol

-

lowed by the same seven bit address with the R/W bit

now

set to one. The LTC2943 acknowledges and sends

the contents of the requested register. The transmission

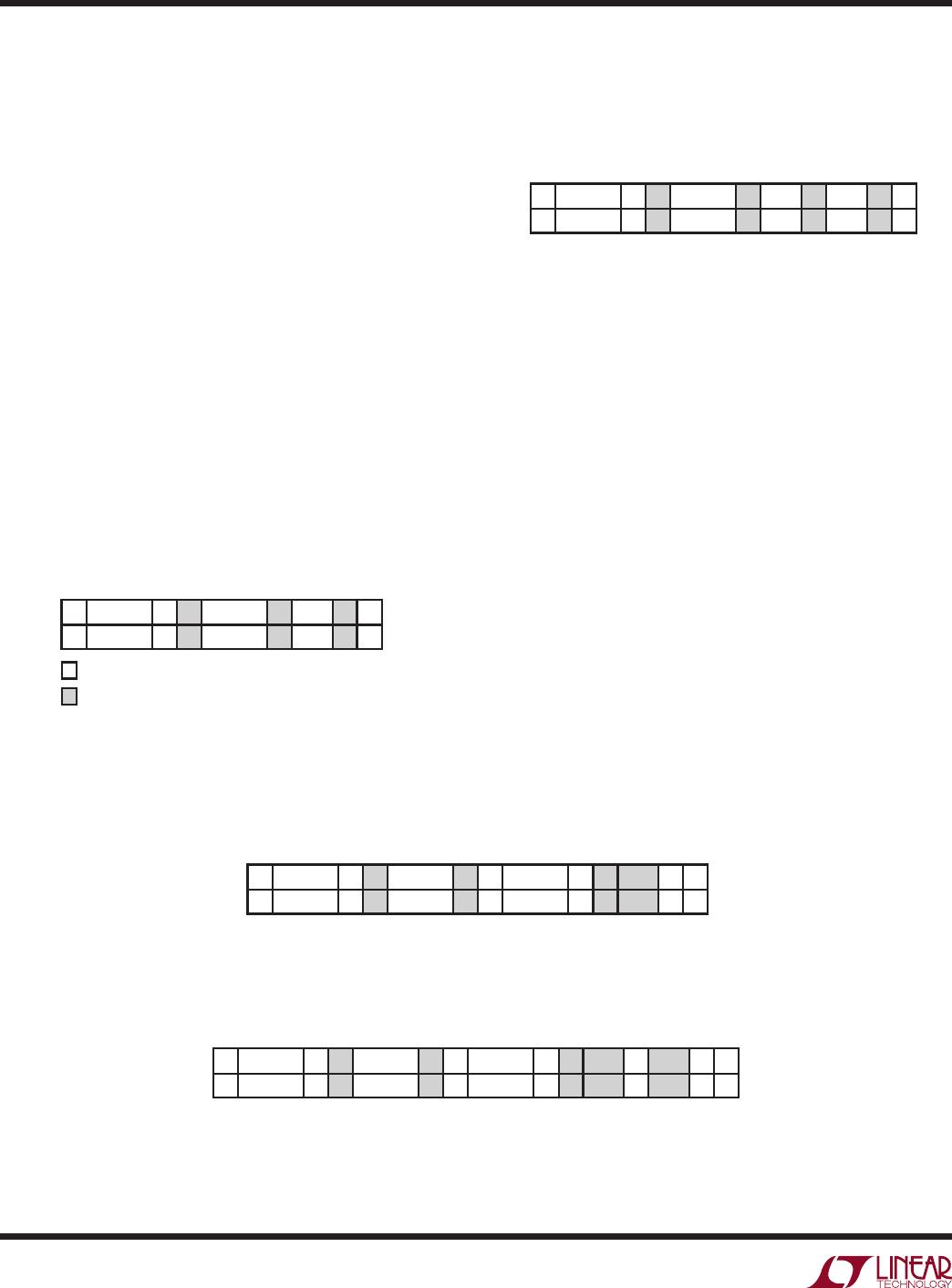

is ended when the master sends a STOP condition. If

the master acknowledges the transmitted data byte, the

LTC2943 increments its address pointer and sends the

contents of the following register as depicted in Figure 8.

Figure 6. Writing F001h to the LTC2943 Accumulated Charge

Register (C, D)

Figure 7. Reading the LTC2943 Status Register (A)

Figure 8. Reading the LTC2943 Voltage Register (I, J)

FROM MASTER TO SLAVE

S W

ADDRESS REGISTER DATA

FROM SLAVE TO MASTER

2943 F05

A: ACKNOWLEDGE (LOW)

A: NOT ACKNOWLEDGE (HIGH)

S: START CONDITION

P: STOP CONDITION

R: READ BIT (HIGH)

W: WRITE BIT (LOW)

A A A

0

1100100 01h FCh

0 0 0

P

S W

ADDRESS REGISTER DATA

A A A

0

1100100 02h F0h 01h

0 0 0

0

P

DATA

A

S W

ADDRESS REGISTER Sr

2943 F07

A A ADDRESS

0

1100100 00h 1

0 0 1100100

0

P

R

1

A

01h

DATA

A

S W

ADDRESS REGISTER Sr

2943 F08

A A ADDRESS

0

1100100 08h 1

0 0 1100100

0

P

R

0

A

F1h

DATA

24h

DATA

A

1

A