17

LT1995

1995fb

APPLICATIO S I FOR ATIO

WUUU

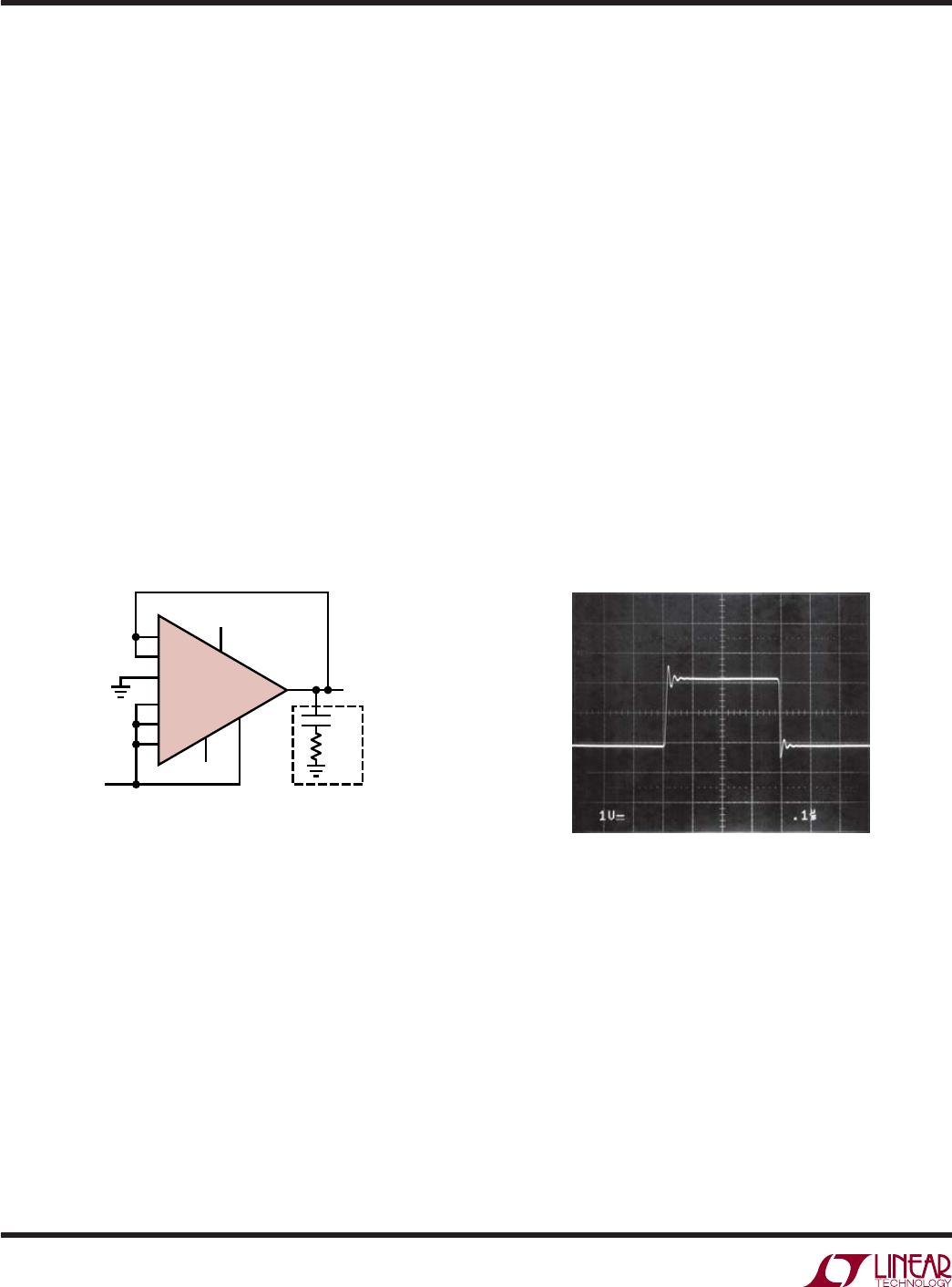

If one of the A parameter configurations in Figure 3 is

preferred, or the use of an external biasing source is

desired, the P and REF input connections shown grounded

in a Figure 3 circuit may be instead driven by a V

BIAS

voltage to establish a quiescent operating point for the

input and output pins. The V

IN

connections of the Figure 3

circuit are then driven via a coupling capacitor. Any

grounded M inputs for the desired G configuration (refer

to Figure 2) must be individually or collectively

AC-coupled to ground. Figure 8 illustrates a complete

example circuit of an externally biased AC-coupled nonin-

verting amplifier. The V

BIAS

source impedance should be

low (a few ohms) to avoid degrading the inherent accuracy

of the LT1995. 0.013% of additional Gain Error for each

ohm of resistance on the REF pin is typical.

at room temperature, and to within 0.3% over tempera-

ture. The temperature coefficient of the resistors is typi-

cally –30ppm/°C. The resistors have been sized to accom-

modate 15V across each resistor, or in terms of power,

225mW in the 1k resistors, 113mW in the 2k resistors, and

56mW in the 4k resistors.

Power Supply Considerations

As with any high speed amplifier, the LT1995 printed

circuit layout should utilize good power supply decoupling

practices. Good decoupling will typically consist of one or

more capacitors employing the shortest practical inter-

connection traces and direct vias to a ground plane. This

practice minimizes inductance at the supply pins so the

impedance is low at the operating frequencies of the part,

thereby suppressing feedback or crosstalk artifacts that

might otherwise lead to extended settling times, fre-

quency response anomalies, or even oscillation. For high

speed parts like the LT1995, 10nF ceramics are suitable

close-in bypass capacitors, and if high currents are being

delivered to a load, additional 4.7µF capacitors in parallel

can help minimize induced power supply transients.

Because unused input pins are connected via resistors to

the input of the op amp, excessive capacitances on these

pins will degrade the rise time, slew rate, and step re-

sponse of the output. Therefore, these pins should not be

connected to large traces which would add capacitance

when not in use.

Since the LT1995 has a wide operating supply voltage

range, it is possible to place the part in situations of

relatively high power dissipation that may cause excessive

die temperatures to develop. Maximum junction tempera-

ture (T

J

) is calculated from the ambient temperature (T

A

)

M4

M2

M1

P1

P2

P4

8

9

10

1

2

3

V

OUT

CONFIGURATION EXAMPLE:

A = 0.625

G = 6.00

(V

OUT

/V

IN

= 3.75V)

C

OUT

V

BIAS

V

IN

+V

6

4

5

1995 F08

7

LT1995

REF

C

BYP

C

IN

Figure 8. AC-Coupled Noninverting Amplifier

with External Bias Source (Example)

Resistor Considerations

The resistors in the LT1995 are very well matched, low

temperature coefficient thin film based elements. Although

their absolute tolerance is fairly wide (typically ±5% but

±25% worst case), the resistor matching is to within 0.2%