10 Integrated Silicon Solution, Inc. - www.issi.com

Rev. A

10/22/09

IS42SM83200D / IS42SM16160D / IS42SM32800D

IS42RM83200D / IS42RM16160D / IS42RM32800D

Burst Type

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to as the

burst type and is selected via bit M3.

The ordering of accesses within a burst is determined by the burst length, the burst type and the starting column

address, as shown in BURST DEFINITION table.

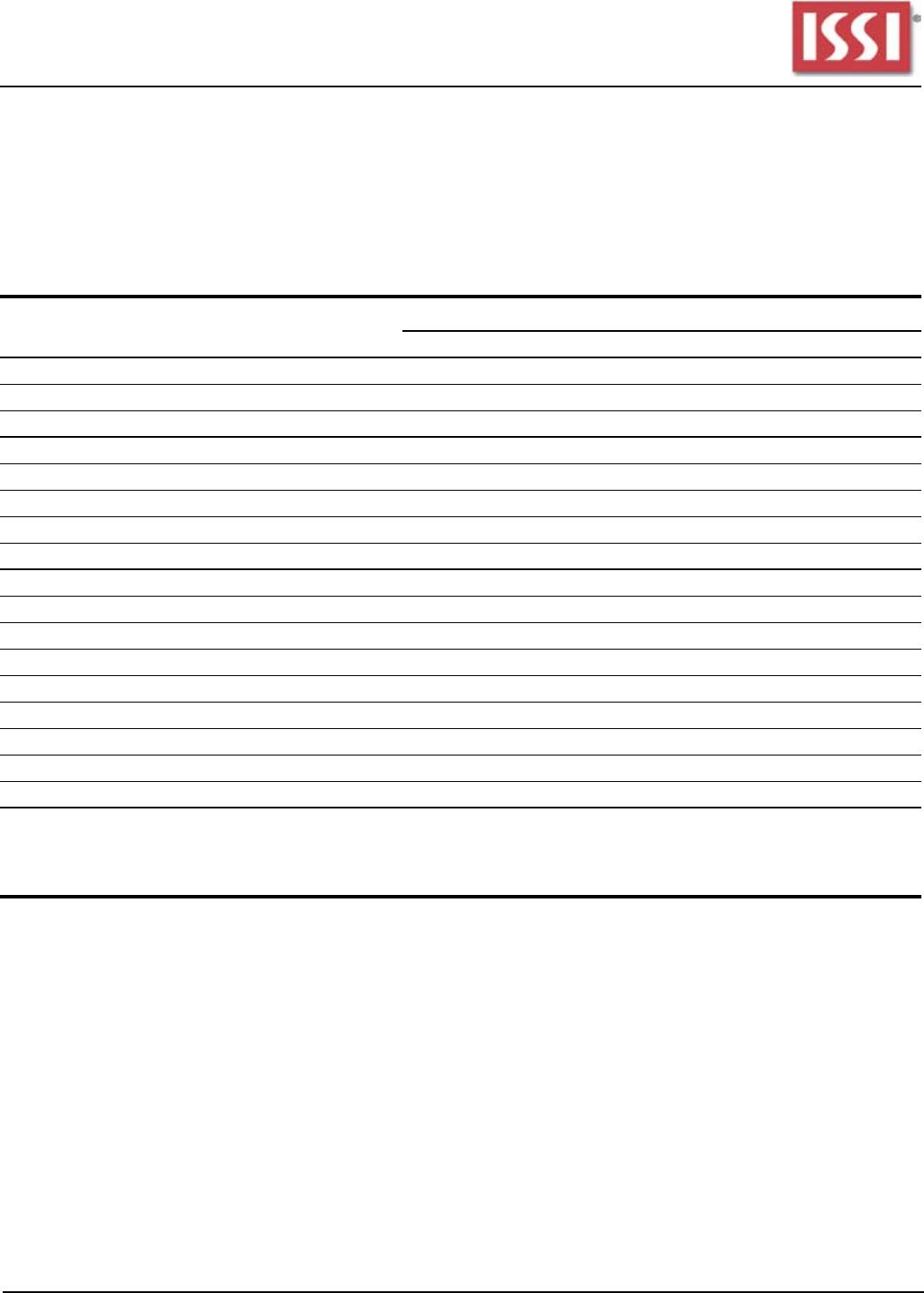

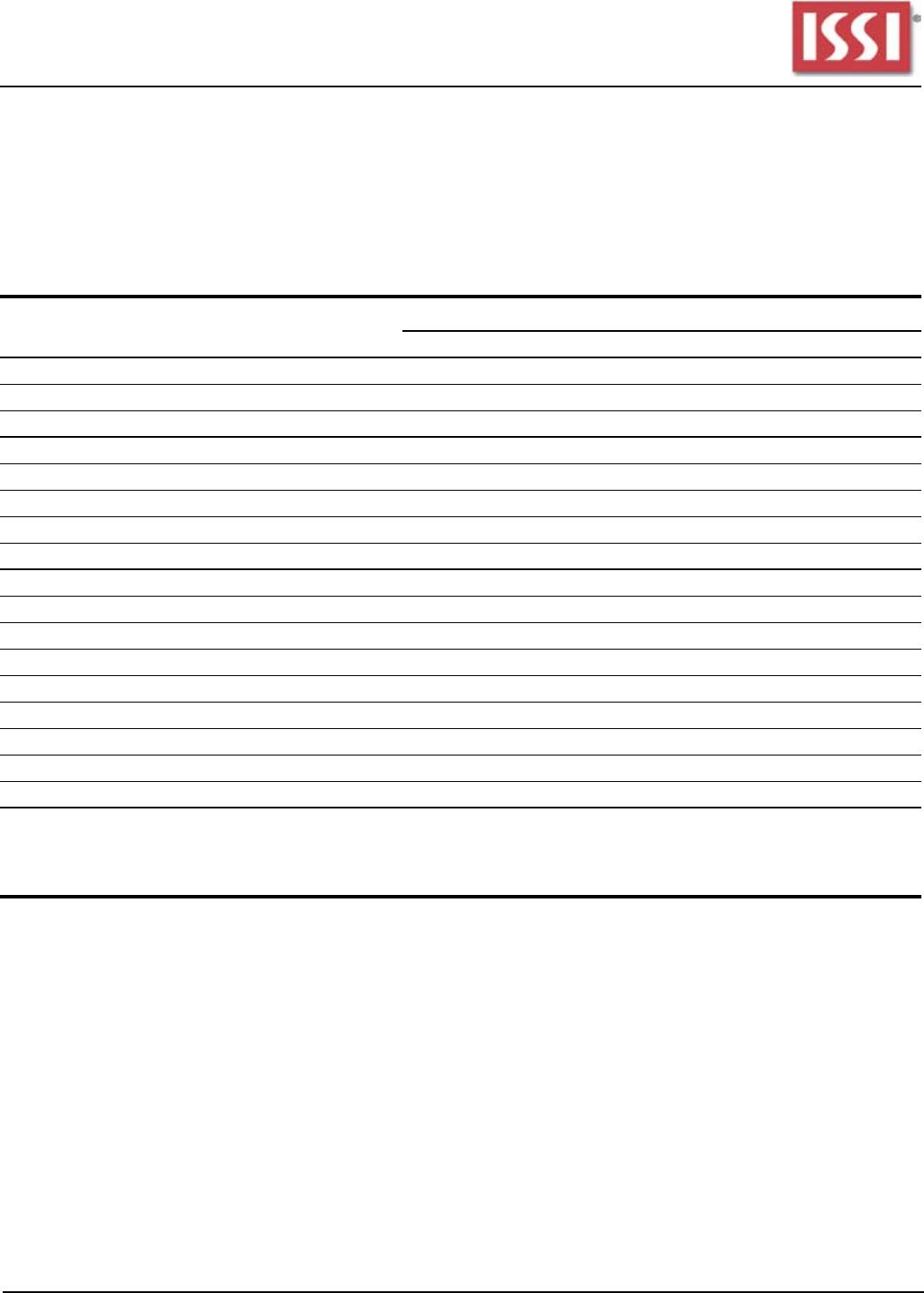

BURST DEFINITION

Burst Starting Column Order of Accesses Within a Burst

Length Address Type = Sequential Type = Interleaved

A0

2 0 0-1 0-1

1 1-0 1-0

A1 A0

0 0 0-1-2-3 0-1-2-3

4 0 1 1-2-3-0 1-0-3-2

1 0 2-3-0-1 2-3-0-1

1 1 3-0-1-2 3-2-1-0

A2 A1 A0

0 0 0 0-1-2-3-4-5-6-7 0-1-2-3-4-5-6-7

0 0 1 1-2-3-4-5-6-7-0 1-0-3-2-5-4-7-6

0 1 0 2-3-4-5-6-7-0-1 2-3-0-1-6-7-4-5

8 0 1 1 3-4-5-6-7-0-1-2 3-2-1-0-7-6-5-4

1 0 0 4-5-6-7-0-1-2-3 4-5-6-7-0-1-2-3

1 0 1 5-6-7-0-1-2-3-4 5-4-7-6-1-0-3-2

1 1 0 6-7-0-1-2-3-4-5 6-7-4-5-2-3-0-1

1 1 1 7-0-1-2-3-4-5-6 7-6-5-4-3-2-1-0

Full n = A0-A8 (x16, x32) Cn, Cn + 1, Cn + 2 Not Supported

Page n = A0-A9 (x8) Cn + 3, Cn + 4...

(y) (location 0-y) …Cn - 1,

Cn…

CAS Latency

The CAS latency is the delay, in clock cycles, between the registration of a READ command and the availability of the

first piece of output data. The latency can be set to two or three clocks.

If a READ command is registered at clock edge n, and the latency is m clocks, the data will be available by clock

edge n + m. The DQs will start driving as a result of the clock edge one cycle earlier (n + m - 1), and provided that

the relevant access times are met, the data will be valid by clock edge n + m. For example, assuming that the clock

cycle time is such that all relevant access times are met, if a READ command is registered at T0 and the latency

is programmed to two clocks, the DQs will start driving after T1 and the data will be valid by T2, as shown in CAS

Latency diagrams.

Reserved states should not be used as unknown operation or incompatibility with future versions may result.

Operating Mode

The normal operating mode is selected by setting M7 and M8 to zero; the other combinations of values for M7 and M8

are reserved for future use and/or test modes. The programmed burst length applies to both READ and WRITE bursts.