16 Integrated Silicon Solution, Inc. - www.issi.com

Rev. A

10/22/09

IS42SM83200D / IS42SM16160D / IS42SM32800D

IS42RM83200D / IS42RM16160D / IS42RM32800D

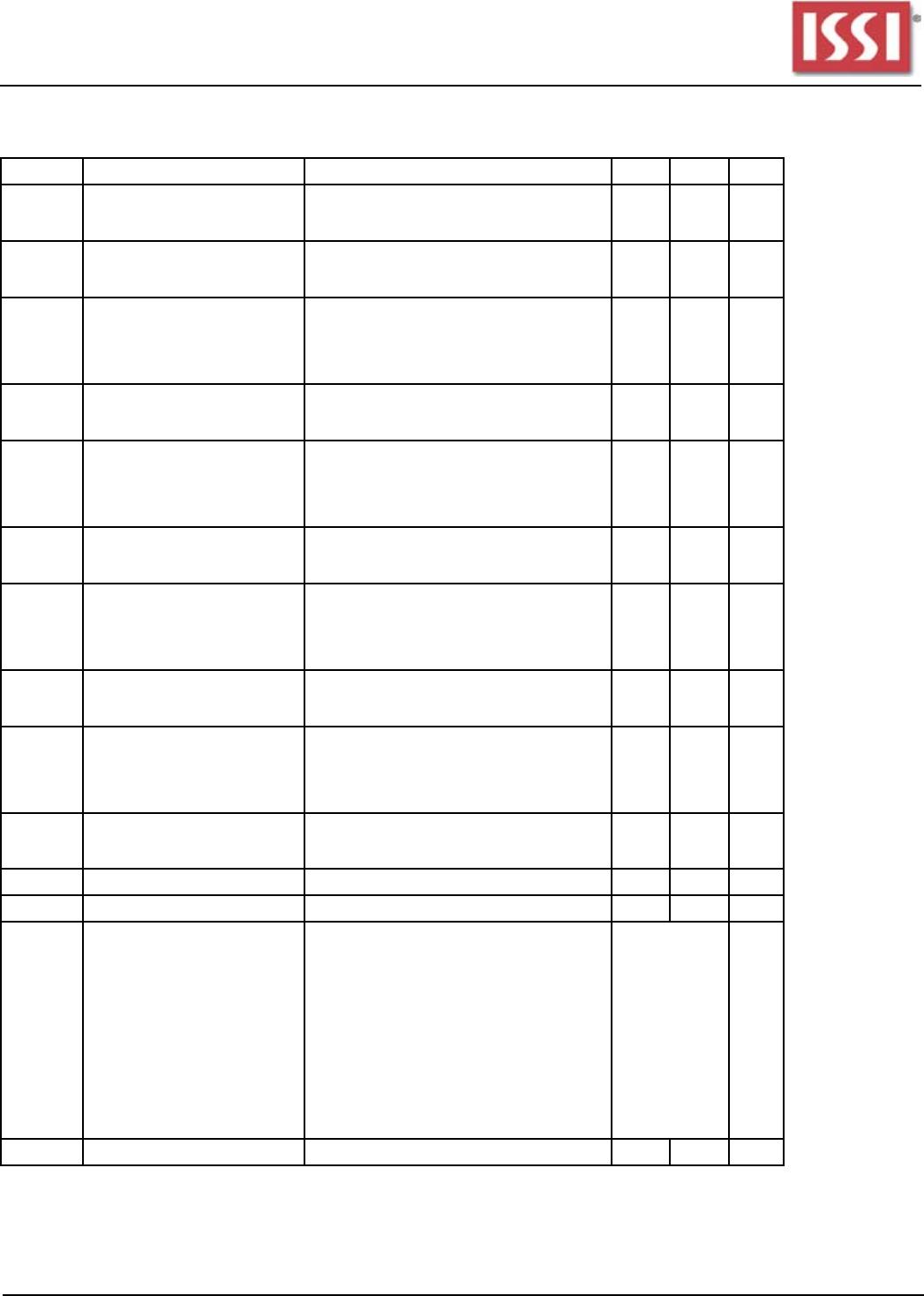

Symbol Parameter Test Condition –7 –10 Unit

I

d d 1

(1)

Operating Current One Bank Active, CL = 3, BL = 1,

tclK = tCLK(min), tRC = tRC(min)

85 75 mA

I

d d 2p

(4)

Precharge Standby Current

(In Power-Down Mode)

CKE ≤ V

i l (max), tCK = 15ns

CS ≥ V

d d - 0.2V

1 1 mA

I

d d 2p s

(4)

Precharge Standby Current

With Clock Stop

(In Power-Down Mode)

CKE ≤ V

i l (max), CLK ≤ Vi l (max)

CS ≥ V

d d - 0.2V

1 1 mA

I

d d 2n

(2)

Precharge Standby Current

(In Non Power-Down Mode)

CS ≥ Vd d - 0.2V, CKE ≥ Vi h (min)

tCK = 15 ns

35 35 mA

I

d d 2n s Precharge Standby Current

With Clock Stop

(In Non-Power Down Mode)

CS ≥ Vd d - 0.2V, CKE ≥ Vi h (min)

All Inputs Stable

20 20 mA

I

d d 3p

(2)

Active Standby Current

(In Power-Down Mode)

CKE ≤ Vi l (max), CS ≥ Vd d - 0.2V

tCK = 15 ns

2 2 mA

I

d d 3p s Active Standby Current

With Clock Stop

(In Power-Down Mode)

CKE ≤ V

i l (max), CLK ≤ Vi l (max)

CS ≥ V

d d - 0.2V

2 2 mA

I

d d 3n

(2)

Active Standby Current

(In Non Power-Down Mode)

CS ≥ Vd d - 0.2V, CKE ≥ Vi h (min)

tCK = 15 ns

40 40 mA

I

d d 3n s Active Standby Current

With Clock Stop

(In Non Power-Down Mode)

CS ≥ V

d d - 0.2V, CKE ≥ Vi h (min)

All Inputs Stable

25 25 mA

I

d d 4 Operating Current All Banks Active, BL = FULL, CL = 3

tCK = tCK(min)

110 80 mA

I

d d 5 Auto-Refresh Current tRC = tRC(min), tCLK = tCLK(min) 160 120 mA

I

d d 6 Self-Refresh Current CKE ≤ 0.2V 1.2 1.2 mA

I

d d 7 Self-Refresh: CKE = LOW;

t

c K = tc K (MIN); Address,

Control, and Data bus inputs

are stable

Full Array, 85

o

C

Full Array, 45

o

C

Half Array, 85

o

C

Half Array, 45

o

C

1/4th Array, 85

o

C

1/4th Array, 45

o

C

1/8th Array, 85

o

C

1/8th Array, 45

o

C

1/16th Array, 85

o

C

1/16th Array, 45

o

C

1200

800

1000

670

800

540

700

470

600

400

mA

I

z z

(3,4)

Deep Power Down Current CKE ≤ 0.2V 20 20 mA

DC ELECTRICAL CHARACTERISTICS VDD = 3.3V/2.5V (x8 and x16)

Notes:

1. I

d d (max) is specified at the output open condition.

2. Input signals are changed one time during 30ns.

3. Izz values shown are nominal at 25

o

C. Izz is not tested.

4. Tested after 500ms delay