8 Integrated Silicon Solution, Inc. - www.issi.com

Rev. A

10/22/09

IS42SM83200D / IS42SM16160D / IS42SM32800D

IS42RM83200D / IS42RM16160D / IS42RM32800D

Mobile SDRAM Functionality

ISSI’s 256Mb Mobile SDRAMs are pin compatible and have similar functionality with ISSI’s standard SDRAMs, but

offer lower operating voltages and power saving features. For detailed descriptions of pin functions, command truth

tables, functional truth tables, device operation as well as timing diagrams please refer to ISSI document “Mobile

Synchronous DRAM Device Operations & Timing Diagrams” listed at www.issi.com

REGISTER DEFINITION

Mode Register (MR) & Extended Mode Register (EMR)

There are two mode registers in the Mobile SDRAM; Mode Register (MR) and Extended Mode Register (EMR). The

Mode Register is discussed below, followed by the Extended Mode Register. The Mode Register is used to define

the specific mode of operation of the SDRAM. This definition includes the selection of burst length, a burst type, CAS

Latency, operating mode, and a write burst mode. The mode register is programmed via the LOAD MODE REGISTER

command and will retain the stored information until it is programmed again or the device loses power.

The EMR controls the functions beyond those controlled by the MR. These additional functions are special features

of the Mobile SDRAM. They include temperature-compensated self refresh (TCSR) control, partial-array self refresh

(PASR), and output drive strength. The EMR is programmed via the MODE REGISTER SET command with BA1

= 1 and BA0 = 0 and retains the stored information until it is programmed again or the device loses power. Not

programming the extended mode register upon initialization will result in default settings for the low-power features.

The extended mode will default with the temperature sensor enabled, full drive strength, and full array (all 4 banks)

refresh.

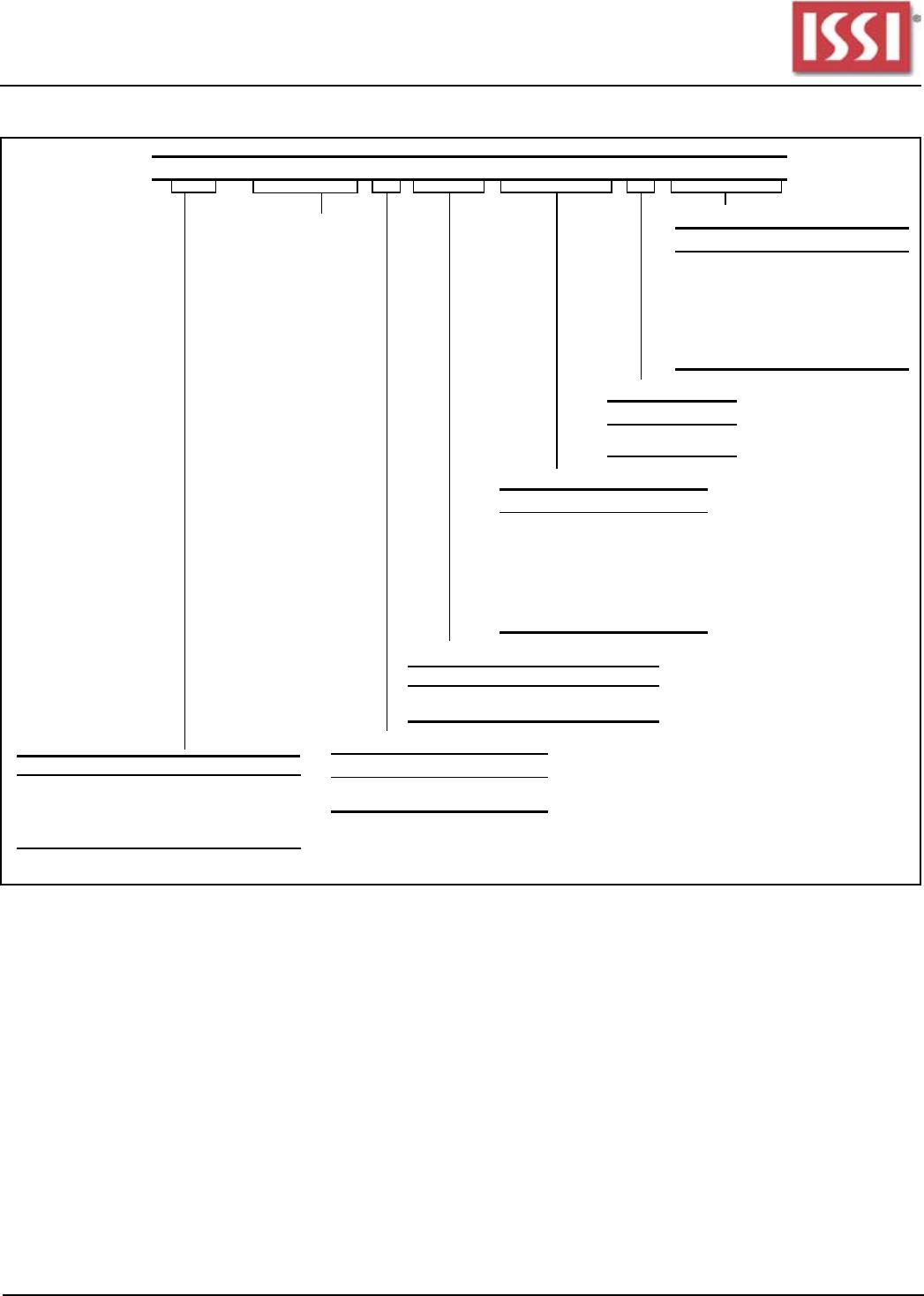

Mode Register Definition

The MR is used to define the specific mode of operation of the SDRAM. This definition includes the selection of a

burst length, a burst type, a CAS latency, an operating mode and a write burst mode, as shown in Figure MODE

REGISTER DEFINITION. The mode register is programmed via the LOAD MODE REGISTER command and will

retain the stored information until it is programmed again or the device loses power.

Mode register bits M0 - M2 specify the burst length, M3 specifies the type of burst (sequential or interleaved), M4 -

M6 specify the CAS latency, M7 and M8 specify the operating mode, M9 specifies the WRITE burst mode, and M10,

M11, and M12 are reserved for future use.

The mode register must be loaded when all banks are idle, and the controller must wait the specified time before

initiating the subsequent operation. Violating either of these requirements will result in unspecified operation.