14

FN8191.4

January 15, 2009

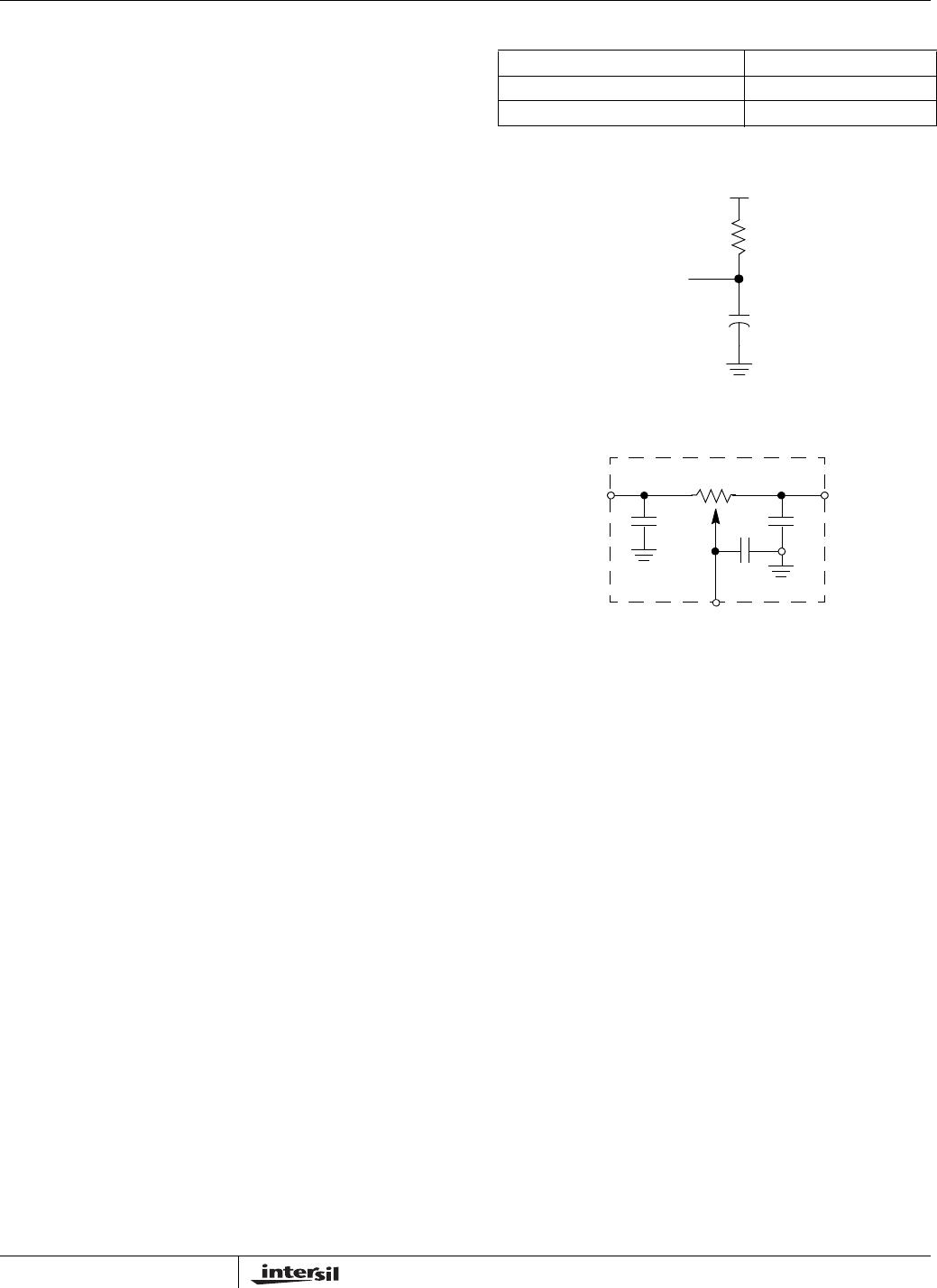

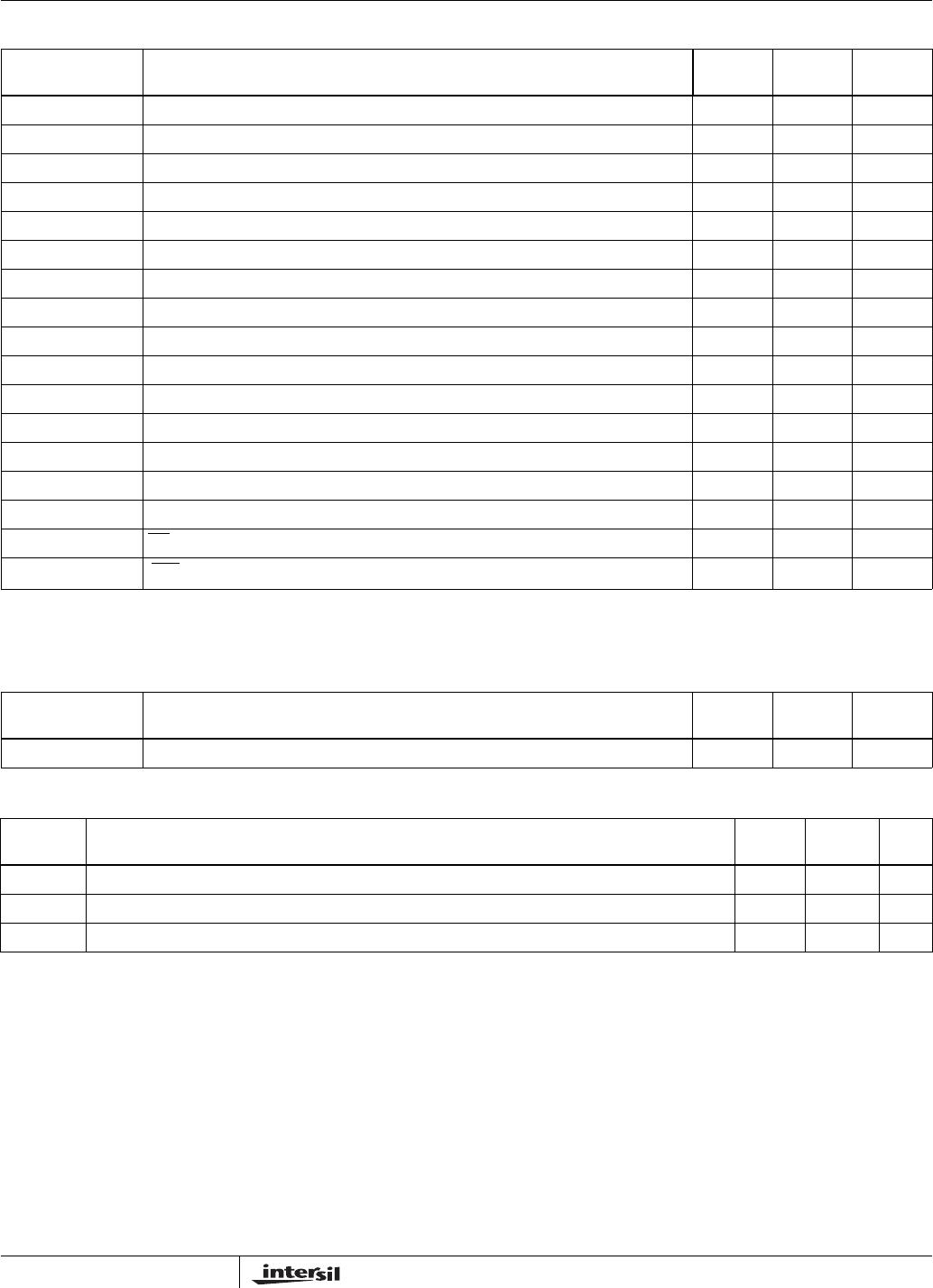

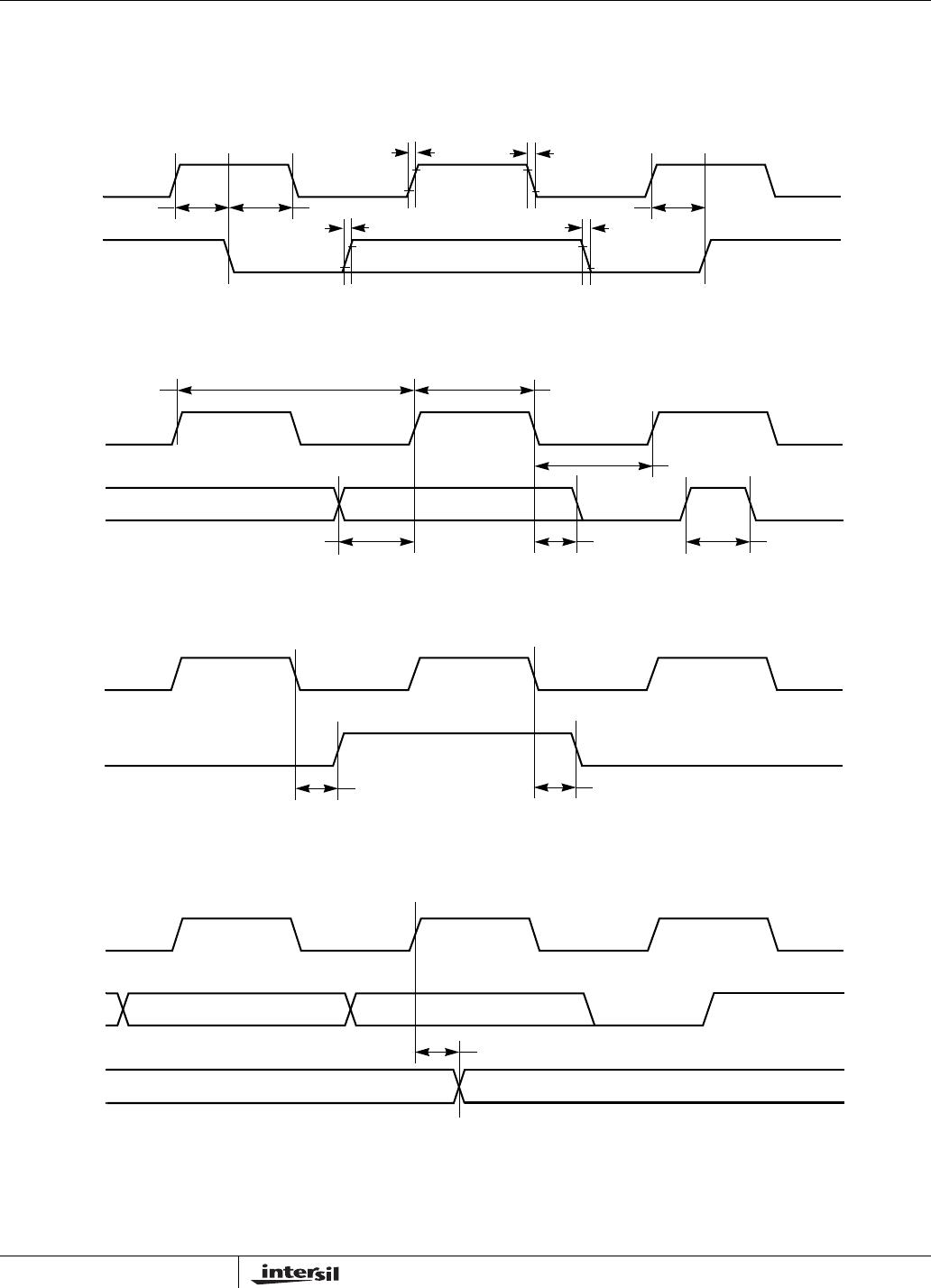

AC Timing (Over recommended operating condition)

HIGH-VOLTAGE WRITE CYCLE TIMING

XDCP TIMING

SYMBOL PARAMETER

MIN

(Note 5)

MAX

(Note 5) UNIT

f

SCL

Clock frequency 400 kHz

t

CYC

Clock cycle time 2500 ns

t

HIGH

Clock high time 600 ns

t

LOW

Clock low time 1300 ns

t

SU:STA

Start setup time 600 ns

t

HD:STA

Start hold time 600 ns

t

SU:STO

Stop setup time 600 ns

t

SU:DAT

SDA data input setup time 100 ns

t

HD:DAT

SDA data input hold time 30 ns

t

R (Note 7)

SCL and SDA rise time 300 ns

t

F (Note 7)

SCL and SDA fall time 300 ns

t

AA

SCL low to SDA data output valid time 900 ns

t

DH

SDA Data output hold time 50 ns

T

I

Noise suppression time constant at SCL and SDA inputs 50 ns

t

BUF

Bus free time (prior to any transmission) 1300 ns

t

SU:WPA

WP, A0, A1, A2 and A3 setup time 0 ns

t

HD:WPA

WP, A0, A1, A2 and A3 hold time

0ns

NOTES:

7. This parameter is not production tested. Parameter established by characterization.

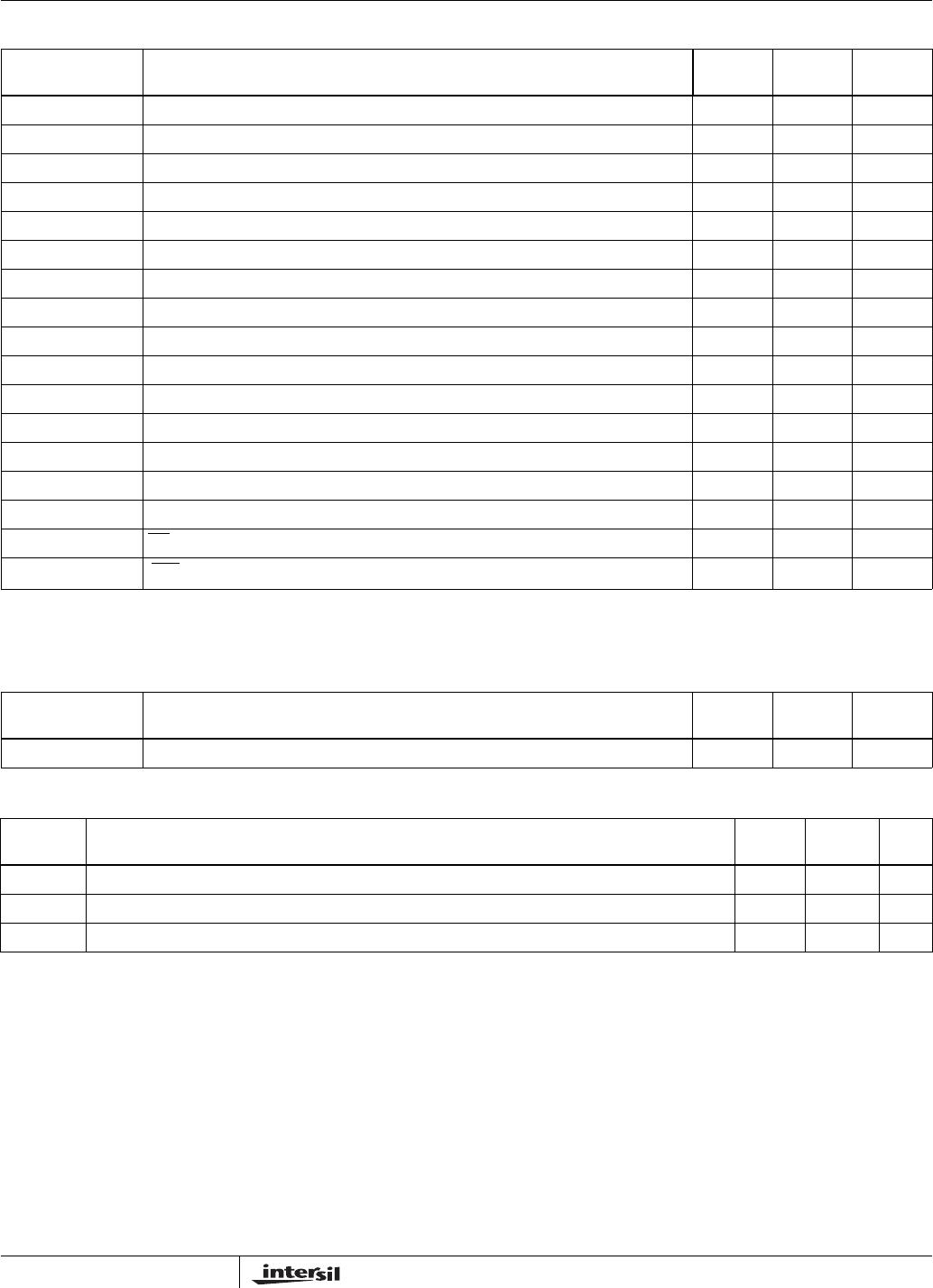

SYMBOL PARAMETER

TYP.

(Note 4)

MAX.

(Note 6) UNIT

t

WR

High-voltage write cycle time (store instructions) 5 10 ms

SYMBOL PARAMETER

MIN.

(Note 5)

MAX.

(Note 6) UNIT

t

WRPO

Wiper response time after the third (last) power supply is stable 10 µs

t

WRL

Wiper response time after instruction issued (all load instructions) 10 µs

t

WRID

Wiper response time from an active SCL/SCK edge (increment/decrement instruction) 10 µs

X9408