NCL30051

www.onsemi.com

10

PFC Output Capacitor - Cbulk

The bulk capacitor is one of the most critical components

in the PFC design. High value, high voltage capacitors are

expensive and take up a large space. In traditional PFC

applications, the voltage rating of this capacitor is about

450 V (some designers cut it to 420 V for cost savings), but

for 277 Vac lighting applications, 450 V rating is not

sufficient. As shown in the table above, if the output

voltage is allowed to vary, the bulk voltage can go even

higher. Availability of bulk capacitors above 450 V is

limited. One solution is to take two capacitors and put them

in series. The effective value of two series capacitors is

lower, but for low-medium power applications, this should

not be a big issue. For 600 V maximum bulk voltage, two

400 V capacitors need to be used, but for 90−135 Vac only

applications, lower rated capacitors can be used. When

putting capacitors in series, it is required to have a parallel

high value resistor pair in order to ensure voltage sharing.

The effective bulk capacitance value also depends on the

application requirements. Normal rule of thumb for

traditional PFC circuits is to use around 1 mF/W to achieve

desired hold-up time and ripple performance. In this

approach, due to absence of a regulated second stage, it

may be prudent to increase the capacitance value if low

ripple or fast transient response is required. Another factor

in selecting the capacitor is that it handles high ripple

current due to the CrM topology implemented here. The

equations for ripple current through the capacitor are

derived in ON Semiconductor application note AND8123

and should be used to determine that the selected capacitor

can handle the ripple current without overheating or

lifetime degradation.

PFC Diode (D

BST

)

The PFC diode provides the rectification function and

has to be rated above the peak value of Vbulk. In the CrM

operation, with the diode current going to zero every cycle

prior to its turn-off, the reverse recovery is not that

prominent and an ultrafast diode can be used. In addition,

there is little or no overshoot caused by the reverse

recovery, so the FET voltage is also well contained. In most

cases a 600 V diode is sufficient depending on the derating

criteria.

PFC Switch (Q

BST

)

Typically, the PFC switch is a MOSFET rated anywhere

from 500 V to 650 V. Better commercial availability of

higher voltage rated FETs in recent years has meant that the

QBST is not a major constraint in implementation of

variable Vbulk approach offered by NCL30051. However,

depending on derating guidelines and practices, the 600 V

rating of the FET may not be sufficient. In that case, a

higher voltage FET is required.

PFC Inductor (L

BST

)

The PFC inductor is designed using the standard CrM

design equations. When the output voltage goes up from

390 V to 540 V, there is about 20% increase in value of

inductance required. Thus, variation in PFC voltage results

in higher boost inductor value and size (and/or higher

ripple current when the output voltage is higher).

HBR Converter Design

The half-bridge resonant converter utilizes an LLC

resonant circuit to achieve the ZVS of the primary switches

and also to reduce the transition losses in the secondary.

Additionally, this circuit offers a major benefit wherein the

output inductor can be eliminated.

In traditional LLC approaches, when the second stage

converter is regulated, the switching frequency of the HBR

converter has to be varied to respond to load or line

changes. As a result, operation near the resonant frequency

is not always guaranteed and the efficiency takes a hit.

Also, varying the frequency imposes additional design

burden on the designer to ensure that the control circuit is

stable and provides desired results over the full load and

line range. The feedback design and loop closure is more

challenging in this type of converter.

By keeping a constant switching frequency, not only is

the control circuit simplified, the magnetics design also

becomes easier. The transformer size can be reduced as it

is designed for a single frequency and full optimization is

available. Studies have shown that this approach leads to

about 25-40% reduction in total magnetics area-product.

Other design considerations for the LLC resonant

converter remain the same as given in ON Semiconductor

application note AND8311 and are not repeated here.

The power conversion architecture of the NCL30051 is

ideal for many LED Lighting applications since it provides

higher efficiency and power factor correction. Since

hold-up time and output ripple are not major considerations

in these applications, NCL30051 fits in very well. This

means that it is ideal for fixed output voltage LED power

supplies (ex: 24 Vdc and 48 Vdc) as well as constant current

schemes where the output voltage varies depending on the

number of LEDs and the variation of the LED forward

voltage. This topology is best suited for applications where

the output voltage variation is constrained to a ratio of

about 1.5 for designs that require operation at 230 Vac.

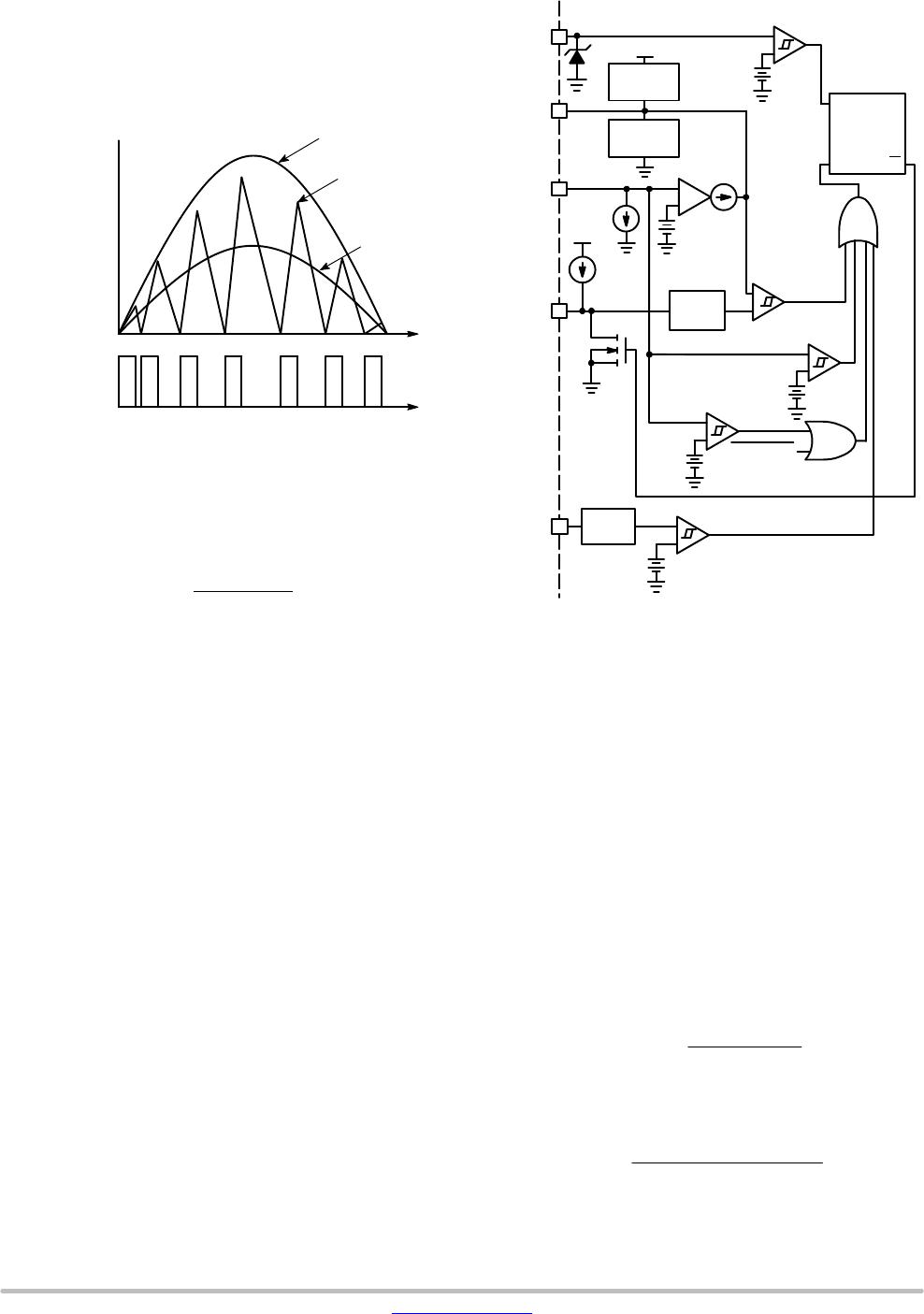

Supply Sequencing

The error amplifier of the PFC controller is enabled once

V

CC

reaches V

CC(on)

and the PFB voltage exceeds

V

PUVP(high)

, typically 290 mV. Once enabled, the PControl

voltage starts rising and when it exceeds V

EA(OL)

and V

CC

is above V

CC(enable)

, the first PFC drive pulse is generated.

The half-bridge driver is enabled after the first PFC drive

pulse is generated. This ensures a monotonic output

voltage rise as the input voltage to the half bridge stage is

regulated.

In the event that V

CC

falls below V

CC(enable)

before the

control voltage exceeds V

EA(OL)

, the error amplifier will

remain on and V

CC

will fall to Vcc

(OFF)

at which time the

HV startup circuit will be enabled and a new startup

sequence will be initiated.