NCL30051

www.onsemi.com

14

V

PFC

+ V

PREF

@

R

1

) R

2

R

2

) I

PFB

@ R

1

(eq. 5)

A transconductance amplifier has a voltage−to−current

gain, gm. That is, the output current is controlled by the

differential input voltage. The NCL30051 amplifier has a

typical gm of 95 mS. The PControl pin provides access to the

amplifier output for compensation. The compensation

network is ground referenced allowing the PFC feedback

signal to be used to detect an overvoltage condition.

The compensation network on the PControl pin is

selected to filter the bulk voltage ripple such that a constant

control voltage is maintained across the ac line cycle. A

capacitor between the PControl pin and ground sets a pole.

A pole at or below 20 Hz is enough to filter the ripple

voltage for a 50 and 60 Hz system. The low frequency pole,

f

p

, of the system is calculated using Equation 6.

f

p

+

gm

2pC

PControl

(eq. 6)

where, C

PControl

is the capacitor on the PControl pin to

ground.

A key feature to using a transconductance type amplifier,

is that the input is allowed to move independently with respect

to the output, since the compensation capacitor is connected

to ground. This allows dual usage of the feedback pin by the

error amplifier and by the overvoltage comparator.

PFC Undervoltage

The NCL30051 safely disables the controller if the PFB

pin is left open. An undervoltage detector disables the

controller if the voltage on the PFB pin is below

V

PUVP(low)

, typically 0.23 V. A 1.2 mA (typical) pull down

current source, I

PFB

, ensures V

PFB

falls below V

PUVP(low)

if the PFB pin is floating. The PFB pull down current source

affects the PFC output voltage regulation setpoint.

PFC Overvoltage

An overvoltage detector monitors the PFC feedback

voltage and disables the PFC driver if an overvoltage

condition is detected. This is set internal to the IC at 5%

above the nominal setting of the PFC voltage If an OVP

event is detected, drive pulses are suppressed until the over

voltage condition is removed. The overvoltage detector

tolerance is better than ±2%. The overvoltage detector

threshold, V

POVP

, is the midpoint between the PFC driver

disable and enable thresholds. The overvoltage comparator

hysteresis is the voltage difference between the disable and

enable thresholds. An overvoltage condition is detected

once V

PFB

exceeds V

POVP

by half of V

POVP(HYS)

. The

controller is re-enabled once V

PFB

drops below V

POVP

by

half of V

POVP(HYS)

.

PFC Overcurrent

The PFC current is monitored by means of an overcurrent

detector. The PCS pin provides access to the overcurrent

detector. The PFC drive pulse is terminated if the voltage

on the PCS pin exceeds the overcurrent threshold,

V

PCS(ILIM)

. This comparison is done on a cycle by cycle

basis. The overcurrent threshold is typically 0.84 V.

The current sense signal is prone to leading edge spikes

caused by the power switch transitions. The NCL30051 has

leading edge blanking circuitry that blocks out the first

110 ns (typical) of each current pulse.

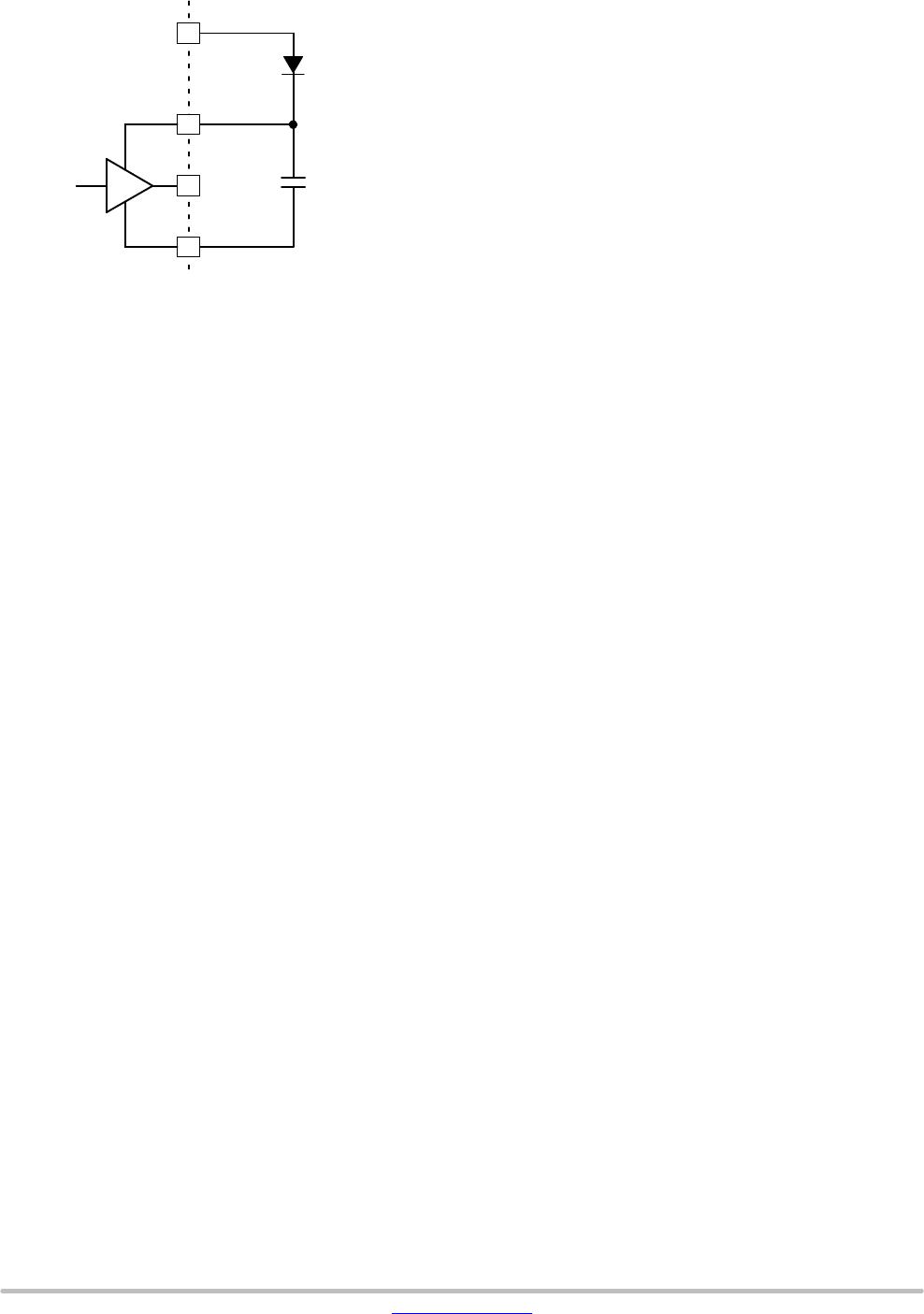

PFC Driver

The PFC driver source and sink impedances are typically

60 and 15 W, respectively. Depending on the external

MOSFET gate charge requirements, an external driver may

be needed to drive the PFC power switch. A driver such as

the one shown in Figure 9 can be easily implemented using

small bipolar transistors.

Figure 9. External Driver

To gate

of MOSFET

VCC

xDRVx

Half−Bridge Driver

The half−bridge stage operates at a fixed 50% duty ratio.

The oscillator frequency is divided by two before it is

applied to the half−bridge controller.

The half−bridge controller has a low side driver,

HDRVlo, and a 600 V high side driver, HDRVhi. The built

in high voltage driver eliminates the need for an external

transformer or dedicated driver. A built−in delay between

each drive transition eliminates the risk of cross

conduction. The delay is typically 785 ns. The typical duty

ratio of each half−bridge driver is 48%.

The high side driver is connected between the HBoost

and the HVS pins as shown in Figure 10.