LTC4359

7

Rev D

For more information www.analog.com

Blocking diodes are commonly placed in series with supply

inputs for the purpose of ORing redundant power sources

and protecting against supply reversal. The LTC4359

replaces diodes in these applications with a MOSFET to

reduce both the voltage drop and power loss associated

with a passive solution. The curve shown on page 1 illus

-

trates the dramatic improvement in power loss achieved in

a practical application. This represents significant savings

in board area by greatly reducing power dissipation in the

pass device. At low input voltages, the improvement in

forward voltage loss is readily appreciated where head-

room is tight, as shown in Figure2.

The LTC4359 operates from 4V to 80V and withstands

an absolute maximum range of –40V to 100V without

damage. In automotive applications the LTC4359 operates

through load dump, cold crank and two-battery jumps,

and it survives reverse battery connections while also

protecting the load.

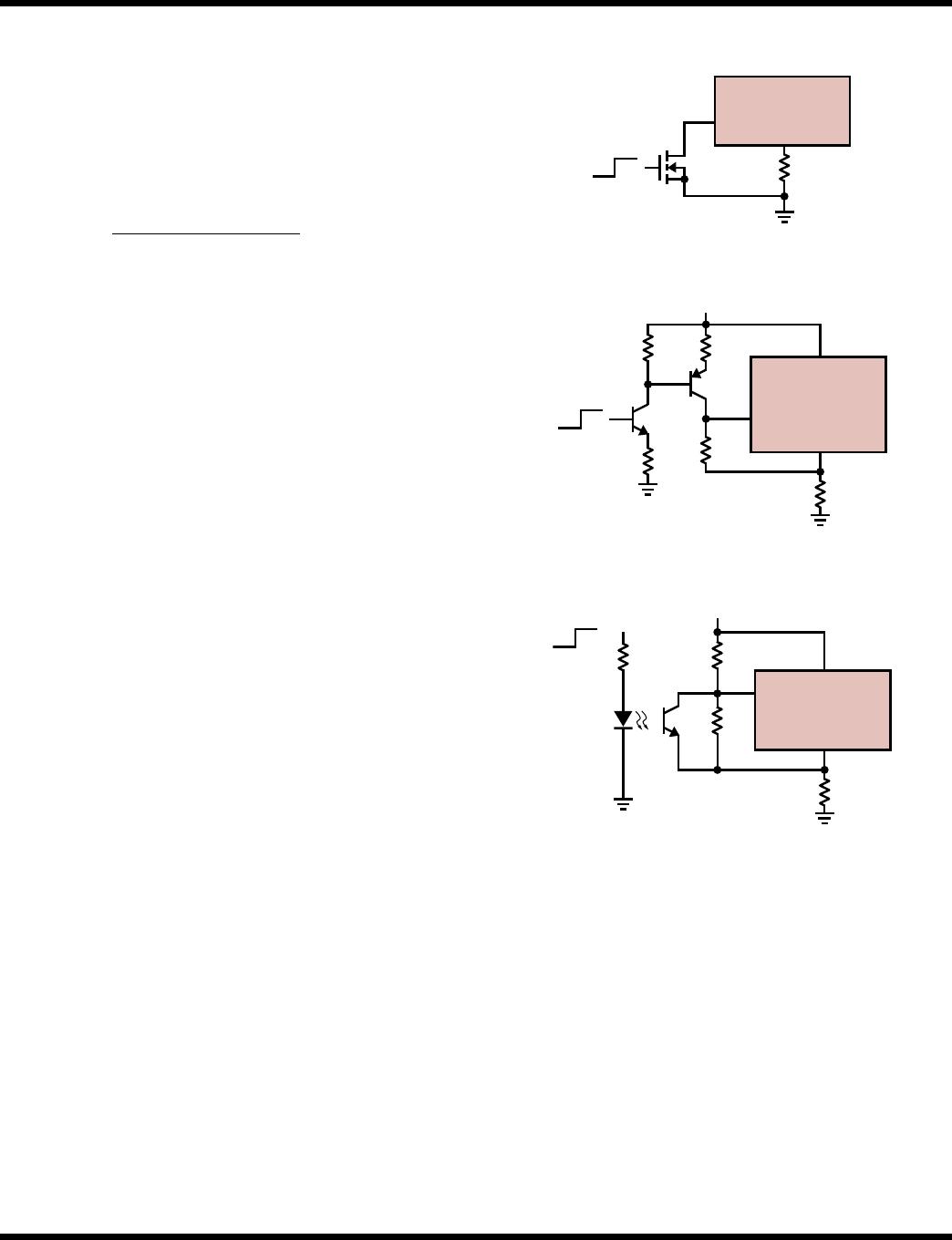

A 12V/20A ideal diode application is shown in Figure1.

Several external components are included in addition to

the MOSFET, Q1. Ideal diodes, like their nonideal coun

-

terparts, exhibit a behavior known as reverse recovery.

In combination with parasitic or intentionally introduced

inductances, reverse recovery spikes may be generated by

an ideal diode during commutation. D1, D2 and R1 protect

against these spikes which might otherwise exceed the

LTC4359’s –40V to 100V survival rating. C

OUT

also plays

a role in absorbing reverse recovery energy. Spikes and

protection schemes are discussed in detail in the Input

Short-Circuit Faults section.

APPLICATIONS INFORMATION

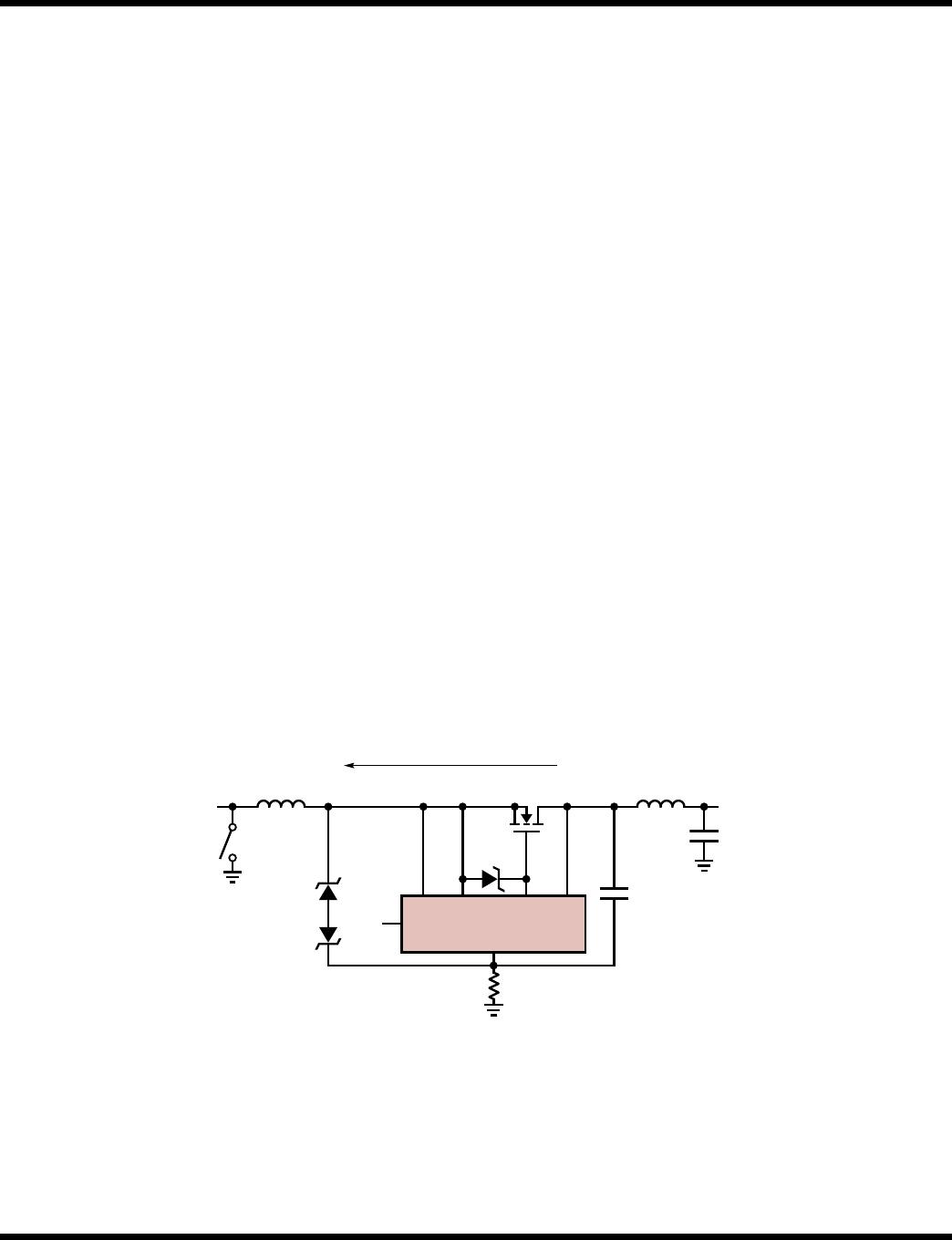

It is important to note that the SHDN pin, while disabling

the LTC4359 and reducing its current consumption to

9µA, does not disconnect the load from the input since

Q1’s body diode is ever-present. A second MOSFET is

required for load switching applications.

MOSFET Selection

All

load current passes through an external MOSFET, Q1.

The important characteristics of the MOSFET are on-

resistance, R

DS(ON)

, the maximum drain-source voltage,

BV

DSS

, and the gate threshold voltage V

GS(TH)

.

Gate drive is compatible with 4.5V logic-level MOSFETs

over the entire operating range of 4V to 80V. In applications

above 8V, standard 10V threshold MOSFETs may be used.

An internal clamp limits the gate drive to 15V maximum

between the GATE and SOURCE pins. For 24V and higher

applications, an external Zener clamp (D4) must be added

between GATE and SOURCE to not exceed the MOSFET’s

V

GS(MAX)

during input shorts.

The maximum allowable drain-source voltage, BV

DSS

, must

be higher than the power supply voltage. If the input is

grounded, the full supply voltage will appear across the

MOSFET. If the input is reversed, and the output is held

up by a charged capacitor, battery or power supply, the

sum of the input and output voltages will appear across

the MOSFET and BV

DSS

> OUT + |V

IN

|.

Figure1. 12V/20A Ideal Diode with Reverse Input Protection

4359 F01

LTC4359

V

SS

SHDN

IN SOURCE

BSC028N06NS

C

OUT

47nF

R1

1k

GATE

D1

SMAT70A

70V

D2

SMAJ24A

24V

V

IN

V

12V

20A

OUT

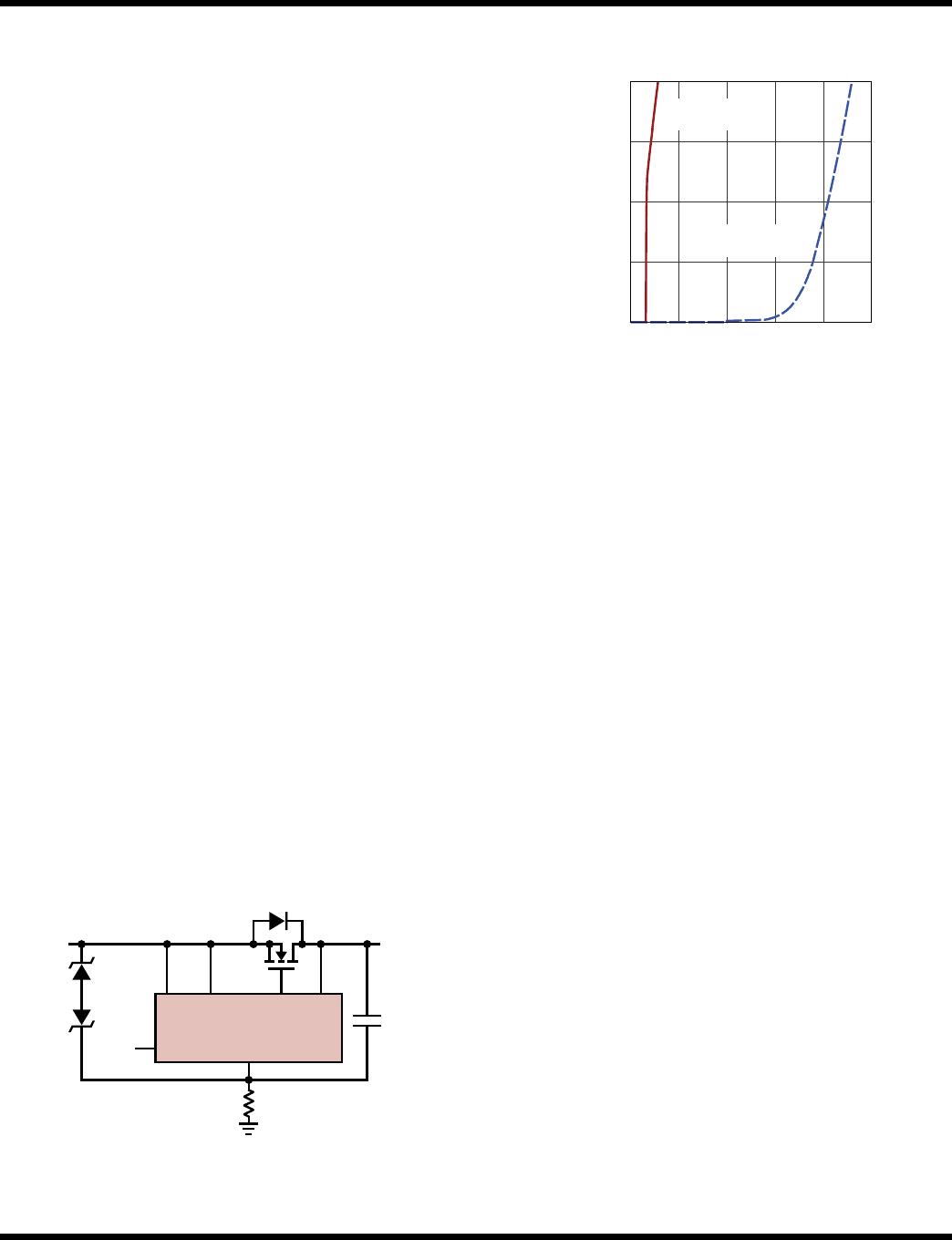

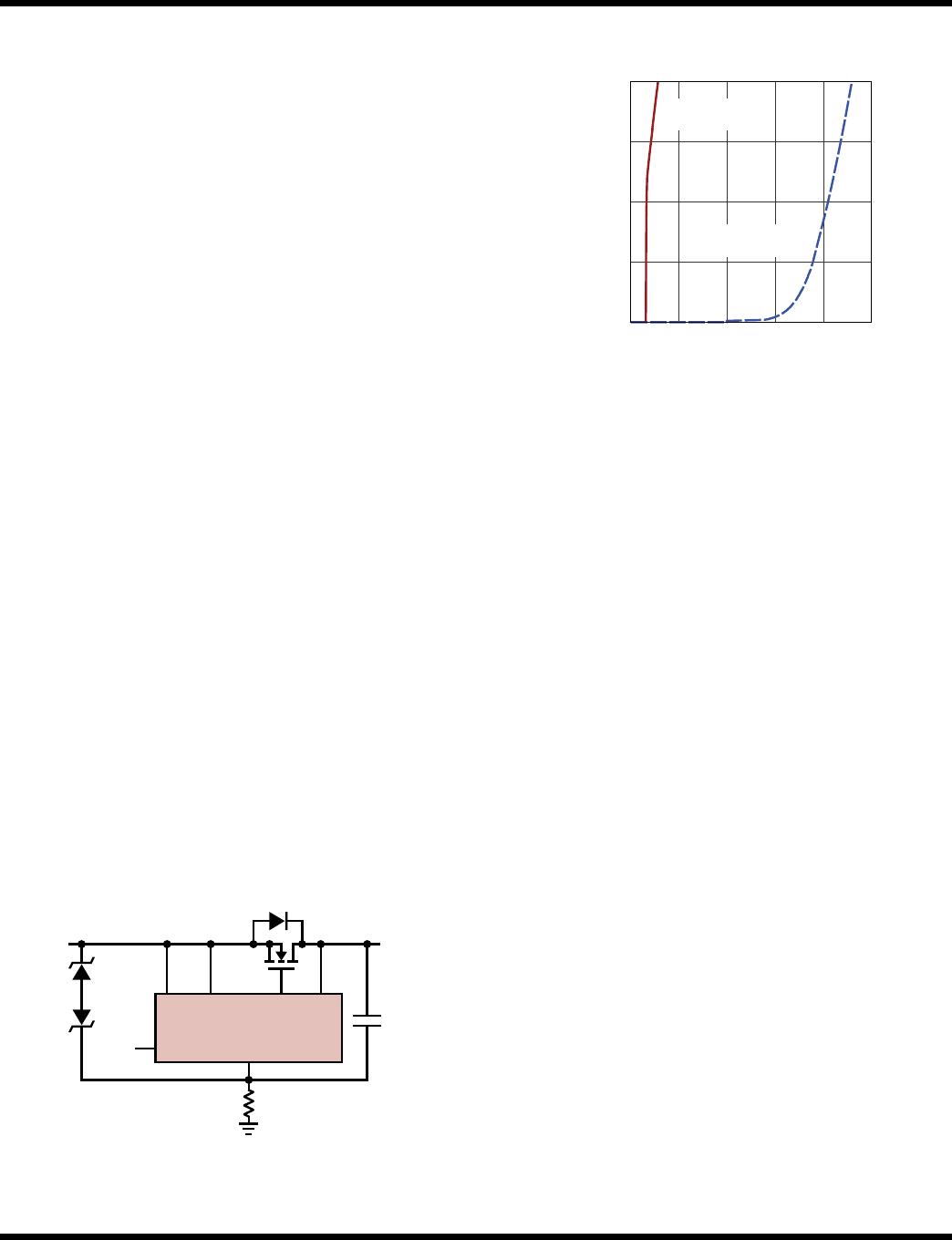

Figure2. Forward Voltage Drop Comparison

Between MOSFET and Schottky Diode

VOLTAGE (V)

0

10

15

5

0

0.20.1

0.3

0.4

MOSFET

(BSC028N06NS)

SCHOTTKY DIODE

(SBG2040CT)