Using a byte descriptive notation, the reset command

can be viewed as the following sequence, within the

same CS cycle:

SDI: <0x04>

Features and Settings

Values and parameters are set through registers in the

MAX7057 that are addressable through the SPI. These

registers contain bits that either turn functions on and

off or program numerical settings. The following set-

tings are controlled through the SPI.

Variable Capacitor

The internal variable shunt capacitor, which is instru-

mental in matching the PA to the antenna, is controlled

by setting 5 bits in the configuration 0 register. This

allows for 32 levels of shunt capacitance control. Since

the control of these 5 bits is independent of the other

settings, any capacitance value can be chosen at any

frequency, making it possible to maintain maximum

transmitter efficiency while moving rapidly from one fre-

quency to another.

Clock Output

The MAX7057 has a buffered clock output that can

serve as a clock for a microprocessor. The divide ratio

is set through the configuration 0 register (see Tables 5

and 6). The divide settings are 1 (no division), 2, 4, 8, or

16; the original undivided frequency is based on the

reference frequency generated by the external crystal.

The buffered clock output is available at GPO when

enabled by setting the configuration 1 register (see

Tables 2, 3, 15, and 16).

Mode Select and Crystal Shutdown

The transmission mode is selected by writing to a regis-

ter. The default mode is ASK and the mode can be

changed to FSK by writing a 1 to the mode bit in the

control register. This register is also used to keep the

crystal circuit powered up in the shutdown mode.

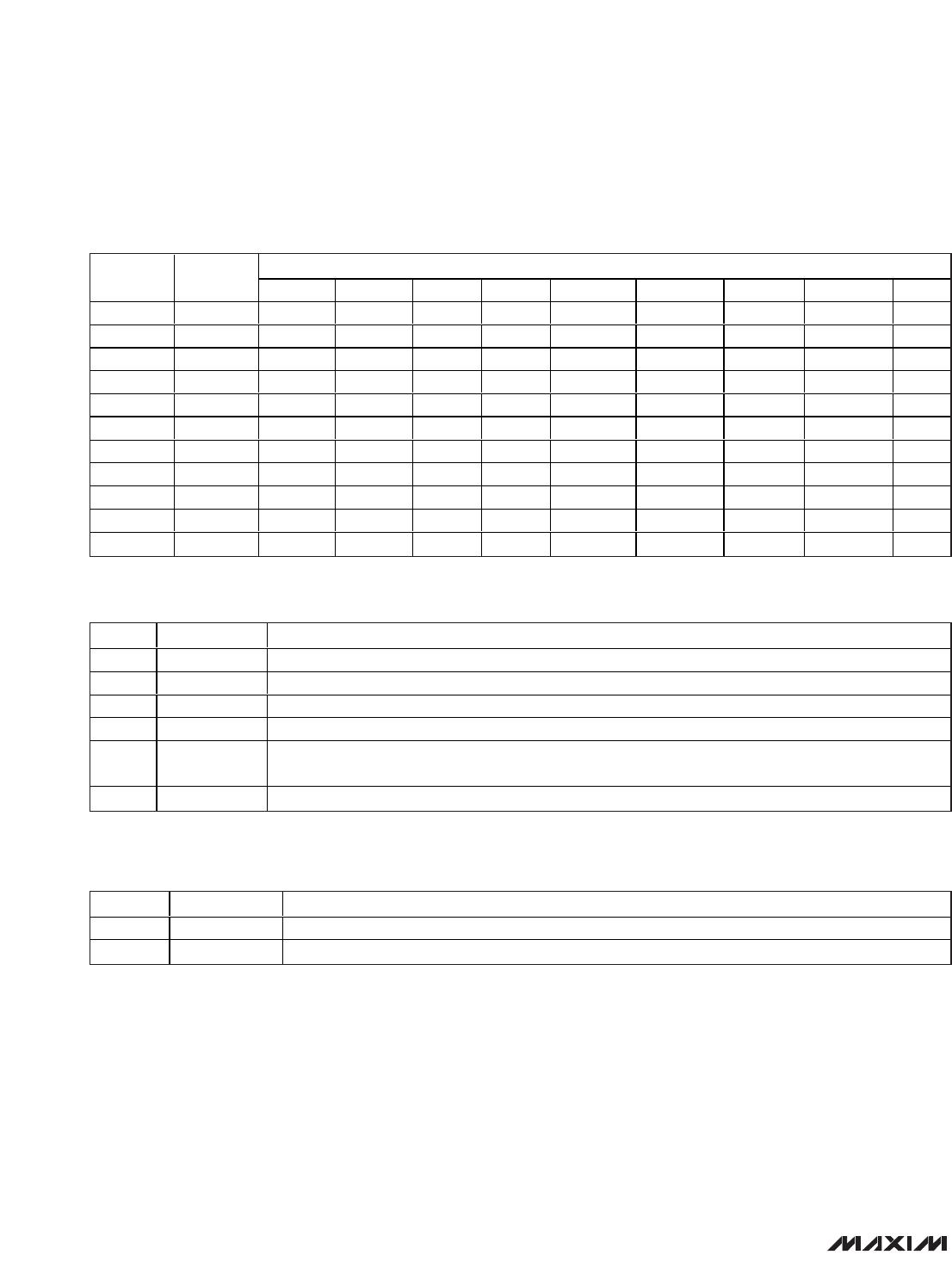

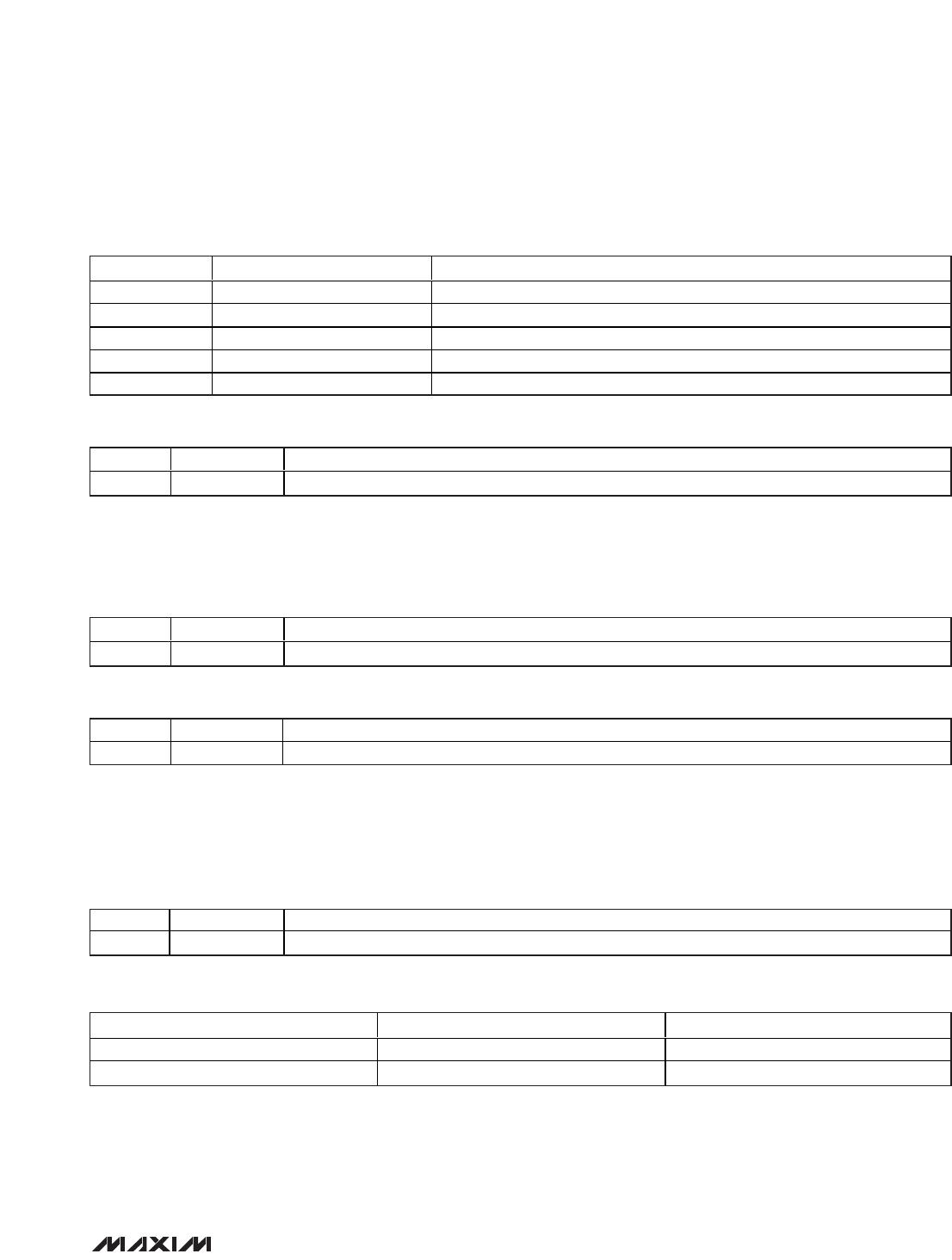

Registers

The following tables provide information on the

MAX7057 registers.

MAX7057

300MHz to 450MHz Frequency-Programmable

ASK/FSK Transmitter

______________________________________________________________________________________ 13

Control register. Controls the mode (ASK/FSK), crystal clock output, envelope-shaping, PLL

bandwidth, and SPI enable.

Configuration 0 register. Controls the capacitance at the PA output and clock output

frequency divider.

Low-frequency 1 register (upper byte). Sets the low frequency in FSK transmission, or

carrier frequency in ASK transmission.

Low-frequency 0 register (lower byte). Sets the low frequency in FSK transmission, or carrier

frequency in ASK transmission.