LTC3555/LTC3555-X

19

3555fe

For more information www.linear.com/LTC3555

1022 times the current in the PROG pin. The program

resistor and the charge current are calculated using the

following equations:

R

PROG

=

I

, I

CHG

=

R

In either the constant-current or constant-voltage charging

modes, the voltage at the PROG pin will be proportional to

the actual charge current delivered to the battery. There-

fore, the actual charge current can be determined at any

time by monitoring the PROG pin voltage and using the

following equation:

I

BAT

=

PROG

R

• 1022

In many cases, the actual battery charge current, I

BAT

, will

be lower than I

CHG

due to limited input power available

and prioritization with the system load drawn from V

OUT

.

Charge Status Indication

The CHRG pin indicates the status of the battery charger.

Four possible states are represented by CHRG which in-

clude charging, not charging, unresponsive battery, and

battery temperature out of range.

The signal at the CHRG pin can be easily recognized as

one of the above four states by either a human or a mi-

croprocessor. An open-drain output, the CHRG pin can

drive an indicator LED through a current limiting resistor

for human interfacing or simply a pull-up resistor for

microprocessor interfacing.

To make the CHRG pin easily recognized by both humans

and microprocessors, the pin is either low for charging,

high for not charging, or it is switched at high frequency

(35kHz) to indicate the two possible faults, unresponsive

battery and battery temperature out of range.

When charging begins, CHRG is pulled low and remains

low for the duration of a normal charge cycle. When

charging is complete, i.e., the BAT pin reaches the float

voltage and the charge current has dropped to one tenth

of the programmed value, the CHRG pin is released (Hi-Z).

If a fault occurs, the pin is switched at 35kHz. While

switching, its duty cycle is modulated between a low

and high value at a very low frequency. The low and high

duty cycles are disparate enough to make an LED appear

to be on or off thus giving the appearance of “blinking”.

Each of the two faults has its own unique “blink” rate for

human recognition as well as two unique duty cycles for

machine recognition.

The CHRG pin does not respond to the C/10 threshold if

the LTC3555 family is in V

BUS

current limit. This prevents

false end-of-charge indications due to insufficient power

available to the battery charger.

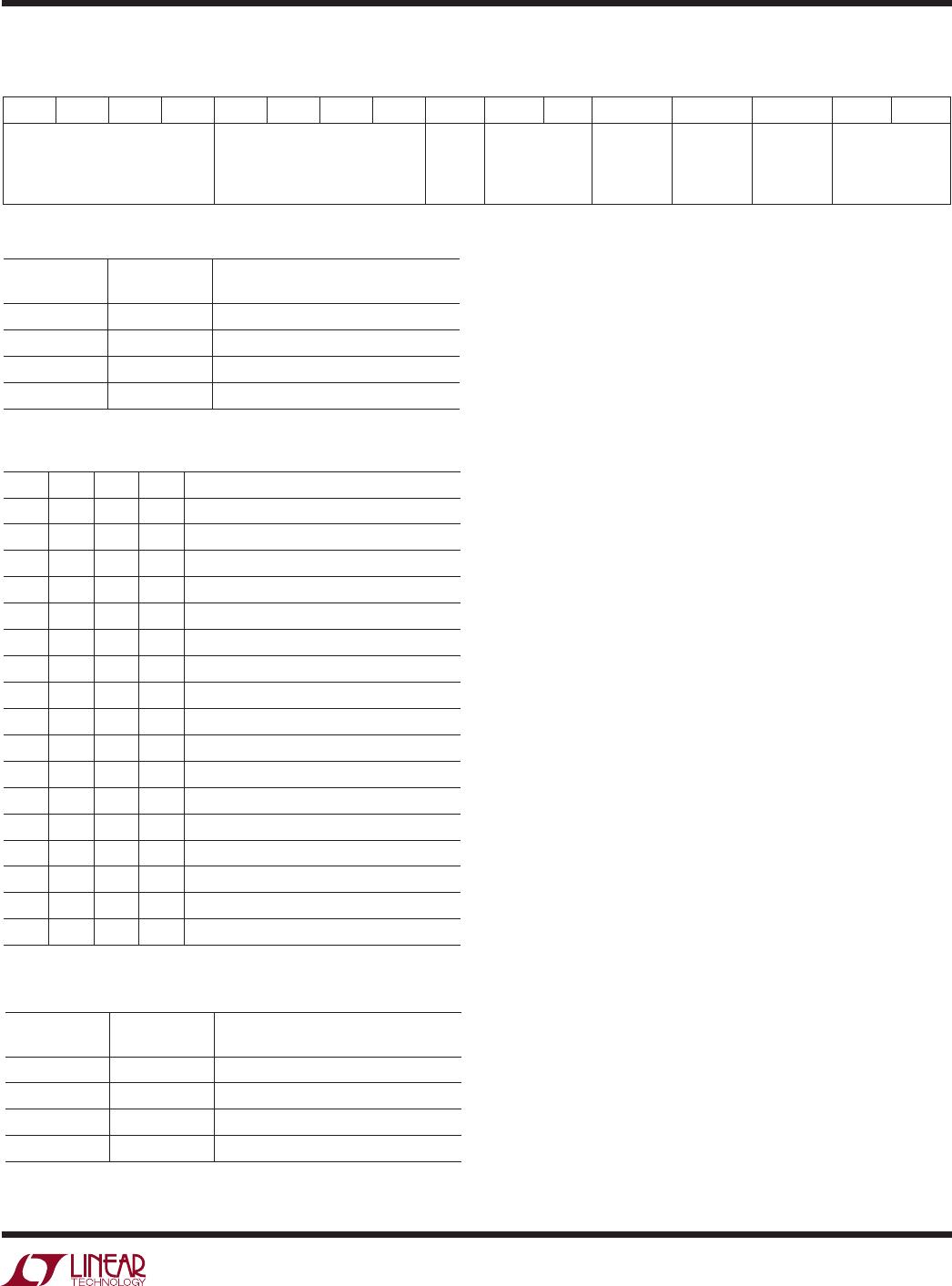

Table 1 illustrates the four possible states of the CHRG

pin when the battery charger is active.

Table 1. CHRG Signal

STATUS

FREQUENCY

MODULATION

(BLINK) FREQUENCY

DUTY CYCLES

Charging 0Hz 0Hz (Lo-Z) 100%

Not Charging 0Hz 0Hz (Hi-Z) 0%

NTC Fault 35kHz 1.5Hz at 50% 6.25% to 93.75%

Bad Battery 35kHz 6.1Hz at 50% 12.5% to 87.5%

An NTC fault is represented by a 35kHz pulse train whose

duty cycle varies between 6.25% and 93.75% at a 1.5Hz

rate. A human will easily recognize the 1.5Hz rate as a

“slow” blinking which indicates the out-of-range battery

temperature while a microprocessor will be able to decode

either the 6.25% or 93.75% duty cycles as an NTC fault.

If a battery is found to be unresponsive to charging (i.e.,

its voltage remains below 2.85V for 1/2 hour), the CHRG

pin gives the battery fault indication. For this fault, a human

would easily recognize the frantic 6.1Hz “fast” blink of the

LED while a microprocessor would be able to decode either

the 12.5% or 87.5% duty cycles as a bad battery fault.

Note that the LTC3555 family is a three terminal PowerPath

product where system load is always prioritized over battery

charging. Due to excessive system load, there may not be

sufficient power to charge the battery beyond the trickle

charge threshold voltage within the bad battery timeout

period. In this case, the battery charger will falsely indicate

a bad battery. System software may then reduce the load

and reset the battery charger to try again.

Although very improbable, it is possible that a duty cycle

reading could be taken at the bright-dim transition (low

duty cycle to high duty cycle). When this happens the

OPERATION