LTC3555/LTC3555-X

29

3555fe

For more information www.linear.com/LTC3555

By setting R

NOM

equal to R25, the above equations result

in α

HOT

= 0.536 and α

COLD

= 3.25. Referencing these ratios

to the Vishay Resistance-Temperature Curve 1 chart gives

a hot trip point of about 40°C and a cold trip point of about

0°C. The difference between the hot and cold trip points

is approximately 40°C.

By using a bias resistor, R

NOM

, different in value from R25,

the hot and cold trip points can be moved in either direction.

The temperature span will change somewhat due to the non-

linear behavior of the thermistor. The following equations can

be used to easily calculate a new value for the bias resistor:

R

NOM

=

HOT

0.536

• R25

R

NOM

=

α

COLD

• R25

where α

HOT

and α

COLD

are the resistance ratios at the

desired

hot and cold trip points. Note that these equations

are linked. Therefore, only one of the two trip points can

be chosen, the other is determined by the default ratios

designed in the IC. Consider an example where a 60°C

hot trip point is desired.

From the Vishay Curve 1 R-T characteristics, α

HOT

is 0.2488

at 60°C. Using the above equation, R

NOM

should be set to

4.64k. With this value of R

NOM

, the cold trip point is about

16°C. Notice that the span is now 44°C rather than the

previous 40°C. This is due to the decrease in “temperature

gain” of the thermistor as absolute temperature increases.

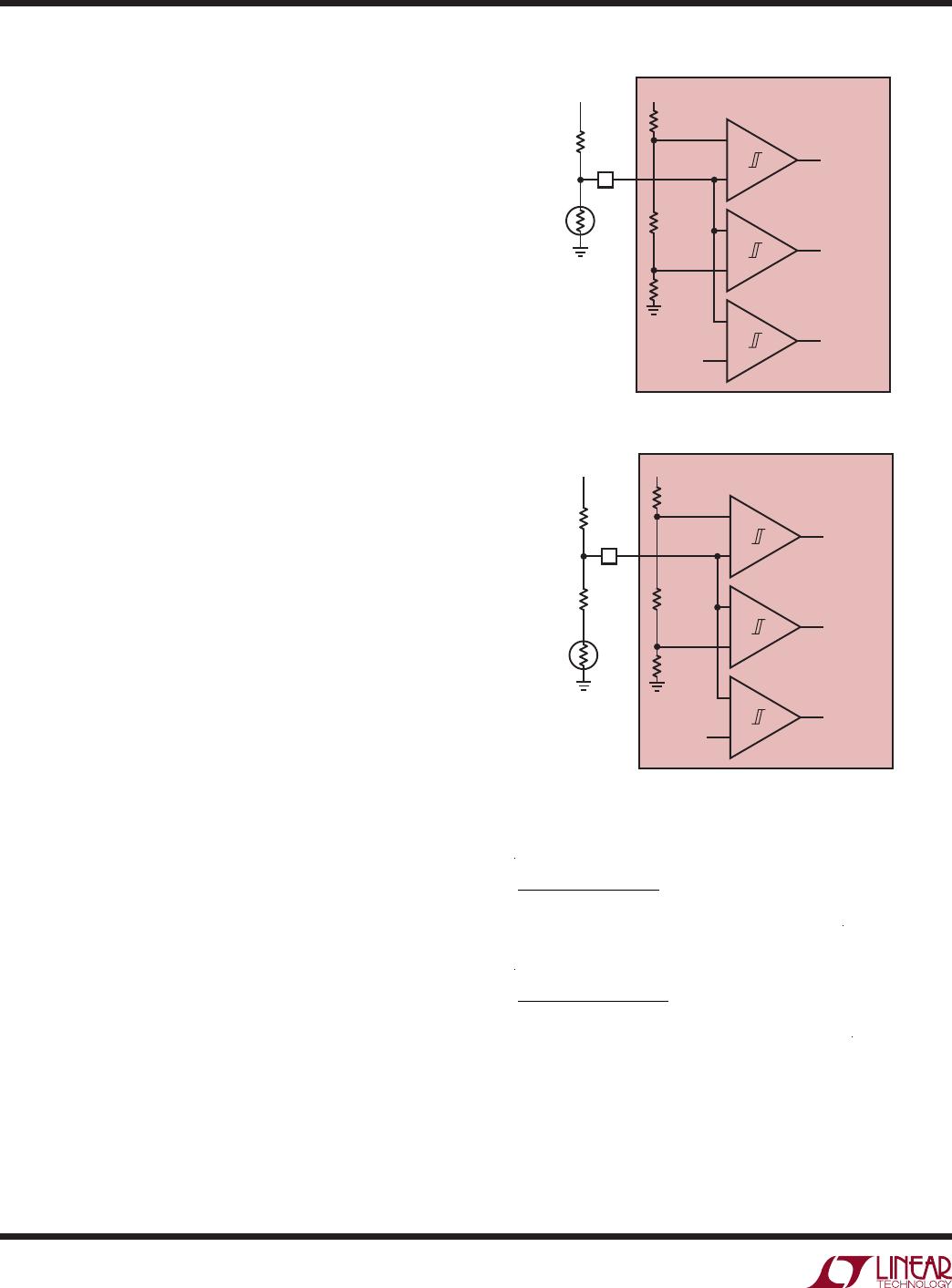

The upper and lower temperature trip points can be inde-

pendently programmed by using an additional bias resistor

as shown in Figure 5b. The following formulas can be used

to compute the values of R

NOM

and R1:

R

NOM

=

COLD

HOT

2.714

• R25

R1= 0.536 • R

– α

• R25

For example, to set the trip points to 0°C and 45°C with

a Vishay Curve 1 thermistor choose:

R

NOM

=

• 10k = 10.42k

the nearest 1% value is 10.5k:

R1 = 0.536 • 10.5k – 0.4368 • 10k = 1.26k

the nearest 1% value is 1.27k. The final circuit is shown

in Figure 5b and results in an upper trip point of 45°C and

a lower trip point of 0°C.

USB Inrush Limiting

When a USB cable is plugged into a portable product,

the inductance of the cable and the high-Q ceramic input

capacitor form an L-C resonant circuit. If the cable does

not have adequate mutual coupling or if there is not much

impedance in the cable, it is possible for the voltage at

the input of the product to reach as high as twice the

USB voltage (~10V) before it settles out. In fact, due to

the high voltage coefficient of many ceramic capacitors, a

nonlinearity, the voltage may even exceed twice the USB

voltage. To prevent excessive voltage from damaging the

LTC3555 family during a hot insertion, it is best to have

a low voltage coefficient capacitor at the V

BUS

pin to the

LTC3555 family. This is achievable by selecting an MLCC

capacitor that has a higher voltage rating than that required

for the application. For example, a 16V, X5R, 10µF capaci-

tor in a 1206 case would be a better choice than a 6.3V,

X5R, 10µF capacitor in a smaller 0805 case.

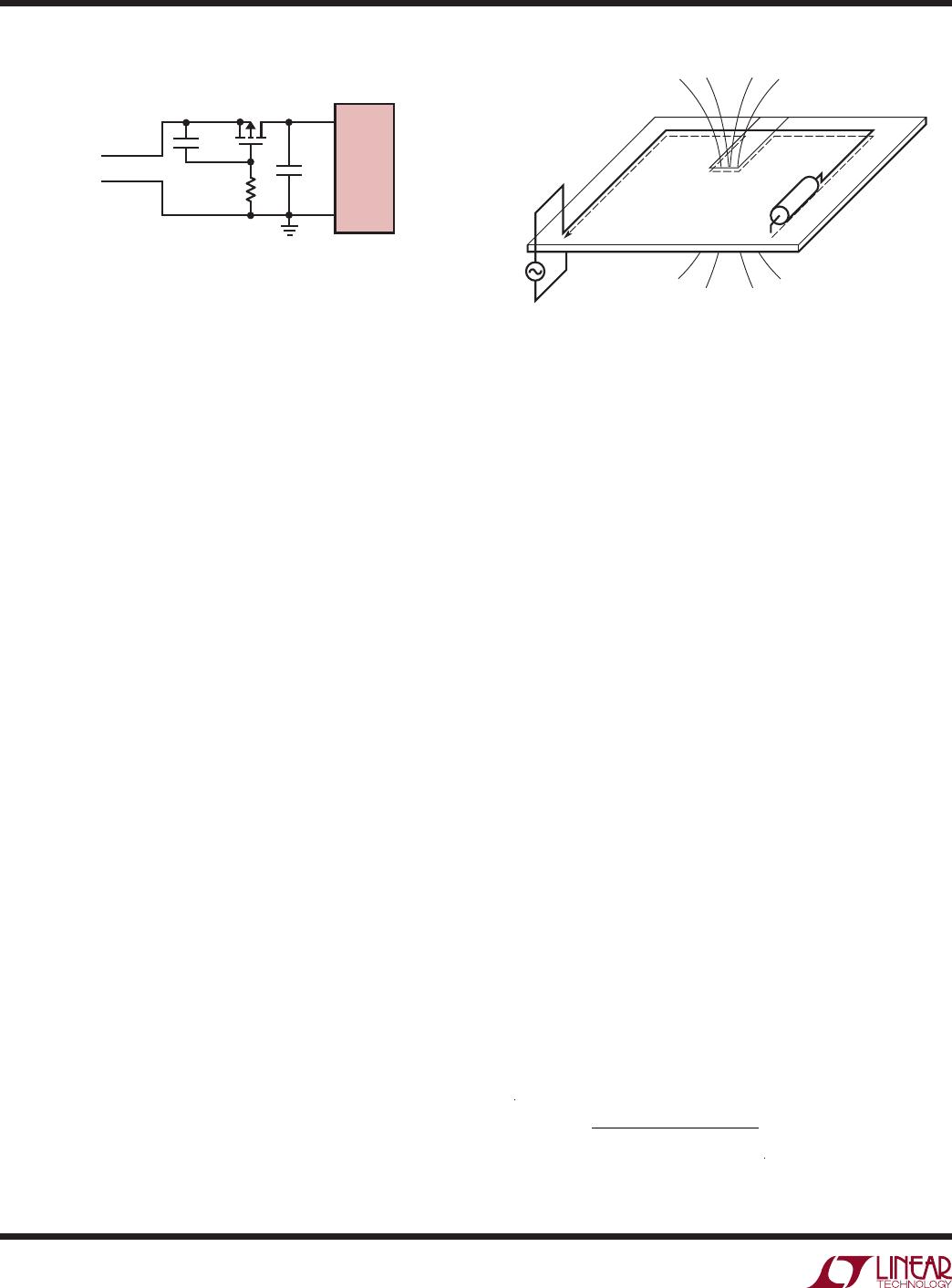

Alternatively, the following soft connect circuit (Figure 6)

can be employed. In this circuit, capacitor C1 holds MP1

off when the cable is first connected. Eventually C1 begins

to charge up to the USB input voltage applying increasing

gate support to MP1. The long time constant of R1 and

C1 prevent the current from building up in the cable too

fast thus dampening out any resonant overshoot.

Printed Circuit Board Layout Considerations

In order to be able to deliver maximum current under all

conditions, it is critical that the Exposed Pad on the back-

side of the LTC3555 family package be soldered to the PC

board ground. Failure to make thermal contact between

the Exposed Pad on the backside of the package and the

copper board will result in higher thermal resistances.

Furthermore, due to its high frequency switching circuitry,

it is imperative that the input capacitors, inductors and

output capacitors be as close to the LTC3555 family as

possible and that there be an

unbroken

ground plane under

the IC and all of its external high frequency components.

APPLICATIONS INFORMATION