MAX7302

SMBus/I

2

C Interfaced 9-Port,

Level-Translating GPIO and LED Driver with CLA

______________________________________________________________________________________ 17

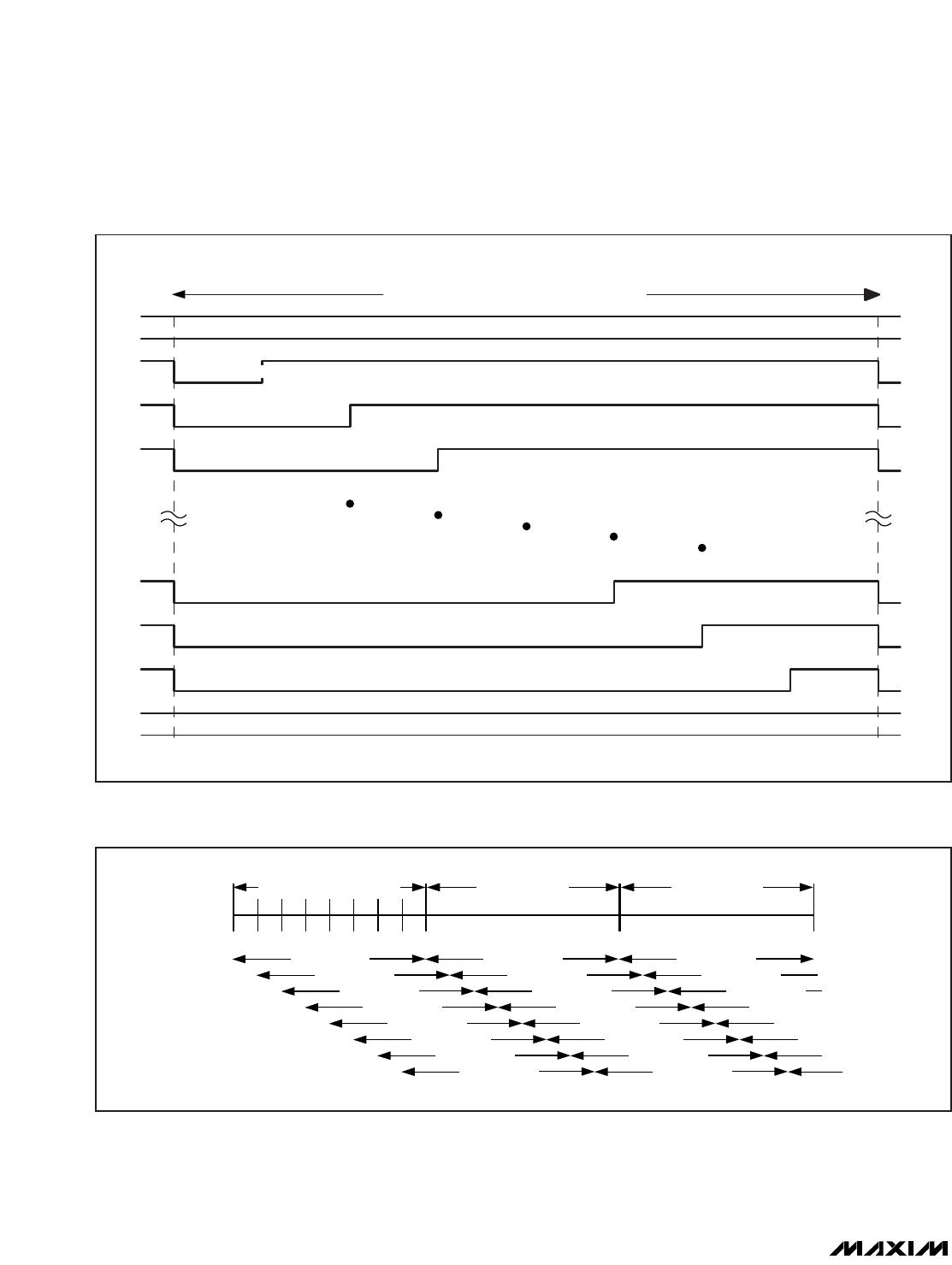

REGISTER DATA

PWM SETTINGS

D7 D6 D5 D4 D3 D2 D1 D0

Port P_ is a static logic-level low output port 0 X 1 00000

Port P_ is a PWM output port; PWM duty cycle is 1/16 0 X 1 00001

Port P_ is a PWM output port; PWM duty cycle is 2/16 0 X 1 00010

Port P_ is a PWM output port; PWM duty cycle is 3/16 0 X 1 00100

……

Port P_ is a PWM output port; PWM duty cycle is 14/16 0 X 1 0 1 1 1 0

Port P_ is a PWM output port; PWM duty cycle is 15/16 0 X 1 0 1 1 1 1

Port P_ is a static logic-level high output port (32/32) 0 1 1 1 X X X X

Table 11. Blink Settings on Output Ports

REGISTER BIT

FUNCTION

D5 D4 D3 D2 D1 D0

XOR noninverted 00

XOR P3 inverted 10

XOR P2 inverted 01

XOR both ports inverted

01X

1

X

1

3 input AND/OR all noninverted 0 0 0

3 input AND/OR P2 inverted 0 0 1

3 input AND/OR P3 inverted 0 1 0

3 input AND/OR P4 inverted 0 1 1

3 input AND/OR P2 and P3 inverted 1 0 0

3 input AND/OR P2 and P4 inverted 1 0 1

3 input AND/OR P3 and P4 inverted 1 1 0

3 input AND/OR all inverted

1

1

1

1

1

1

Table 12. CLA0 (P2–P5) Configuration Register Setting (0x28)

DEVICE CONFIGURATION

REGISTER 0x26

BLINK OR PWM SETTING

BIT D4

BLINK2

BIT D3

BLINK1

BIT D2

BLINK0

BLINK OR PWM

FREQUENCY (32kHz

INTERNAL OSCILLATOR)

(Hz)

BLINK OR PWM

FREQUENCY (0 TO 1MHz

Bl i nk p er i od i s 8s ( 0.125H z) 0 0 0 0.125 OSCIN / 262,144

Blink period is 4s (0.25Hz) 0 0 1 0.25 OSCIN / 131,072

Blink period is 2s (0.5Hz) 0 1 0 0.5 OSCIN / 65,536

Blink period is 1s (1Hz) 0 1 1 1 OSCIN / 32,768

Blink period is a 1/2s (2Hz) 1 0 0 2 OSCIN / 16,384

Blink period is a 1/4s (4Hz) 1 0 1 4 OSCIN / 8192

Bl i nk p er i od i s an 1/8s ( 8H z) 1 1 0 8 OSCIN / 4096

Bl i nk p er i od i s a 1/32s ( 32H z) 1 1 1 32 OSCIN / 1024

PWM X X X 1024 OSCIN / 32

Table 10. Blink and PWM Frequencies