MAX7302

SMBus/I

2

C Interfaced 9-Port,

Level-Translating GPIO and LED Driver with CLA

_______________________________________________________________________________________ 7

Detailed Description

The MAX7302 9-port, general-purpose port expander

operates from a 1.62V to 3.6V power supply. Port P1

can be configured as an input and an open-drain out-

put. Port P1 can also be configured to function as an

INT output. Ports P2–P9 can be configured as inputs,

push-pull outputs, and open-drain outputs. Ports P2–P9

can be used as simple configurable logic arrays

(CLAs) to form user-defined logic gates.

Each port configured as an open-drain or push-pull

output can sink up to 25mA. Push-pull outputs also

have a 5mA source drive capability. The MAX7302 is

rated to sink a total of 100mA into any combination of

its output ports. Output ports have PWM and blink

capabilities, as well as logic drive.

Initial Power-Up

On power-up, the MAX7302 default configuration has all

9 ports, P1–P9, configured as input ports with logic lev-

els referenced to V

LA

. The transition detection interrupt

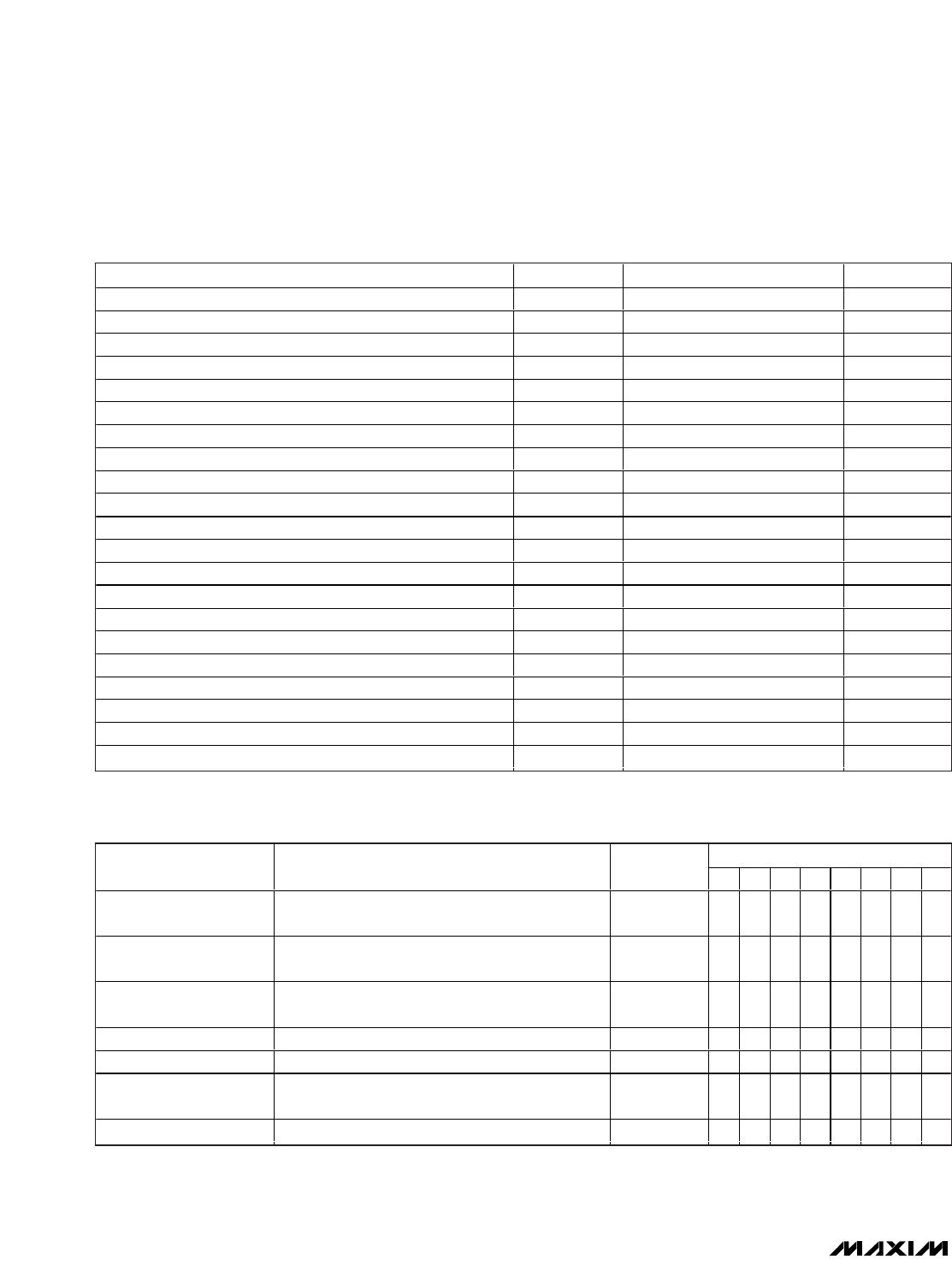

status flag resets and stays high (see Tables 1 and 2).

Device Configuration Registers

The device configuration registers set up the interrupt

function, serial-interface bus timeout, and PWM/blink

oscillator options, global blink period, and reset options

(see Tables 3 and 4).