FUNCTION

D7 Don’t care x Don’t care.

0 Refers inputs to the VL supply voltage; sets outputs to open drain.

D6

Port supply

reference

1 Refers inputs to the V

DD

supply voltage; sets outputs to push-pull.

0 Disables the transition interrupt.

D5

Transition interrupt

enable

1 Enables the transition interrupt.

D4

Transition detection

bit 1

0 Detects the next transition on the port input.

D3

Transition detection

bit 0

0 Detects the next transition on the port input.

0 Disables debouncing of the input port.

D2 Debounce

1 Enables debouncing of the input port.

0 No transition has occurred since the last port read.

D1

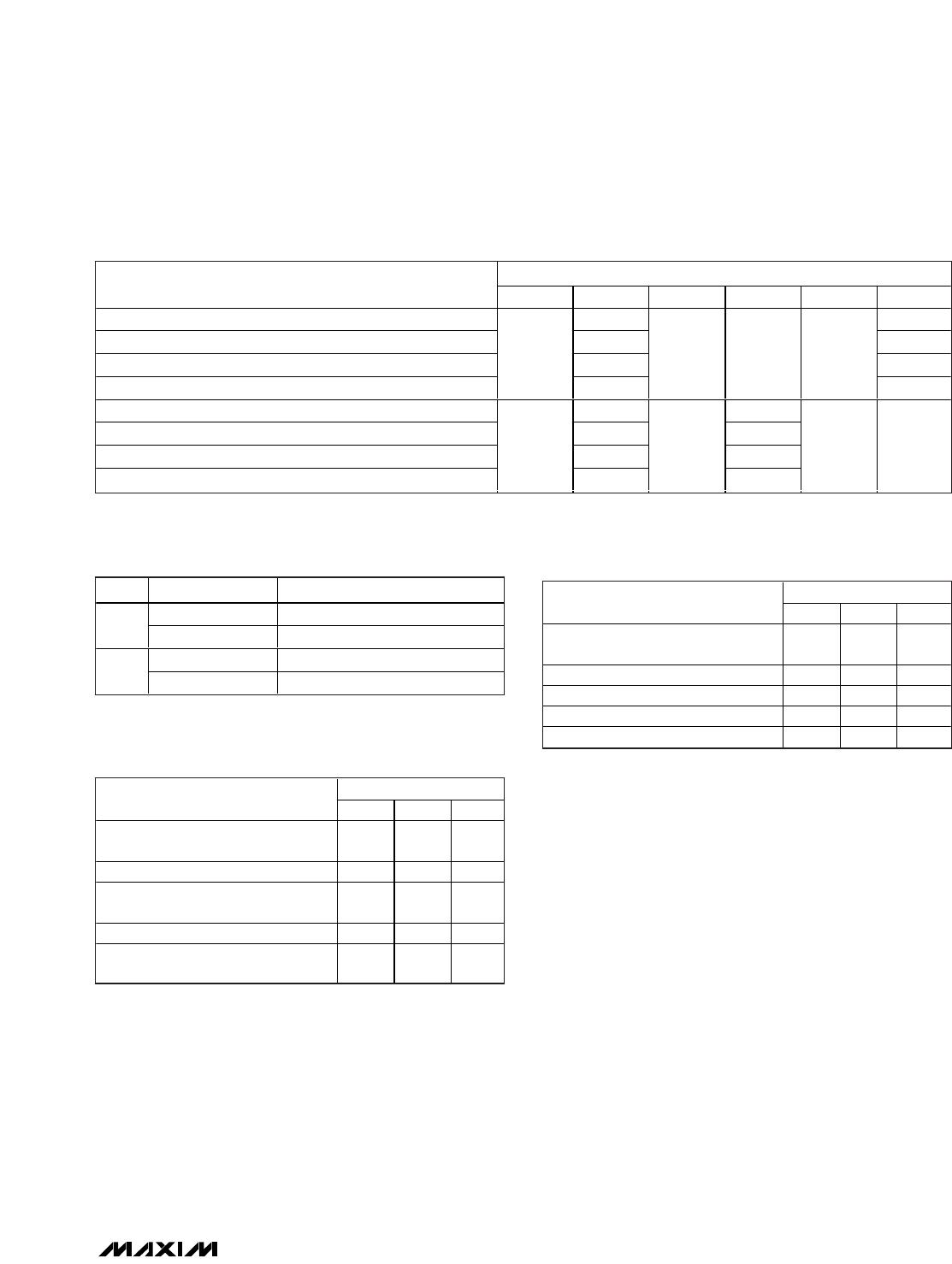

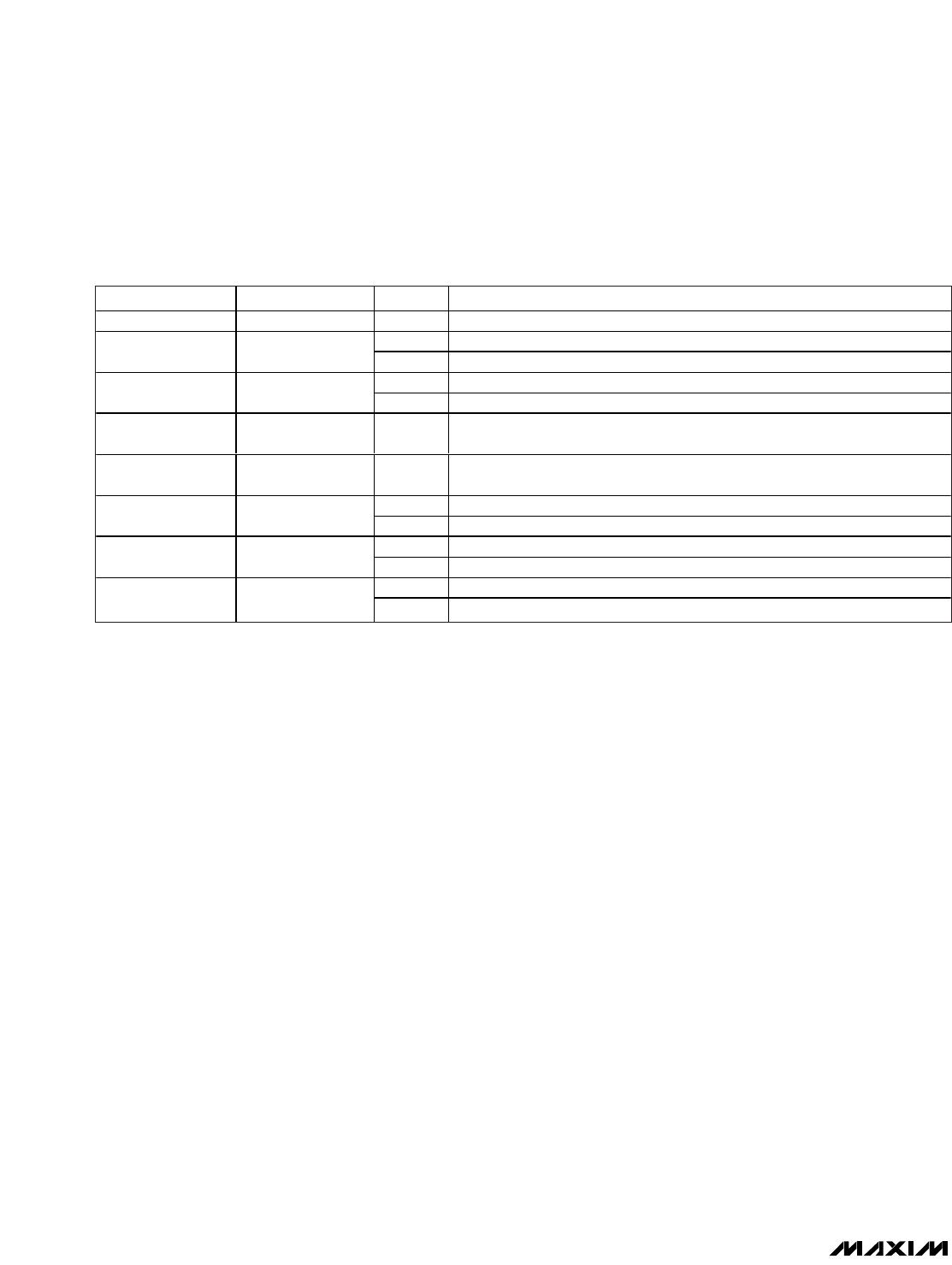

Table 18. Port I/O Registers (I/O Port 5 and 9 Configured as CLA Outputs, Registers

0x05 and 0x09)

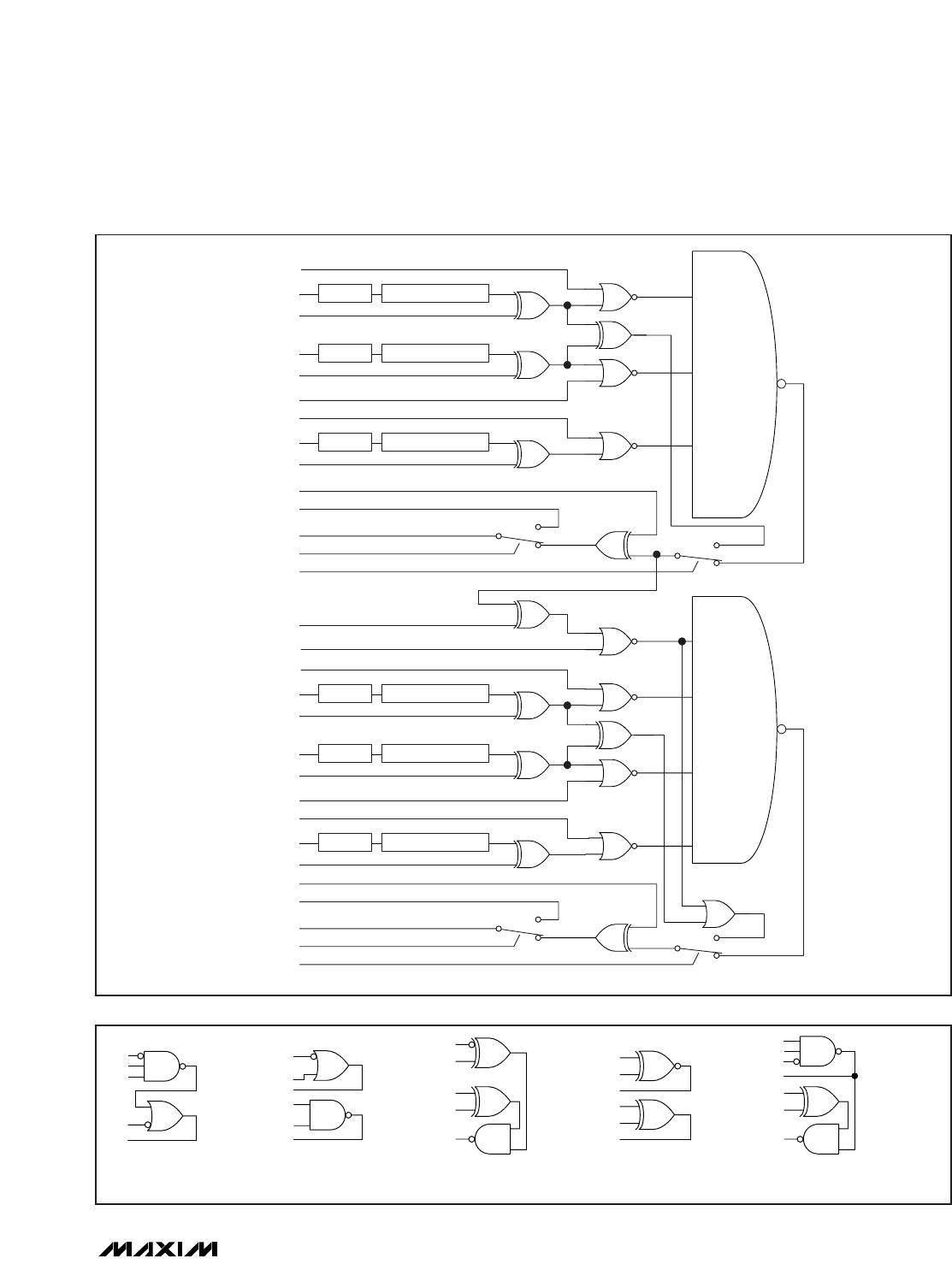

Configurable Logic Array (CLA)

The CLA configures groups of four ports as either a

combinational logic gate up to three inputs, or a two

input exclusive OR/NOR gate (see Tables 12-15).

Eight-port dual groups can be cascaded to form a

two-level gate with the intermediate term brought out

as an output or not, as desired. If fewer than three

gate inputs are needed, the unused CLA input(s)

(which can be any combination of the three CLA

inputs) remain available as independent GPIO ports

(see Figure 8). Use the configurable logic-array enable

register (see Table 16) to enable ports as CLAs. Use the

configurable logic-array lock register (see Table 17) to

permanently lock in any logic-array combination of CLAs

until the next power cycle. Setting D0 and D1 to logic-

high in the configurable logic-array lock register locks the

corresponding bit position in the configurable logic-array

enable register. Additionally, the appropriate CLA_ regis-

ter (addresses 0x28 and 0x29) cannot be changed.

The configurable logic-array lock register is unlocked

on power-up, or by RST when configured by the

RSTPOR bit in the configure register. Each lock bit can

only be written to once per power cycle.

A CLA’s input(s) and output can be read through the

serial interface like a normal input port. The MAX7302

creates a gate that provides an independent real-time

logic function, and every node of it can be examined

through the I

2

C interface with optional debounce and

transition detection.

Setting bits D0 and D1 to logic-high enables the CLA

functionality and sets ports P5 and P9 as CLA outputs

(see Table 16). When in CLA mode, the port I/O regis-

ter data is interpreted differently for CLA output ports

(see Table 18). Bit D7 that normally selects the port

direction is ignored because either port P5 or P9 is

always an output. Bit D6 sets both the CLA output type

(push-pull or open drain) and the logic threshold for

reading the CLA output status back through the I

2

C

interface. The other bits set the readback options, such

as debounce and transition detection interrupt.