Clock management ST7570

18/26 Doc ID 17526 Rev 2

7 Clock management

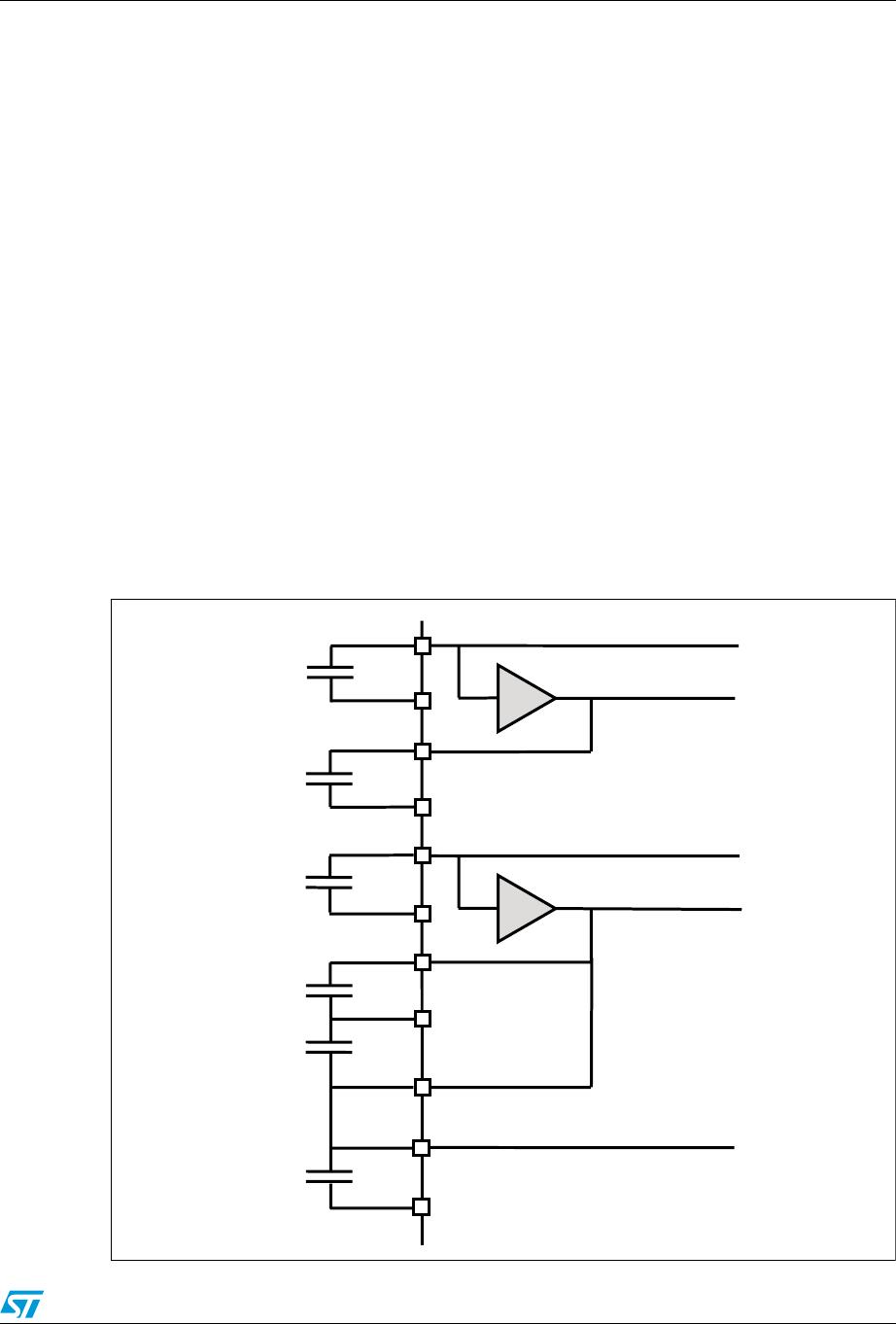

The main clock source is an 8 MHz crystal connected to the internal oscillator through XIN

and XOUT pins. Both XIN and XOUT pins have a 32 pF integrated capacitor, in order to

drive a crystal having a load capacitance of 16 pF with no additional components.

Alternatively, an 8 MHz external clock can be directly supplied to XIN pin, leaving XOUT

floating.

A PLL internally connected to the output of the oscillator generates the f

CLK_PHY

, required by

the PHY processor block. f

CLK_PHY

is then scaled down by two to obtain f

CLK_PC

, required

by the protocol controller.

8 Functional overview

The ST7570 embeds complete physical (PHY) and a medium access control (MAC)

protocol layers and services compliant with the open standard IEC61334-5-1, mainly

developed for smart metering applications, but suitable also for other command and control

applications and remote load management in CENELEC B and D bands.

A local port (UART) is available for communication with an external host, exporting all the

functions and services required to configure and control the device and its protocol stack.

Below a list of the protocol layers and functions embedded in the ST7570 (Figure 10):

● Physical layer: implemented in the PHY processor and exporting all the primitive

functions listed in the international standard document IEC61334-5-1, plus additional

services for configuration, alarm management, signal and noise amplitude estimation,

phase detection, statistical information;

● MAC layer: implemented on the protocol controller and exporting all the primitive

functions listed in the international standard document IEC61334-5-1, Repeater Call

and Intelligent search initiator process together with additional services.

● Management information base (MIB): an information database with all the data

required for proper configuration of the system (at both PHY and MAC layer);

● Host interface: all the services of the PHY, MAC and MIB are exported to an external

host through the local UART port.