AD8194

Rev. 0 | Page 13 of 16

Auxiliary Control Signals

There are four single-ended control signals associated with each

source or sink in an HDMI/DVI application. These are hot plug

detect (HPD), consumer electronics control (CEC), and two

display data channel (DDC) lines. The two signals on the DDC

bus are SDA and SCL (serial data and serial clock, respectively).

The AD8194, which is a low cost part, does not have any addi-

tional capability to switch these signals; other means are

required to switch these signals if required.

In general, it is sufficient to route each auxiliary signal as a

single-ended trace. These signals are not sensitive to impedance

discontinuities, do not require a reference plane, and can be

routed on multiple layers of the PCB. However, it is best to

follow strict layout practices whenever possible to prevent the

PCB design from affecting the overall application. The specific

routing of the HPD, CEC, and DDC lines depends upon the

application in which the AD8194 is being used.

For example, the maximum speed of signals present on the

auxiliary lines is 100 kHz I

2

C data on the DDC lines; therefore,

any layout that enables 100 kHz I

2

C to be passed over the DDC

bus should suffice. The HDMI 1.3 specification, however, places

a strict 50 pF limit on the amount of capacitance that can be

measured on either SDA or SCL at the HDMI input connector.

This 50 pF limit includes the HDMI connector, the PCB, the

capacitance of the CMOS switch, and whatever capacitance is

seen at the input of the HDMI receiver. There is a similar limit

of 100 pF of input capacitance for the CEC line.

The parasitic capacitance of traces on a PCB increases with

trace length. To help ensure that a design satisfies the HDMI

specification, the length of the CEC and DDC lines on the PCB

should be made as short as possible. Additionally, if there is a

reference plane in the layer adjacent to the auxiliary traces in

the PCB stackup, relieving or clearing out this reference plane

immediately under the auxiliary traces significantly decreases

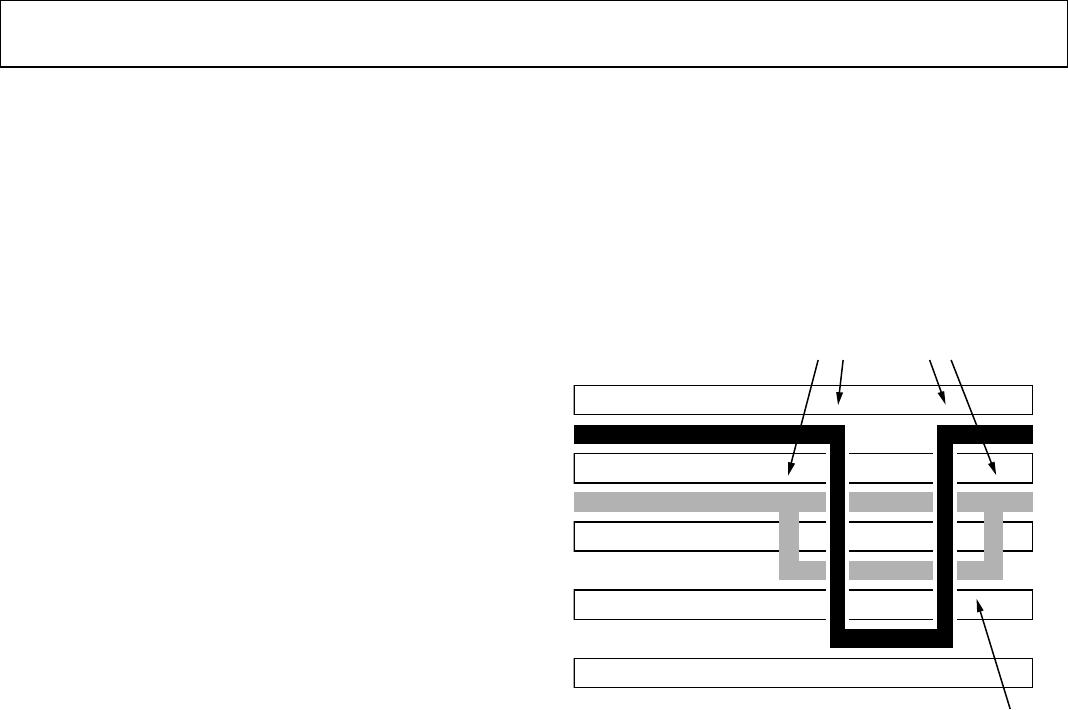

the amount of parasitic trace capacitance. An example of the

board stackup is shown in

Figure 22.

PCB DIELECTRIC

LAYER 1: SIGNAL (MICROSTRIP)

SILKSCREEN

SILKSCREEN

PCB DIELECTRIC

PCB DIELECTRIC

LAYER 2: GND (REFERENCE PLANE)

LAYER 3: PWR (REFERENCE PLANE)

LAYER 4: SIGNAL (MICROSTRIP)

W3W 3W

REFERENCE LAYER

RELIEVED UNDERNEATH

MICROSTRIP

07004-013

Figure 22. Example Board Stackup

HPD is a dc signal presented by a sink to a source to indicate

that the source EDID is available for reading. The placement

of this signal is not critical, but it should be routed as directly

as possible.

Power Supplies

The AD8194 has three separate power supplies referenced to

a single ground. The supply/ground pairs are

• AVCC/AVEE

• VTTI/AVEE

• VTTO/AVEE

The AVCC/AVEE (3.3 V) supply powers the core of the

AD8194. The VTTI/AVEE supply (3.3 V) powers the input

termination (see

Figure 19). Similarly, the VTTO/AVEE

supply (3.3 V) powers the output termination (see

Figure 20).

In a typical application, all pins labeled AVEE should be con-

nected directly to ground. All pins labeled AVCC, VTTI, or

VTTO should be connected to 3.3 V. The supplies can also be

powered individually, but care must be taken to ensure that

each stage of the AD8194 is powered correctly.

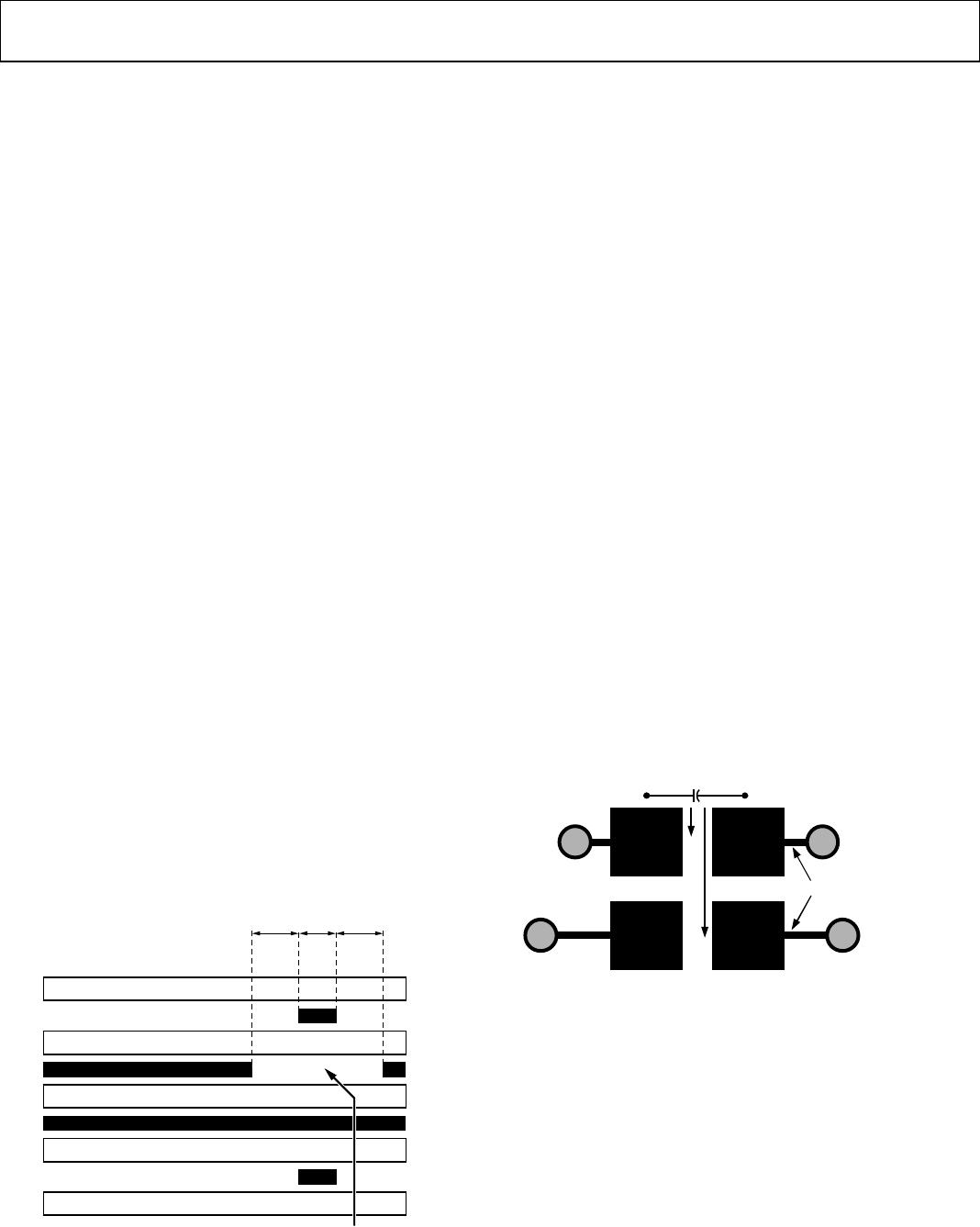

Power Supply Bypassing

The AD8194 requires minimal supply bypassing. When

powering the supplies individually, place a 0.01 F capacitor

between each 3.3 V supply pin (AVCC, VTTI, and VTTO) and

ground to filter out supply noise. Generally, bypass capacitors

should be placed near the power pins and should connect directly

to the relevant supplies (without long intervening traces). For

example, to minimize the parasitic inductance of the power

supply decoupling capacitors, minimize the trace length between

capacitor landing pads and the vias as shown in

Figure 23.

EXTRA ADDED INDUCTANCE

RECOMMENDED

NOT RECOMMENDED

07004-014

Figure 23. Recommended Pad Outline for Bypass Capacitors

In applications where the AD8194 is powered by a single 3.3 V

supply, it is recommended to use two reference supply planes

and bypass the 3.3 V reference plane to the ground reference

plane with one 220 pF, one 1000 pF, two 0.01 F, and one 4.7 F

capacitors. The capacitors should via down directly to the supply

planes and be placed within a few centimeters of the AD8194.