AD8194

Rev. 0 | Page 5 of 16

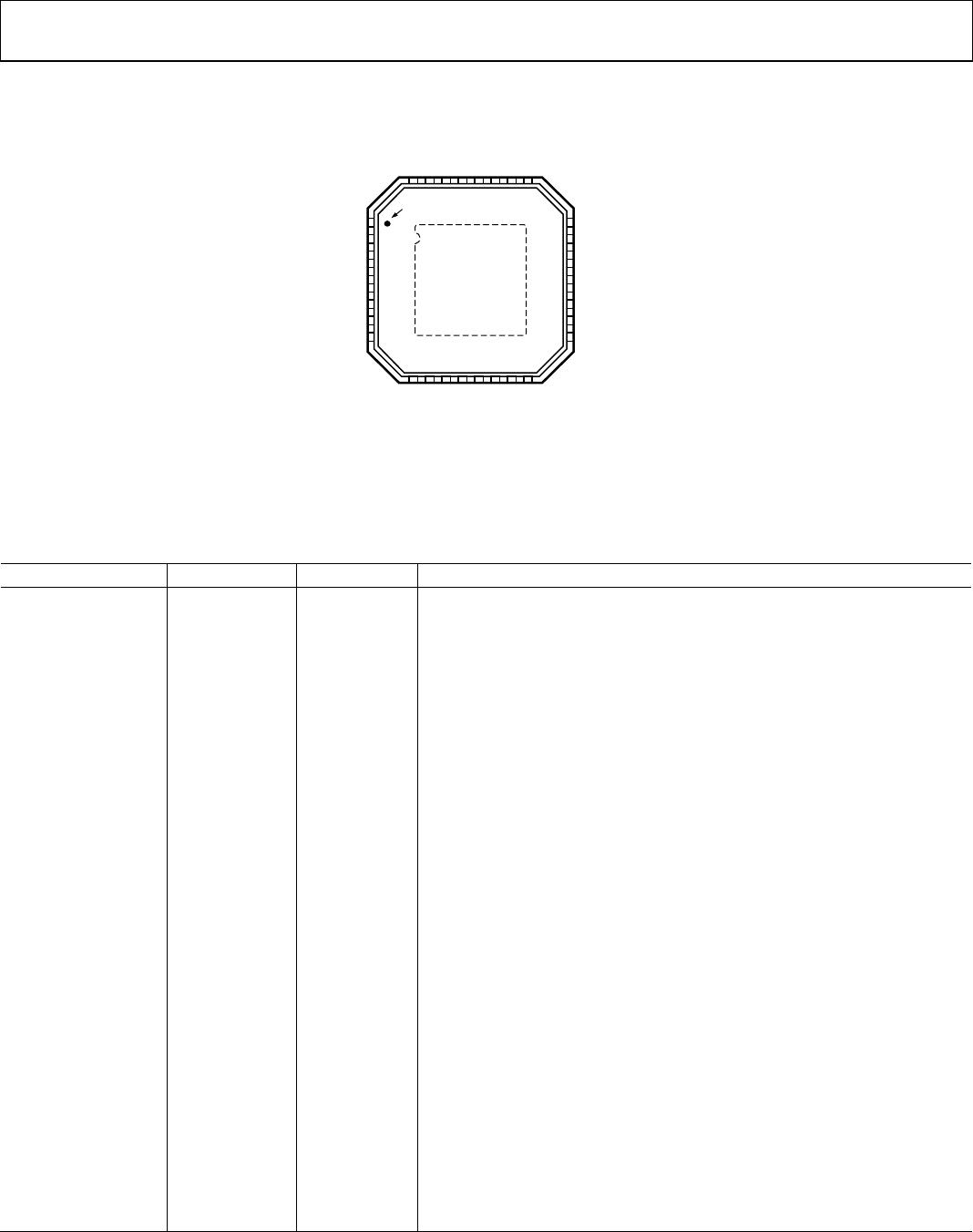

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

2

3

4

5

6

7

8

IN_A2

IP_A2

VTTI

IN_A3

IP_A3

AVCC

OP3

ON3

32

31

30

29

28

27

26

25

9

10

11

12

13

14

15

16

OP2

ON2

AVEE

OP1

ON1

VTTO

OP0

ON0

IP_B2

IN_B2

AVCC

IP_B1

IN_B1

VTTI

IP_B0

IN_B0

24

23

22

21

20

19

18

17

PIN 1

INDICATOR

IP_A1

IN_A1

S_SEL

IP_A0

IN_A0

AVEE

IP_B3

IN_B3

AD8194

TOP VIEW

(Not to Scale)

07004-003

NOTES

1. THE AD8194 LFCSP HAS AN EXPOSED PADDLE (ePAD) ON THE UNDERSIDE

OF THE PACKAGE, WHICH AIDS IN HEAT DISSIPATION. THE ePAD MUST BE

ELECTRICALLY CONNECTED TO THE AVEE SUPPLY PLANE TO MEET

THERMAL SPECIFICATIONS.

Figure 3. Pin Configuration

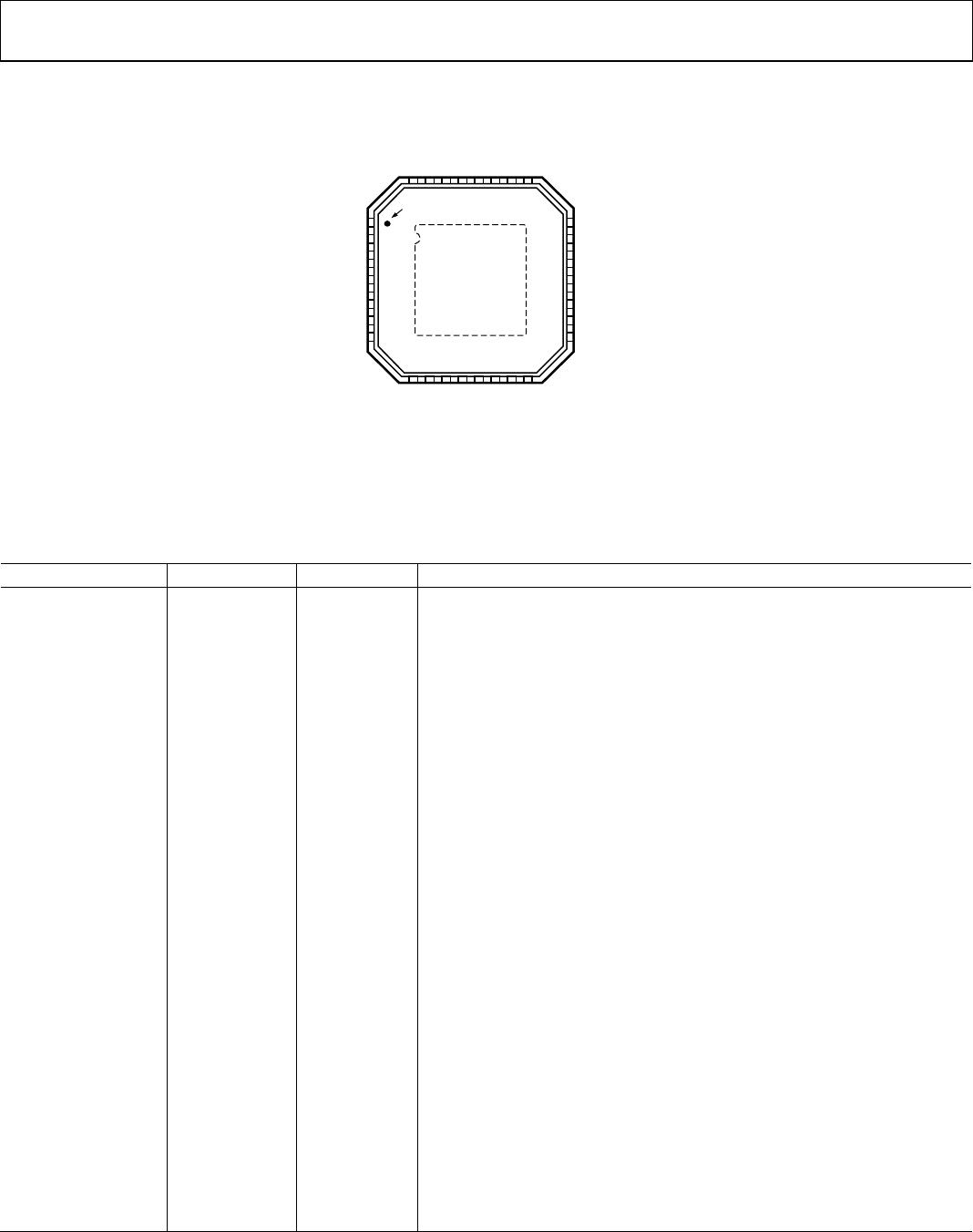

Table 4. Pin Function Descriptions

Pin No. Mnemonic Type

1

Description

1 IN_A2 HS I High Speed Input Complement.

2 IP_A2 HS I High Speed Input.

3, 19 VTTI Power Input Termination Supply. Nominally connected to AVCC.

4 IN_A3 HS I High Speed Input Complement.

5 IP_A3 HS I High Speed Input.

6, 22 AVCC Power Positive Power Supply. 3.3 V nominal.

7 OP3 HS O High Speed Output.

8 ON3 HS O High Speed Output Complement.

9 OP2 HS O High Speed Output.

10 ON2 HS O High Speed Output Complement.

11, 27, ePAD AVEE Power Negative Power Supply. 0 V nominal.

12 OP1 HS O High Speed Output.

13 ON1 HS O High Speed Output Complement.

14 VTTO Power Output Termination Supply. Nominally connected to AVCC.

15 OP0 HS O High Speed Output.

16 ON0 HS O High Speed Output Complement.

17 IN_B0 HS I High Speed Input Complement.

18 IP_B0 HS I High Speed Input.

20 IN_B1 HS I High Speed Input Complement.

21 IP_B1 HS I High Speed Input.

23 IN_B2 HS I High Speed Input Complement.

24 IP_B2 HS I High Speed Input.

25 IN_B3 HS I High Speed Input Complement.

26 IP_B3 HS I High Speed Input.

28 IN_A0 HS I High Speed Input Complement.

29 IP_A0 HS I High Speed Input.

30 S_SEL Control Source Selector Pin.

31 IN_A1 HS I High Speed Input Complement.

32 IP_A1 HS I High Speed Input.

1

HS = high speed, I = input, O = output.