10

FN8164.7

August 17, 2015

Absolute Maximum Ratings Thermal Information

Supply Voltage (V

CC

) Limits

X9241A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5V ±10%

Max Wiper Current for 2k R

TOTAL

. . . . . . . . . . . . . . . . . . . . . . ±4mA

Max Wiper Current for 10k and 50k R

TOTAL

. . . . . . . . . . . . . . ±3mA

Voltage on SCK, SCL or any address

input with respect to V

SS

. . . . . . . . . . . . . . . . . . . . . . . -1V to +7V

Voltage on any V

H

/R

H

, V

W

/R

W

or V

L

/R

L

referenced to V

SS

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +6V/-4V

V = |V

H

/R

H

- V

L

/R

L

|. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10V

I

W

(10s) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±6mA

Power rating (each pot) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50mW

Temperature under bias. . . . . . . . . . . . . . . . . . . . . . . . -65 to +135°C

Storage temperature . . . . . . . . . . . . . . . . . . . . . . . . . . -65 to +150°C

Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

Recommended Operating Conditions

Temperature (Commercial) . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

Temperature (Industrial). . . . . . . . . . . . . . . . . . . . . . . -40°C to +85°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

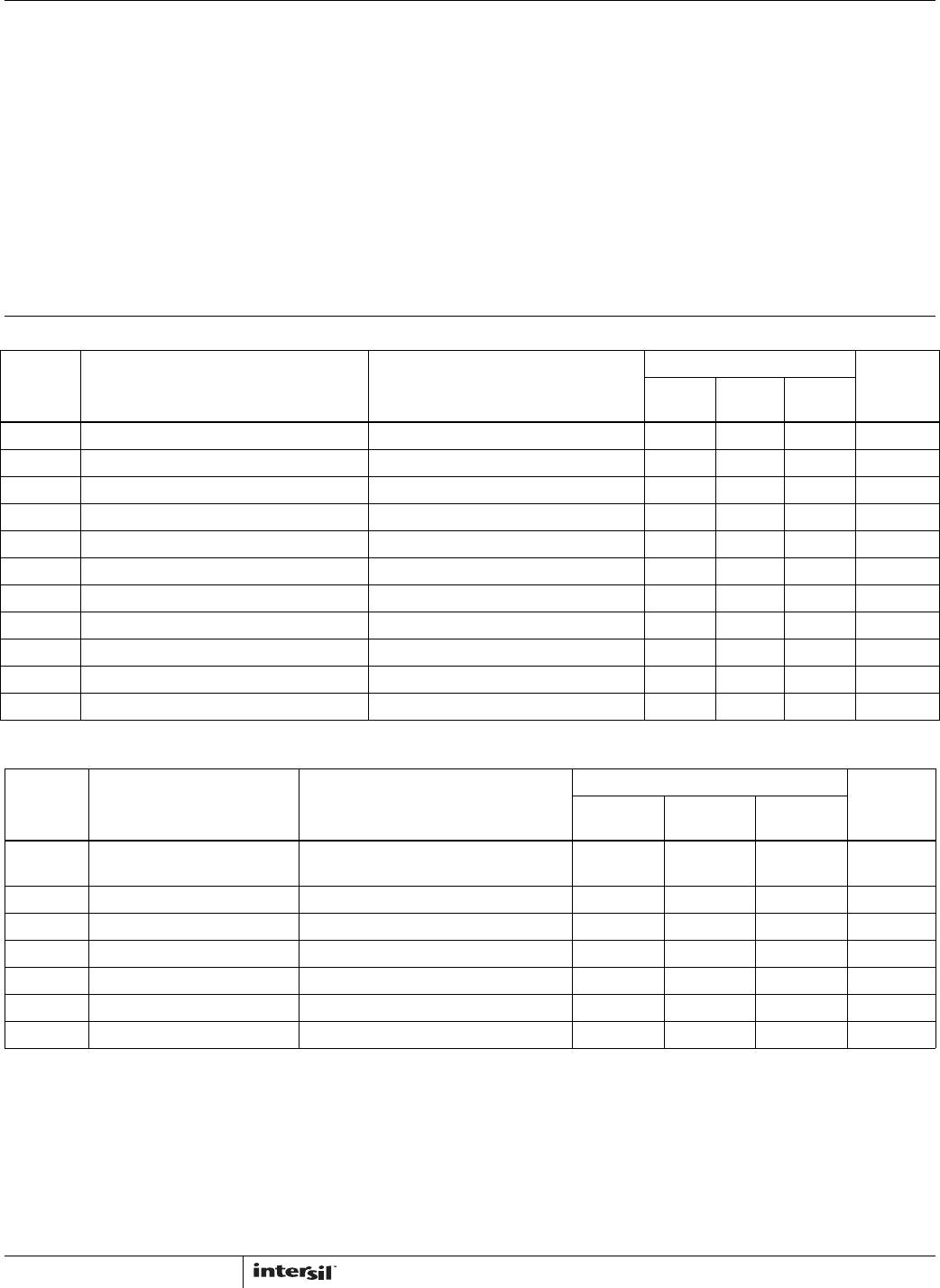

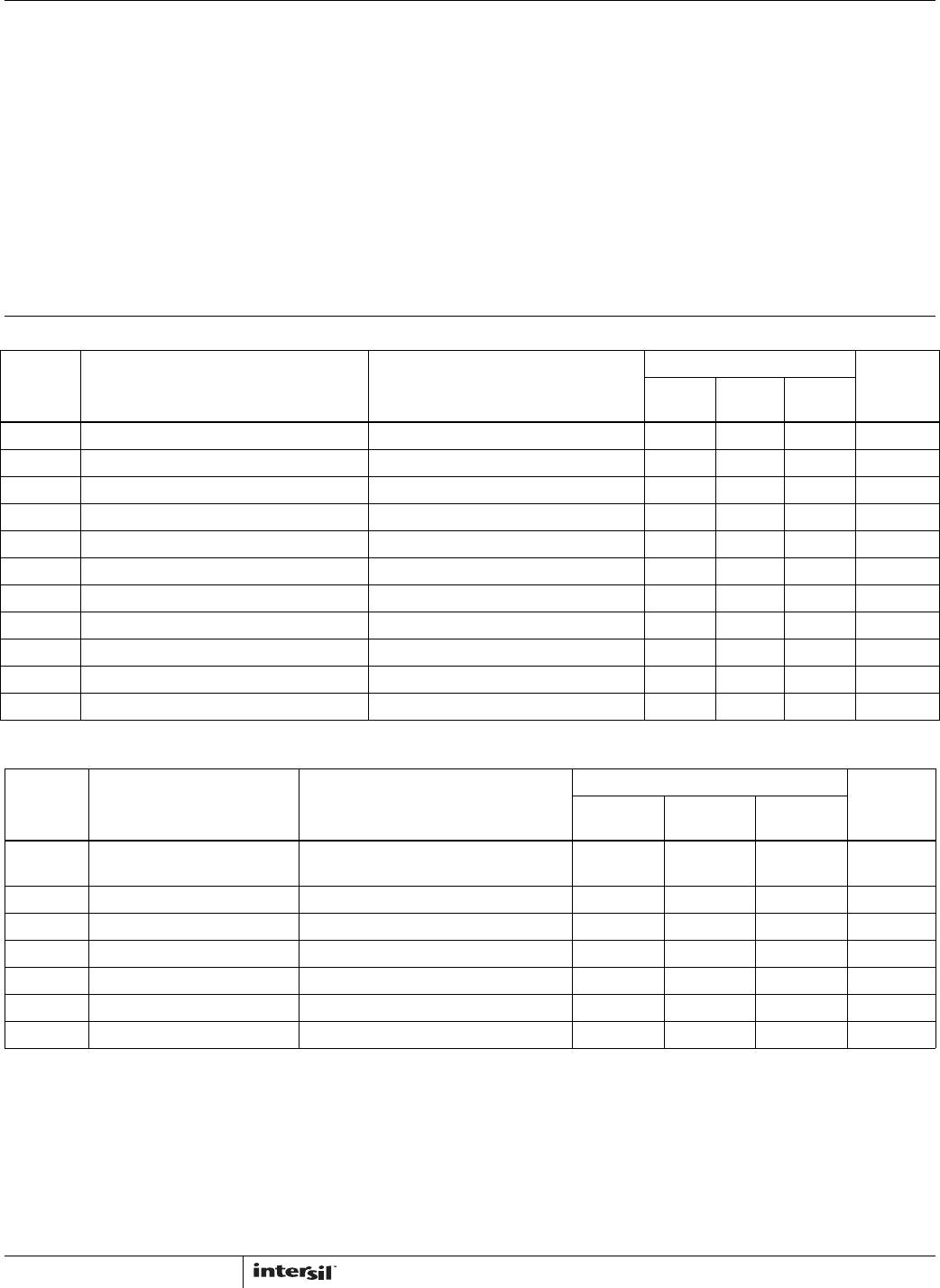

Analog Specifications (Over recommended operating conditions unless otherwise stated).

SYMBOL PARAMETER TEST CONDITION

LIMITS

UNIT

MIN

(Note 11) TYP

MAX

(Note 11)

R

TOTAL

End to end resistance -20 +20 %

R

W

Wiper resistance Wiper Current = (V

H

- V

L

)/R

TOTAL

40 130

V

TERM

Voltage on any V

H

/R

H

, V

W

/R

W

or V

L

/R

L

Pin -3.0 +5 V

Noise Ref: 1kHz (Note 7) 120 dBV

Resolution (Note 7) 1.6 %

Absolute linearity (Note 3) R

w(n)(actual)

- R

w(n)(expected)

±1 MI (Note 5)

Relative linearity

(Note 4) R

w(n + 1)

- [R

w(n) + MI

] ±0.2 MI (Note 5)

Temperature coefficient of R

TOTAL

(Note 7) ±300 ppm/°C

Ratiometric temperature coefficient (Note 7) ±20 ppm/C

C

H

/C

L

/C

W

Potentiometer capacitances See Circuit #3 and (Note 7) 15/15/25 pF

l

AL

R

H

, R

I

, R

W

leakage current V

IN

= V

TERM

. Device is in stand-by mode. 0.1 1 µA

DC Electrical Specifications (Over recommended operating conditions unless otherwise stated.)

SYMBOL PARAMETER TEST CONDITION

LIMITS

UNIT

MIN

(Note 11) TYP

MAX

(Note 11)

l

CC

Supply current (active) f

SCL

= 100kHz, Write/Read to WCR,

Other Inputs = V

SS

3mA

I

SB

V

CC

current (standby) SCL = SDA = V

CC

, Addr. = V

SS

200 500 µA

I

LI

Input leakage current V

IN

= V

SS

to V

CC

10 µA

I

LO

Output leakage current V

OUT

= V

SS

to V

CC

10 µA

V

IH

Input HIGH voltage 2 V

V

IL

Input LOW voltage 0.8 V

V

OL

Output LOW voltage I

OL

= 3mA 0.4 V

NOTES:

3. Absolute Linearity is utilized to determine actual wiper voltage versus expected voltage as determined by wiper position when used as a

potentiometer.

4. Relative Linearity is utilized to determine the actual change in voltage between two successive tap positions when used as a potentiometer. It is

a measure of the error in step size.

5. MI = RTOT/63 or (R

H

– R

L

)/63, single pot

6. Max = all four arrays cascaded together, Typical = individual array resolutions.

X9241A