X28HC64

11

FN8109.4

June 27, 2016

Submit Document Feedback

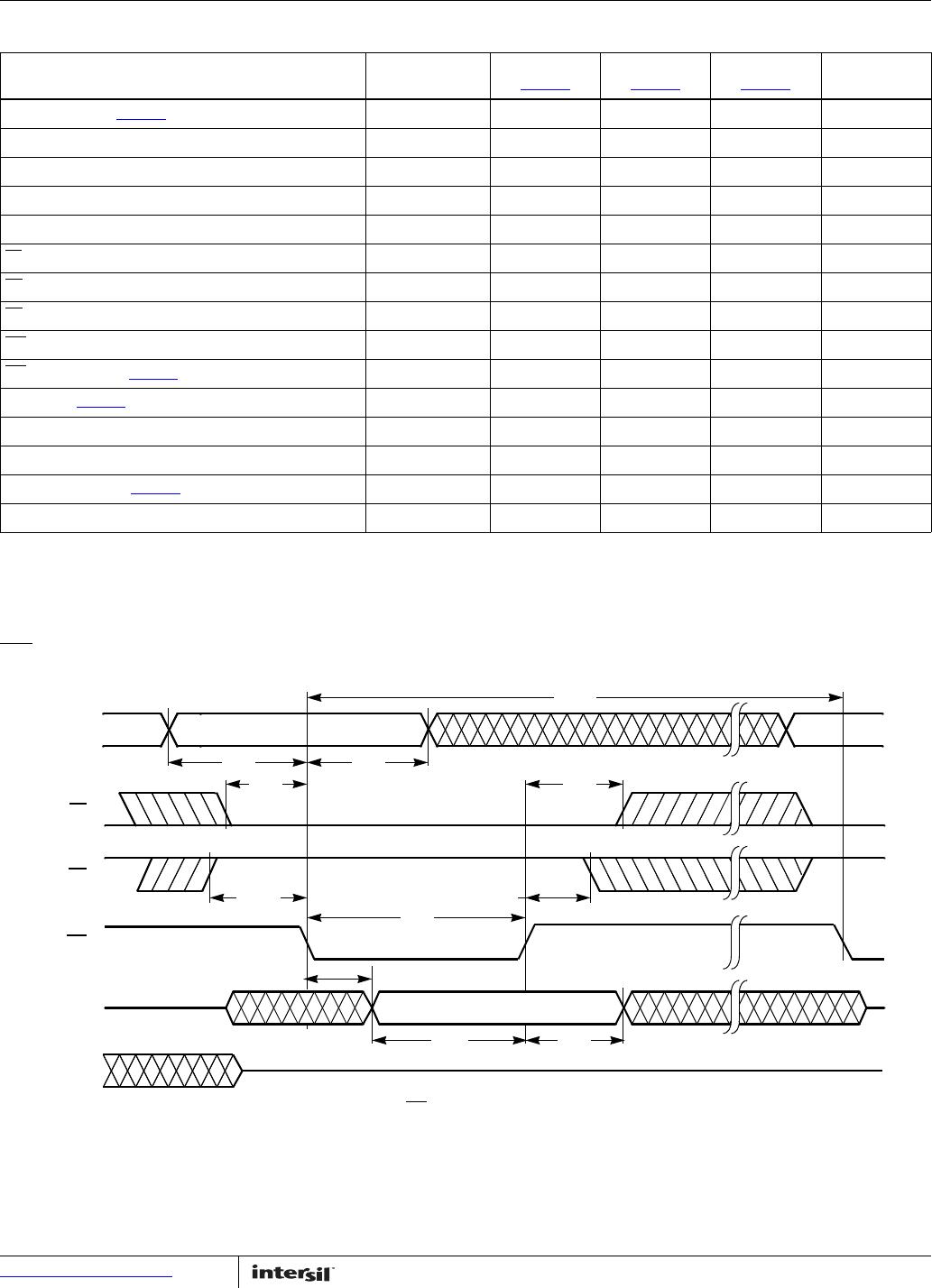

AC Electrical Specifications

Read Cycle Limits Over the recommended operating conditions unless otherwise specified.

PARAMETER SYMBOL

X28HC64-70 X28HC64-90 X28HC64-12

UNIT

MIN

(Note 10

)

MAX

(Note 10)

MIN

(Note 10)

MAX

(Note 10)

MIN

(Note 10)

MAX

(Note 10)

Read Cycle Time t

RC

70 90 120 ns

Chip Enable Access Time t

CE

70 90 120 ns

Address Access Time t

AA

70 90 120 ns

Output Enable Access Time t

OE

35 40 50 ns

CE LOW to Active Output (Note 14)t

LZ

000 ns

OE

LOW to Active Output (Note 14)t

OLZ

000 ns

CE

HIGH to High Z Output (Note 14)t

HZ

30 30 30 ns

OE HIGH to High Z Output (Note 14)t

OHZ

30 30 30 ns

Output Hold from Address Change t

OH

000ns

NOTE:

14. t

LZ

minimum, t

HZ

, t

OLZ

minimum, and t

OHZ

are periodically sampled and not 100% tested. t

HZ

maximum and t

OHZ

maximum are measured from the

point when CE

or OE return HIGH (whichever occurs first) to the time when the outputs are no longer driven.

Read Cycle

FIGURE 14. READ CYCLE

t

CE

t

RC

ADDRESS

CE

OE

WE

DATA VALID

t

OE

t

LZ

t

OLZ

t

OH

t

AA

t

HZ

t

OHZ

DATA I/O

V

IH

HIGH Z

DATA VALID