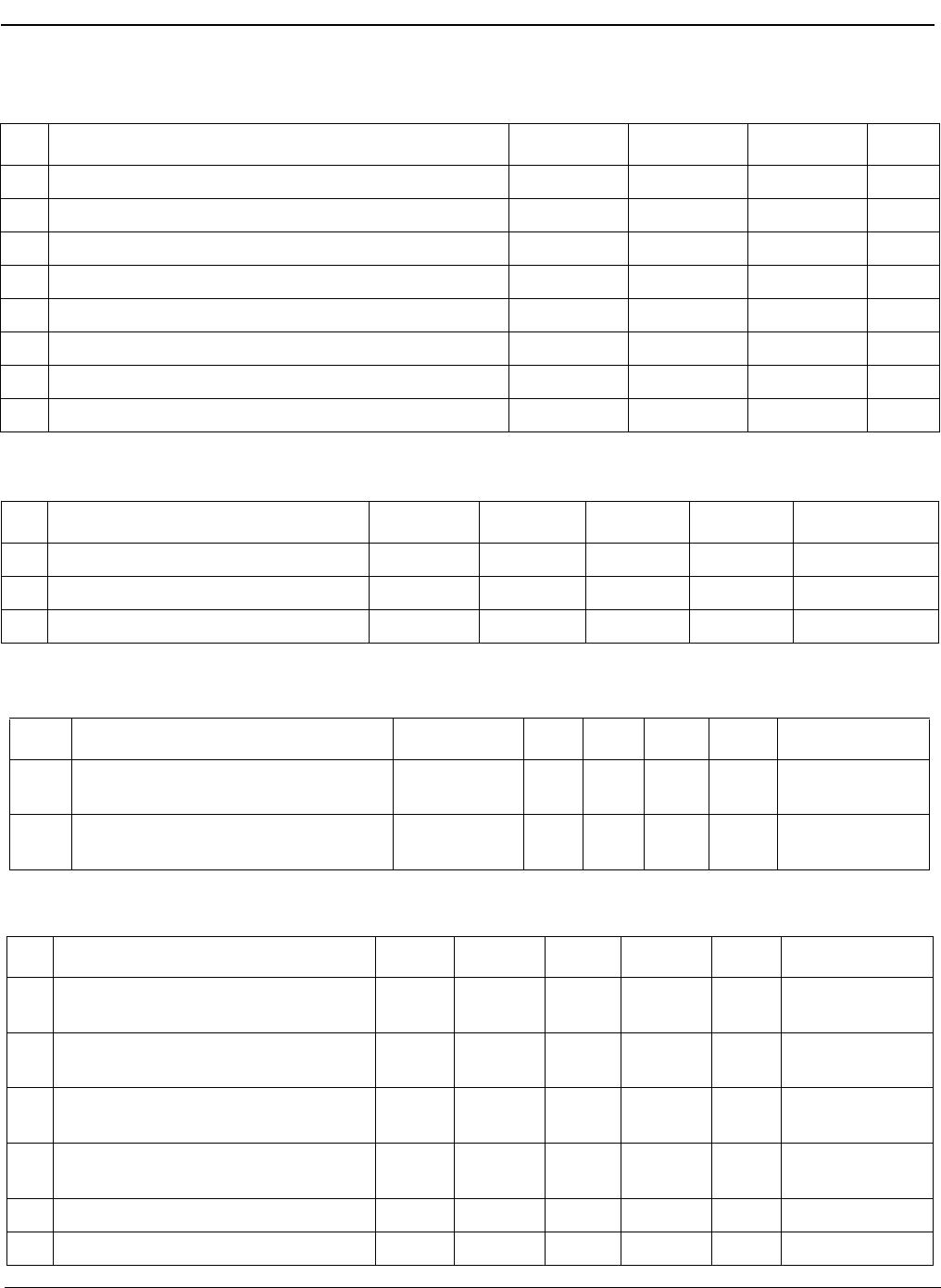

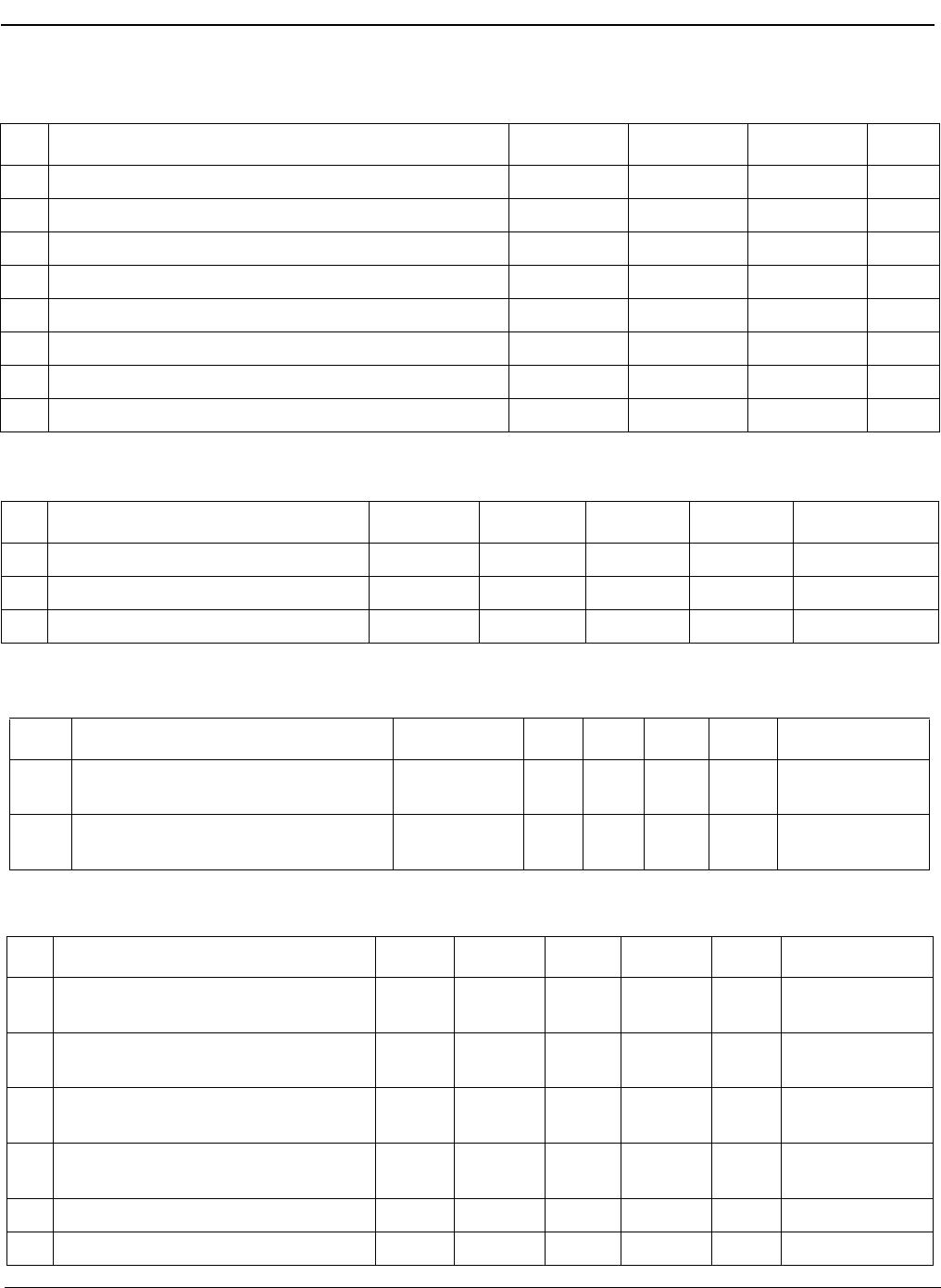

Absolute Maximum Ratings*

Parameter Sym. Min. Max. Units

1 Supply voltage V

DD_R

-0.5 4.6 V

2 Voltage on any digital pin V

PIN

-0.5 VDD V

4 LVPECL output current I

out

30 mA

5 Soldering temperature T 260 °C

6 Storage temperature T

ST

-55 125 °C

7 Junction temperature T

j

125 °C

8 Voltage on input pin V

input

VDD V

9 Input capacitance each pin C

p

500 fF

ZL40205 Data Sheet

16

Microsemi Corporation

4.0 AC and DC Electrical Characteristics

* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

* Voltages are with respect to ground (GND) unless otherwise stated

Recommended Operating Conditions*

Characteristics Sym. Min. Typ. Max. Units

1 Supply voltage 2.5 V mode V

DD25

2.375 2.5 2.625 V

2 Supply voltage 3.3 V mode V

DD33

3.135 3.3 3.465 V

3 Operating temperature T

A

-40 25 85 °C

* Voltages are with respect to ground (GND) unless otherwise stated

DC Electrical Characteristics - Current Consumption

Characteristics Sym. Min. Typ. Max. Units Notes

1 Supply current LVPECL drivers -

un

loaded

I

dd_unload

110 mA Unloaded

2

Supply current LVPECL drivers -

loa

ded (all outputs are active)

I

dd_load

209 mA Including power

to R

L

= 50Ω

DC Electrical Characteristics - Inputs and Outputs - for 3.3 V Supply

Characteristics Sym. Min. Typ. Max. Units Notes

1 CMOS control logic high-level

input

voltage

V

CIH

0.7*V

DD

V

2 CMOS control logic low

-level input

voltage

V

CIL

0.3*V

DD

V

3 CMOS control logic Input leakage

current

I

IL

1 µA V

I

= V

DD

or 0 V

4 Differential input common mode

volt

age

V

CM

1.1 2.0 V

5 Differential input voltage difference V

ID

0.25 1 V

6 Differential input resistance V

IR

80 100 120 ohm