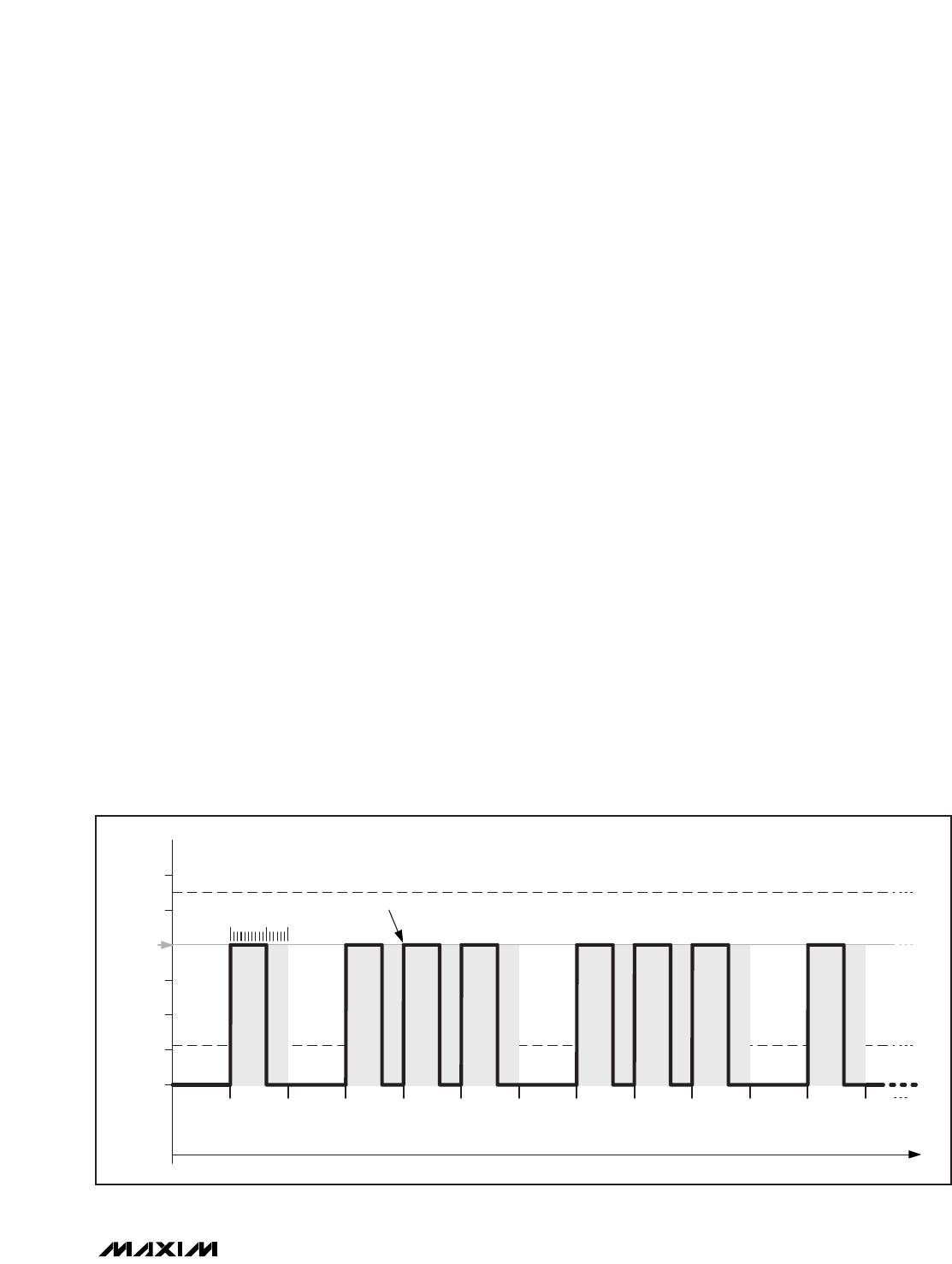

possible (shown in Figure 4 as subframes 1, 3, 4, 5, etc).

Each subframe can be ON for a PWM duration set by the

individual PWM value. The PWM value setting of

2560

DEC

out of 4096 (12-bit) results in a further reduction

of current ON time (shown in bold trace).

The internal PDM logic spreads the on subframes as

evenly as possible among the off subframes to keep

the effective scanning frequency high.

For applications with a slower clock speed, the

MAX6975 can increase the display refresh rate by a

factor of four to eliminate visible flicker. Setting configu-

ration bit D4 (GLB4) to 1 activates the increased

refresh rate (see Table 6). The increased refresh rate

reduces the number of global-intensity settings by a

factor of four (see Table 3).

MAX6974 Video-Frame Timing

The MAX6974 supports up to 60 video frames per

second (fps). The following equation shows the

required clock frequency to support 60 video fps:

60 (video fps) x 4096 (clocks per 12-bit PWM period) x

128 (global-intensity subframes) = 31.5MHz.

The MAX6974 supports up to a 33MHz clock signal

(~63fps).

Each 12-bit PWM period contains 4096 clock cycles;

multiply that number by 128 (number of global-intensity

subframes) to obtain the required number of clock cycles

(524,288) per video frame. The MAX6974 requires 36

bits (12 bits per color multiplied by three colors) to drive

an RGB pixel. The maximum pixel data that the

MAX6974 can send per video frame is 524,288 / 36 or

14,563 pixels, corresponding to 1820 cascaded

MAX6974s.

MAX6975 Video-Frame Timing

The MAX6975 also supports up to 60 video frames per

second (fps). The following equation shows the

required clock frequency to support 60 video fps:

60 (video fps) x 16,384 (clocks per 14-bit PWM period)

x 32 (global-intensity subframes) = 31.5MHz.

The MAX6975 supports up to a 33MHz clock signal

(~63fps).

Each 14-bit PWM period contains 16,384 clock cycles;

multiply 16,384 by 32 (global-intensity subframes) to

obtain the required number of clock cycles (524,288)

per video frame. The MAX6975 requires 42 bits (14 bits

per color multiplied by three colors) to drive an RGB

pixel. The maximum pixel data that the MAX6975 can

send per video frame is 524,288 / 42 or 12,483 pixels,

corresponding to 1560 cascaded MAX6975s.

Multiplexed vs. Nonmultiplexed Operation

The MAX6974/MAX6975 can double the number of

LEDs driven from 24 to 48 through multiplexing. When

multiplexing, the two outputs, MUX0 and MUX1, drive

MAX6974/MAX6975

24-Output PWM LED Drivers

for Message Boards

______________________________________________________________________________________ 11