MAX6974/MAX6975

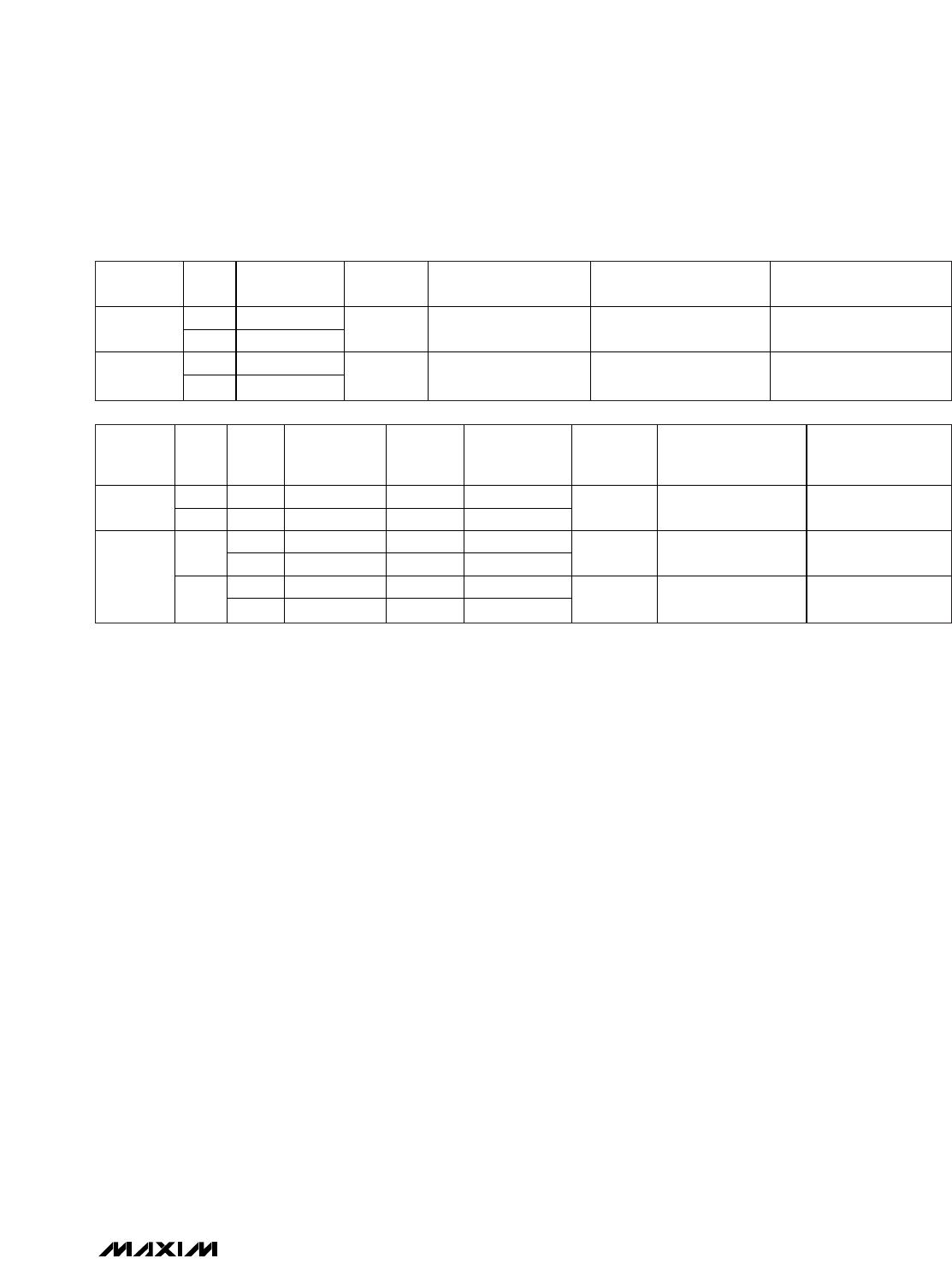

Each command is uniquely identified by two bits, C1

and C0, embedded in the serial-interface protocol

structure. The commands Load CALDAC, Load Global-

Intensity PDM, and Load Configuration each require 24

bits of data (3 bytes) for every cascaded device. The

number of bits required for the command load individual

PWM varies by device and multiplex mode of operation.

Each cascaded device can receive unique data for

CALDACs, global intensity, configuration, and individual

PWM output drivers. Generally, all cascaded devices

are operated in the same configuration mode. The data

bytes are transmitted MSB first for all commands. The

commands are communicated to all cascaded devices

by the host using the synchronous serial-interface and

protocol structure (see the

Serial Interface

section for

details). The four commands and the data lengths for

each command are shown in Table 4.

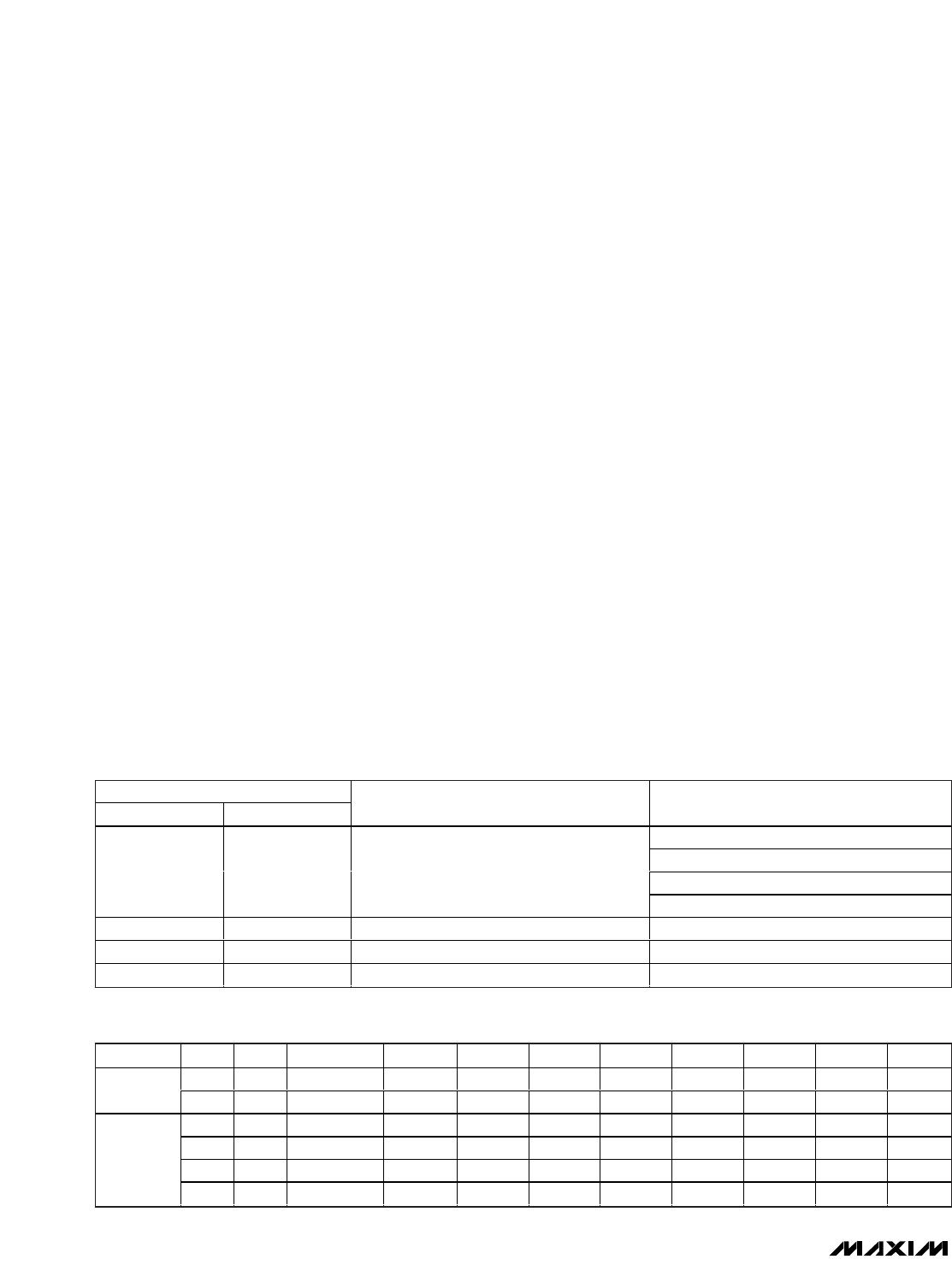

The MAX6974, operating in nonmultiplexed mode,

requires twenty-four 12-bit individual PWM data (288

bits total) and requires forty-eight 12-bit data (576 bits

total) in multiplexed operation mode. Similarly, the

MAX6975, operating in nonmultiplexed mode, requires

twenty-four 14-bit individual-intensity PWM data (336

bits total) and requires forty-eight 14-bit (672 bits total)

data in multiplexed mode. The individual PWM data are

loaded into an intermediate latch and transferred to the

actual PWM latches at subframe 0 and PWM clock 0.

The R, G, and B calibration DACs are loaded with 8-bit

data each in nonmultiplexed and multiplexed modes.

Data is updated immediately into the CALDAC latches

(see Table 8)

.

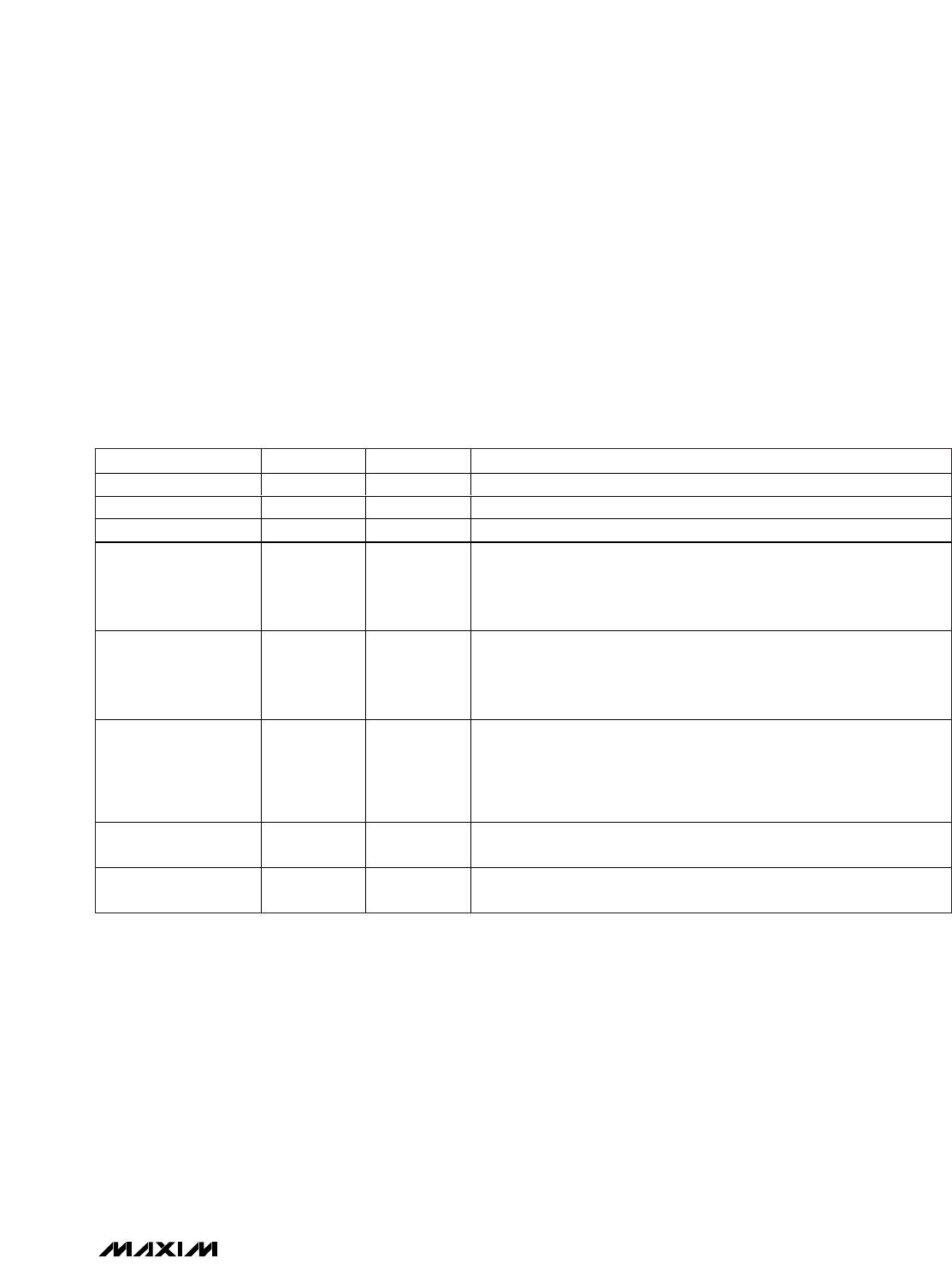

The MAX6974/MAX6975 require one data byte to set the

global-intensity PDM for all output drivers. The global-

intensity PDM data has a variable number of active bits

depending on the multiplex operating mode and, for

the MAX6975, the global-quarter setting. The number of

bits used for global-intensity control is always justified

to the LSB of the data byte, as shown in Table 5. One

byte of data is sent three times with the global-intensity

PDM data bits justified to the LSB. Data is updated into

the PWM latches at subframe 0 and PWM clock 0 (see

Table 9)

.

When using the MAX6975 5-bit global-intensity setting,

the settings range from 0 to 63 to set the global intensity

from 1 to 64 subframes ON to 64 out of 64 subframes ON.

When using the MAX6974 7-bit global-intensity setting,

the settings range from 0 to 127 to set the global inten-

sity from 1 out of 128 subframes ON to 128 out of 128

subframes ON.

24-Output PWM LED Drivers

for Message Boards

14 ______________________________________________________________________________________