MAX6974/MAX6975

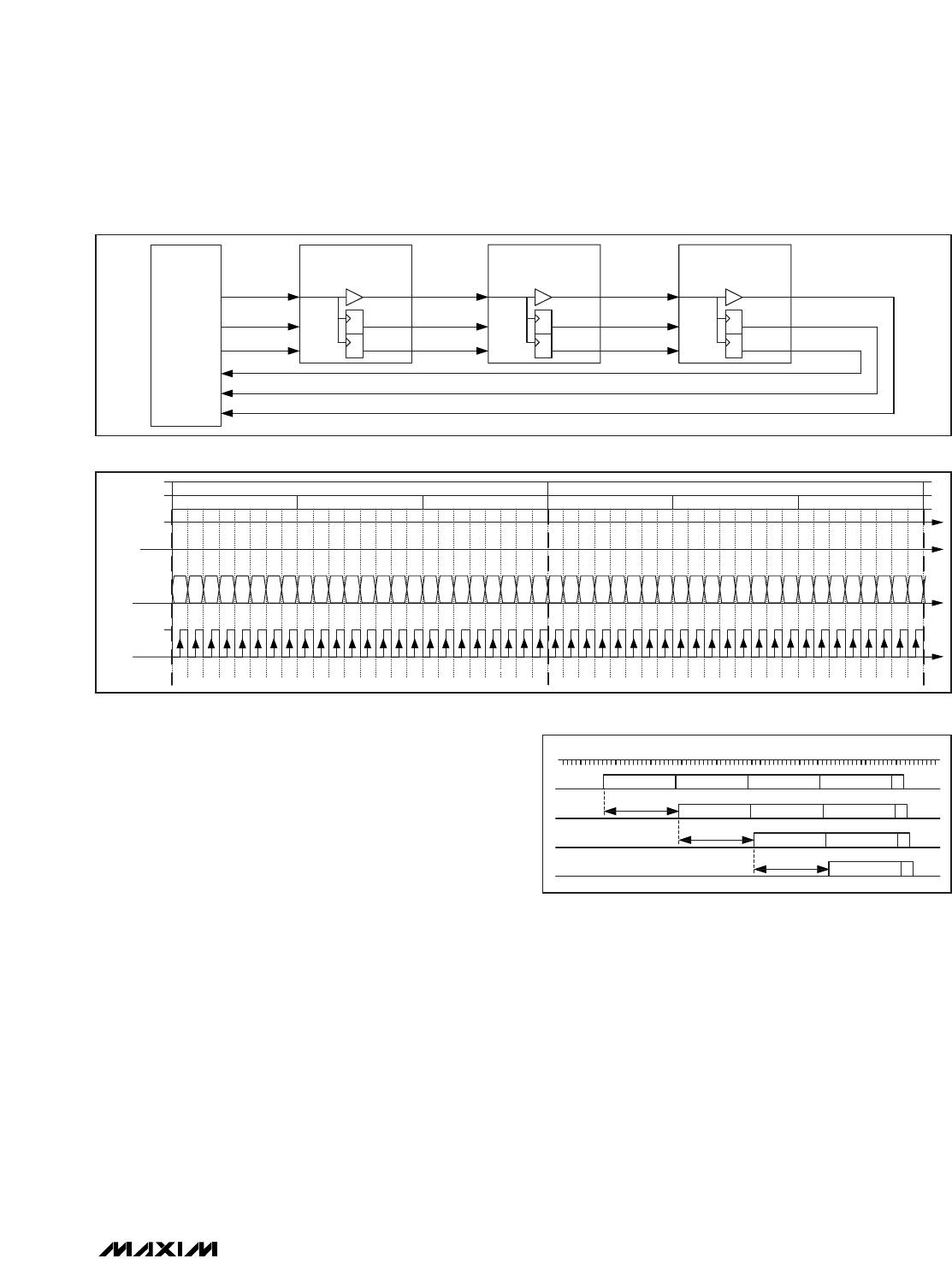

When the MAX6974/MAX6975 send individual-intensity

PWM data, the data segment bit length is large due to

the 12-bit or 14-bit PWM data for each of the 24 outputs

(see Figure 11). The various data segment bit lengths

for each of the four commands and different operating

modes is shown in Table 4. Data capturing is the same

as described above with the header segment outputs

and data being delayed by the full length of the data bit

stream being captured plus one clock cycle.

LED Open-Circuit and

Overtemperature Detection Counter

The MAX6974/MAX6975 feature LED open-circuit

detection and overtemperature detection that use the

counter section of the header segment to record

detected faults. Using commands 01 or 11 force the

counter to record LED open-circuit detection faults.

Using commands 00 or 10 force the counter to record

overtemperature faults.

The MAX6974/MAX6975 detect an open circuit on a driver

output by monitoring for output voltages below 200mV.

When an open circuit is detected, the MAX6974/

MAX6975 increment the counter segment data,

CNTR[9:0], received on DIN by 1 before transmitting a

header and new counter value out DOUT. Regardless

of the number of open-circuit outputs on a device, the

counter increment is 1.

The MAX6974/MAX6975 detect die temperatures above

T

DIE

= +165°C and disable all output drivers by setting

all PWM data to zero. During an overtemperature event,

the MAX6974/MAX6975 increment the counter segment

data, CNTR[9:0], received on DIN by 1 before transmitting

a header and new counter value out DOUT. The output

drivers are allowed to be on when the die temperature

falls below T

DIE

= +150°C.

When there is no fault detected, the counter data is

passed directly to DOUT unaltered.

Applications Information

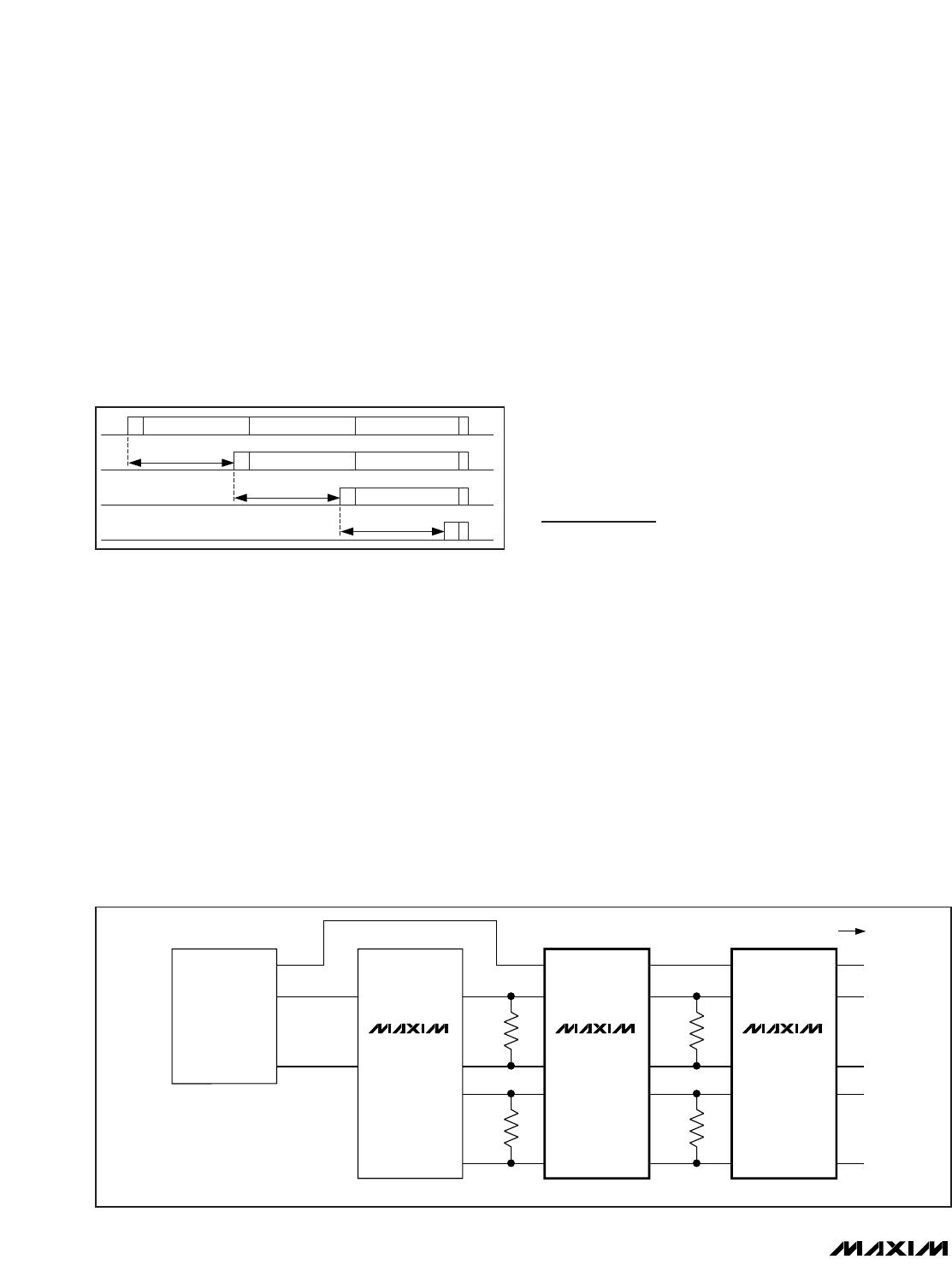

Terminations and PCB Layout

The MAX6974/MAX6975’s layout simplifies cascading

multiple devices, as the interface signals flow through

from each device. The synchronous and buffered

nature of the interface simplifies the board design, but

pay attention to signal routing and termination, as with

other high-speed logic circuits.

Terminate the differential input pairs, CLKI+ and CLKI-,

as well as DIN+ and DIN-, with a termination resistor as

close as possible to the package. When using the

MAX6974/MAX6975 as the signal source, use a 200Ω

termination resistor. When using a level translator or clock

retimer as the signal source, use a 110Ω termination

resistor. Route each differential input pair as close

parallel tracks with spacing or a GND trace between

the track pair and the next signal track to minimize

cross-coupling. Track lengths up to a few inches do not

require termination-matched tracks (transmission lines).

24-Output PWM LED Drivers

for Message Boards

20 ______________________________________________________________________________________