6

LTC1562

1562fa

PIN FUNCTIONS

UUU

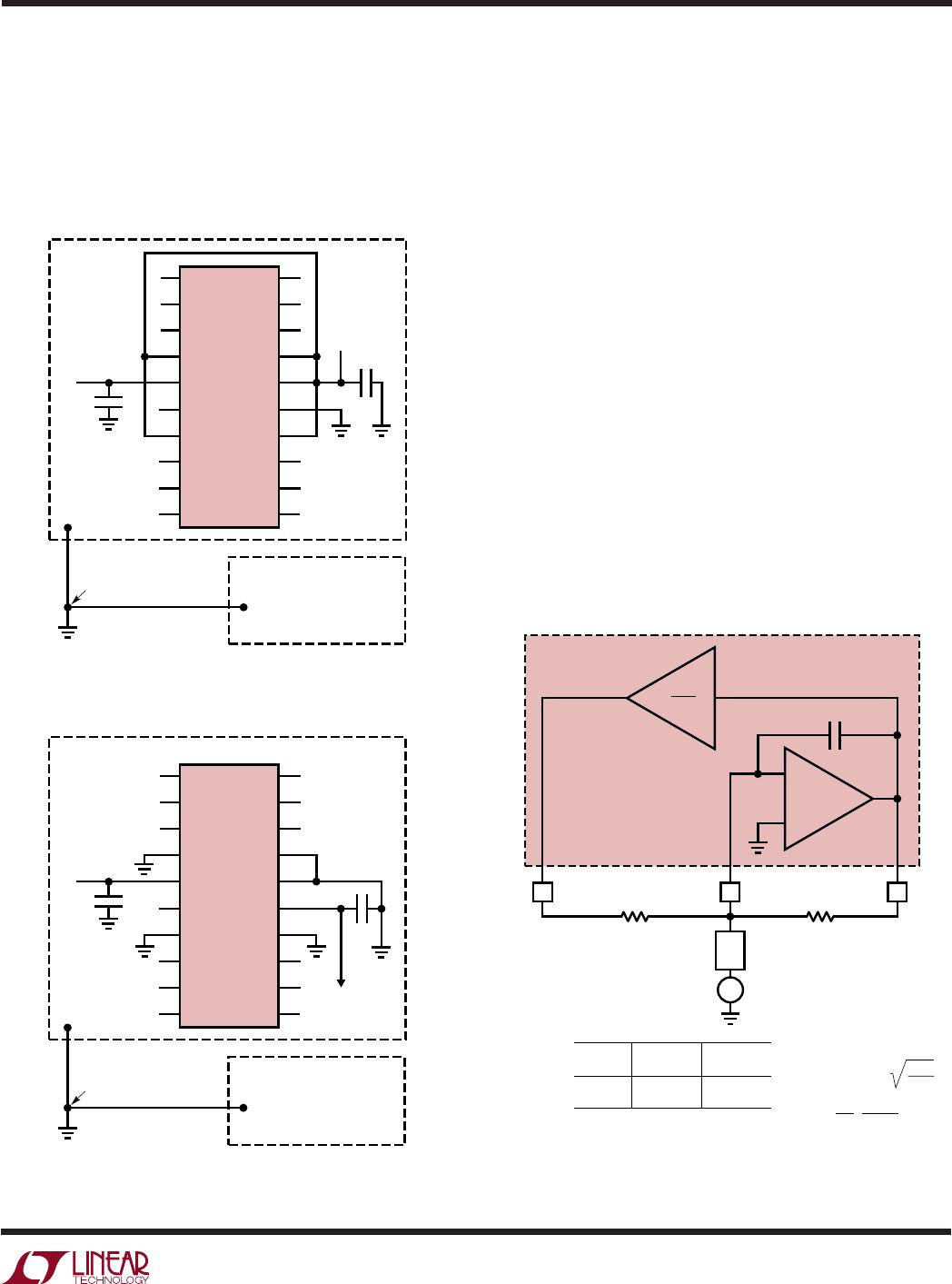

INV A, INV B, INV C, INV D: Each of the INV pins is a virtual-

ground summing point for the corresponding 2nd order

section. For each section, external components Z

IN

, R2,

R

Q

connect to the INV pin as shown in Figure 3 and

described further in the Applications Information. Note

that the INV pins are sensitive internal nodes of the filter

and will readily receive any unintended signals that are

capacitively coupled into them. Capacitance to the INV

nodes will also affect the frequency response of the filter

sections. For these reasons, printed circuit connections to

the INV pins must be kept as short as possible, less than

one inch (2.5cm) total and surrounded by a ground plane.

V1 A, V1 B, V1 C, V1 D: Output Pins. Provide a bandpass,

highpass or other response depending on external cir-

cuitry (see Applications Information section). Each V1 pin

also connects to the R

Q

resistor of the corresponding 2nd

order filter section (see Figure 3 and Applications Informa-

tion). Each output is designed to drive a nominal net load

of 5kΩ and 30pF, which includes the loading due to the

external R

Q

. Distortion performance improves when the

outputs are loaded as lightly as possible. Some earlier

literature refers to these outputs as “BP” rather than V1.

V2 A, V2 B, V2 C, V2 D: Output Pins. Provide a lowpass,

bandpass or other response depending on external cir-

cuitry (see Applications Information section). Each V2 pin

also connects to the R2 resistor of the corresponding 2nd

order filter section (see Figure 3 and Applications Informa-

tion). Each output is designed to drive a nominal net load

of 5kΩ and 30pF, which includes the loading due to the

external R2. Distortion performance improves when the

outputs are loaded as lightly as possible. Some earlier

literature refers to these outputs as “LP” rather than V2.

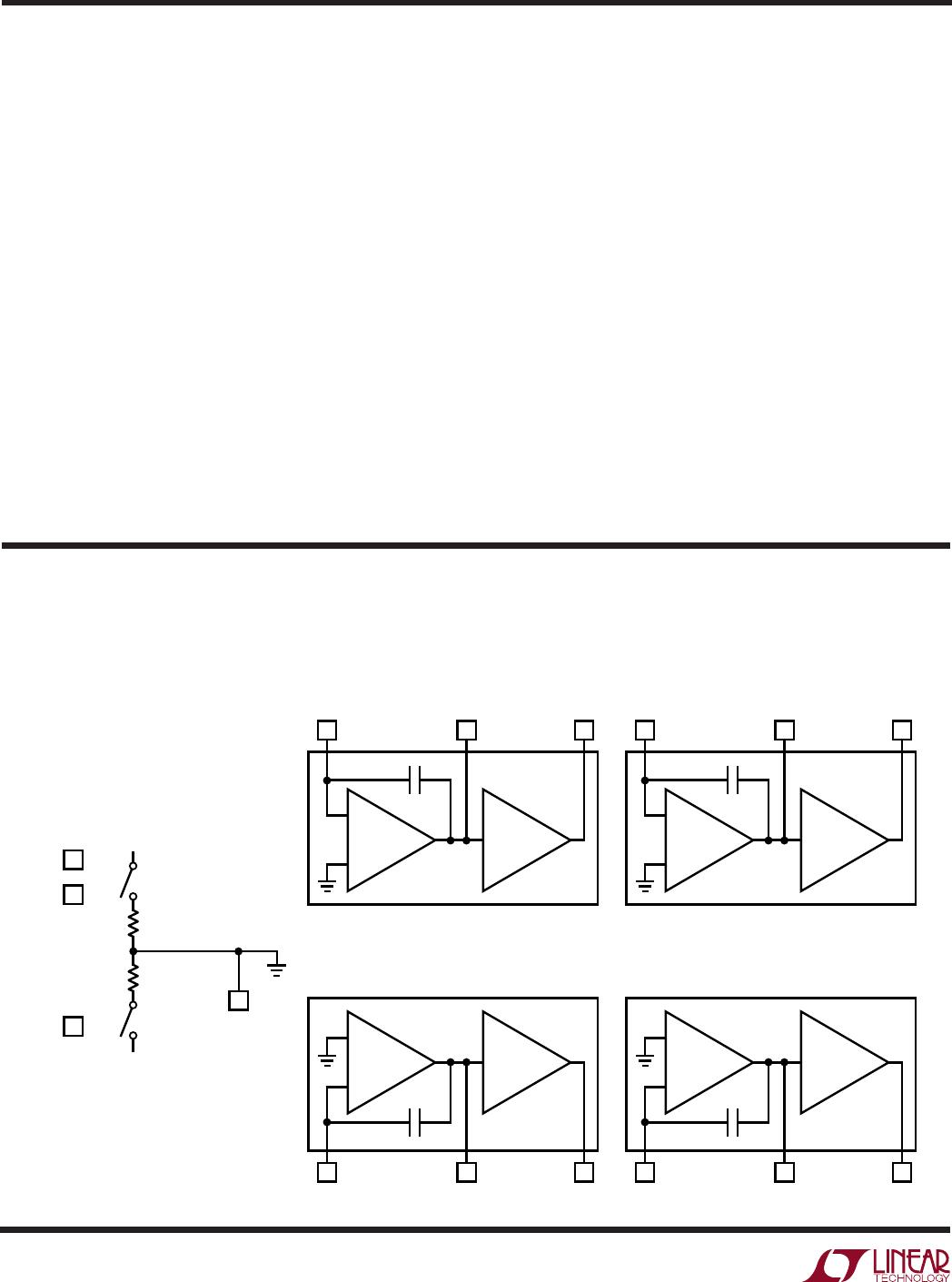

BLOCK DIAGRA

W

Overall Block Diagram Showing Four 3-Terminal 2nd Order Sections

V

+

V

–

SHDN

1562 BD

2ND ORDER SECTIONS

R

R

INV V1 V2

C

SHUTDOWN

SWITCH

SHUTDOWN

SWITCH

AGND

V

+

V

–

–

+

INV V1 V2

INV V1 V2 INV V1 V2

C

CC

AB

DC

–

+

–

+

–

+

∫∫

∫∫