IDT

®

Low Power Clock for Intel Atom

®

-Based Systems 1561C — 08/24/11

9LPRS436C

Low Power Clock for Intel Atom

®

-Based Systems

13

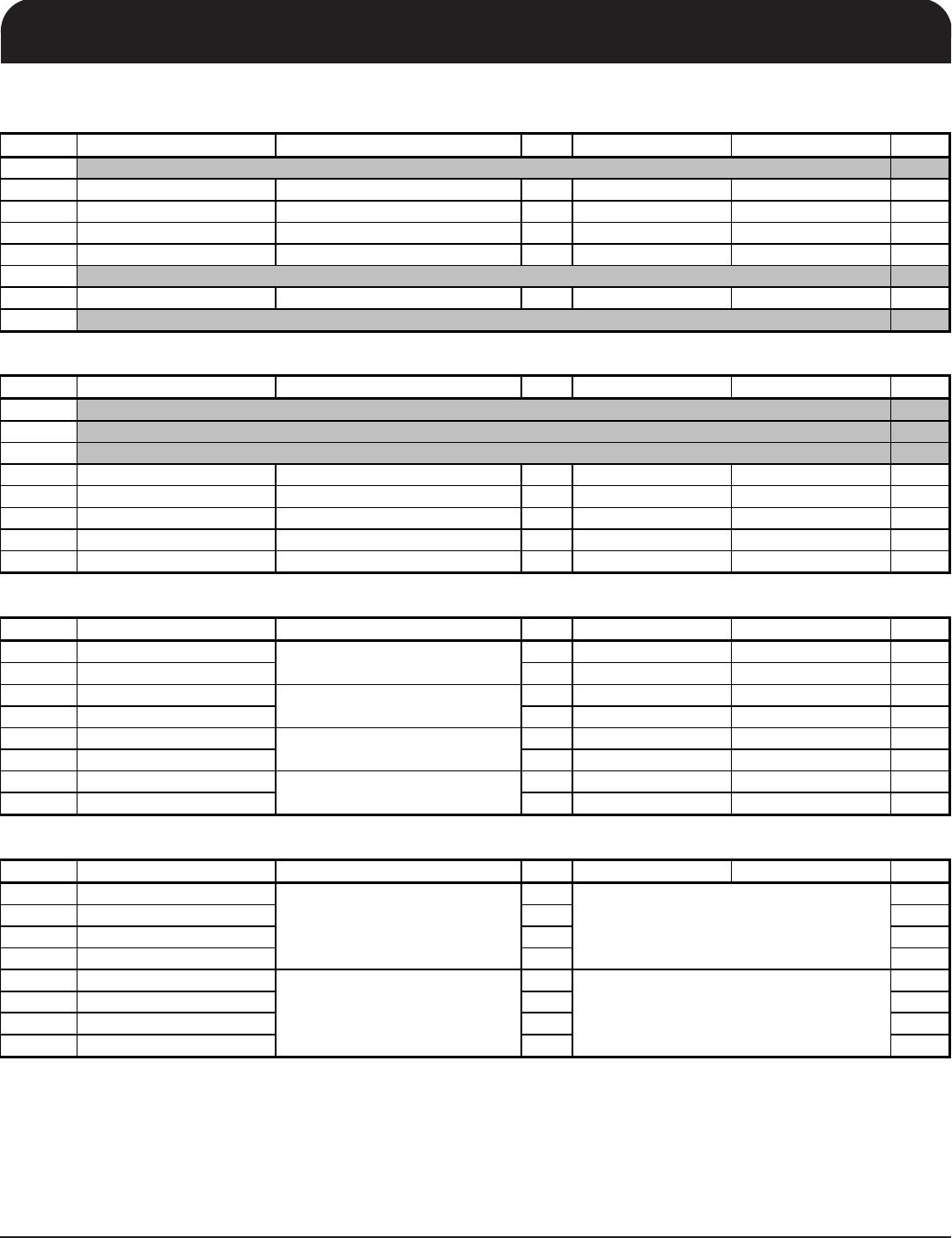

SMBus Table: Frequency Select Register

Byte 0 Name Control Function Type 0 1 PWD

Bit 7

Reserved 0

Bit 6

Reserved 0

Bit 5

Spread Enable

Enables Spread for

CPU/SRC/PCI outputs

RW Off 0.5% down spread 0

Bit 4

FS4 Freq Select Bit 4 RW Latch

Bit 3

FS3 Freq Select Bit 3 RW Latch

Bit 2

FSLC Freq Select Bit 2 RW Latch

Bit 1

FSLB Freq Select Bit 1 RW Latch

Bit 0

FSLA Freq Select Bit 0 RW Latch

SMBus Table: Output Control Register

Byte 1 Name Control Function Type 0 1 PWD

Bit 7

DOT96Mhz Output Enable RW Disable Enable 1

Bit 6

SATA/PCIe3 Output Enable RW Disable Enable 1

Bit 5

ITP/PCIe2 Output Enable RW Disable Enable 1

Bit 4

PCIe1 Output Enable RW Disable Enable 1

Bit 3

PCIe0 Output Enable RW Disable Enable 1

Bit 2

12.288MHz

Output Enable (Disabling This

output also disables the

12.288M PLL).

RW Disable Enable 1

Bit 1

25MHz

25MHz free running during VDD

Suspend (S-states). If this bit is

set to 0, the XTAL OSC will also

be powered down in the

Suspend States)

RW Does Not Run Runs 1

Bit 0

CPU PLL MN_EN CPU PLL M/N Enable RW Disable Enable 0

SMBus Table: Output Control Register

Byte 2 Name Control Function Type 0 1 PWD

Bit 7

USB_48MHz Output Enable RW Disable Enable 1

Bit 6

0

Bit 5

REF0 Output Enable RW Disable Enable 1

Bit 4

25MHz Output Enable RW Disable Enable 1

Bit 3

12_48MHz Output Enable RW Disable Enable 1

Bit 2

PCICLK_F0 Output Enable RW Disable Enable 1

Bit 1

PCICLK0 Output Enable RW Disable Enable 1

Bit 0

0

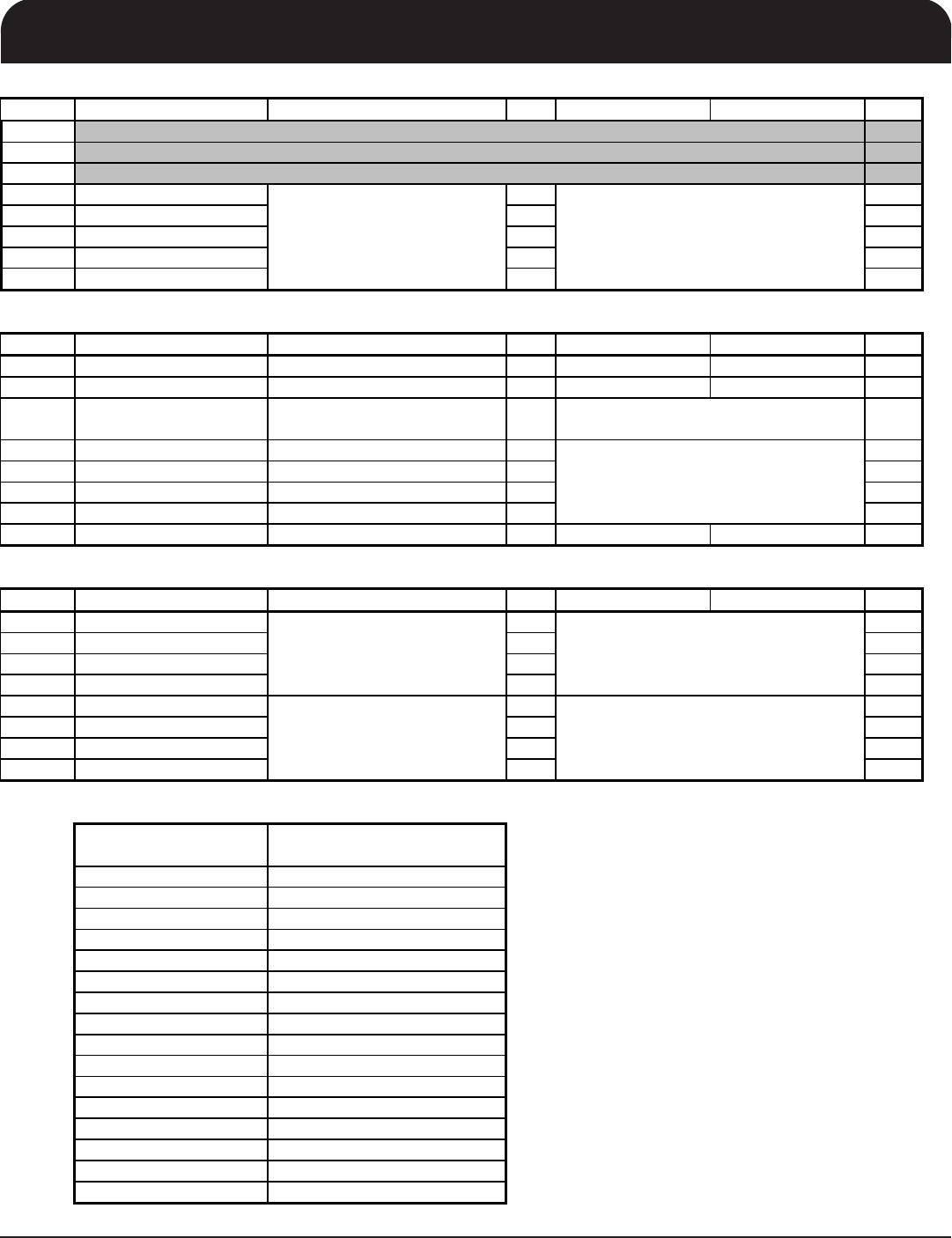

SMBus Table: Output Control Register

Byte 3 Name Control Function Type 0 1 PWD

Bit 7

CPUCLK1 Output Enable RW Disable Enable 1

Bit 6

CPUCLK0 Output Enable RW Disable Enable 1

Bit 5

PEREQ3# Control PCIEX1 is controlled RW Not Controlled Controlled 0

Bit 4

PEREQ3# Control PCIEX2 is controlled RW Not Controlled Controlled 0

Bit 3

PEREQ2# Control PCIEX1 is controlled RW Not Controlled Controlled 0

Bit 2

PEREQ2# Control SATACLK is controlled RW Not Controlled Controlled 0

Bit 1

PEREQ1# Control PCIEX0 is controlled RW Not Controlled Controlled 0

Bit 0

PEREQ1# Control SATACLK is controlled RW Not Controlled Controlled 0

NOTE: Only 1 PEREQ at a time can be selected to control an output.

Reserved

Reserved

See Table 1: CPU/SRC/PCI PLL

Frequency Selection Table