Valley Current Mode Control Buck Converter

A4403

10

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

The amount of capacitance required for a given ripple voltage can

be found:

C

IN

=

.

I

rms

× T

on

V

RIPPLE

(15)

As mentioned in the previous section, E-field biasing effects

can reduce the actual capacitance and this should be taken into

account when making the selection.

Again, there is generally no need to consider the heating effects

of the RMS current flowing through the ESR of a ceramic

capacitor. If an electrolytic device is used, then the ripple current

rating should be considered. Note that most manufacturers only

consider the RMS current rating at 100 kHz.

Recirculation Diode This diode (D1) conducts during the

switch off-time. A Schottky diode is recommended to minimize

both the forward drop and switching losses. The worst-case

dissipation occurs at maximum V

IN

, when the duty cycle is at a

minimum.

The average current through the diode can be found:

I

DIODE(av)

= I

LOAD

× (1 – D (min)) . (16)

The forward voltage drop, V

f

, can be found from the diode

characteristics by using the actual load current (not the average

current).

The static power dissipation can be found:

P

STAT

= I

DIODE(av)

× V

f

. (17)

It is also important to take into account the thermal rating of

the package, R

θJA

, and the ambient temperature, to ensure that

enough heatsinking is provided to maintain the diode junction

temperature within the safe operating area for the device.

To minimize the heating effects from the A4403 on the diode and

vice-versa, it is recommended that the diode be mounted on the

reverse side of the printed circuit board.

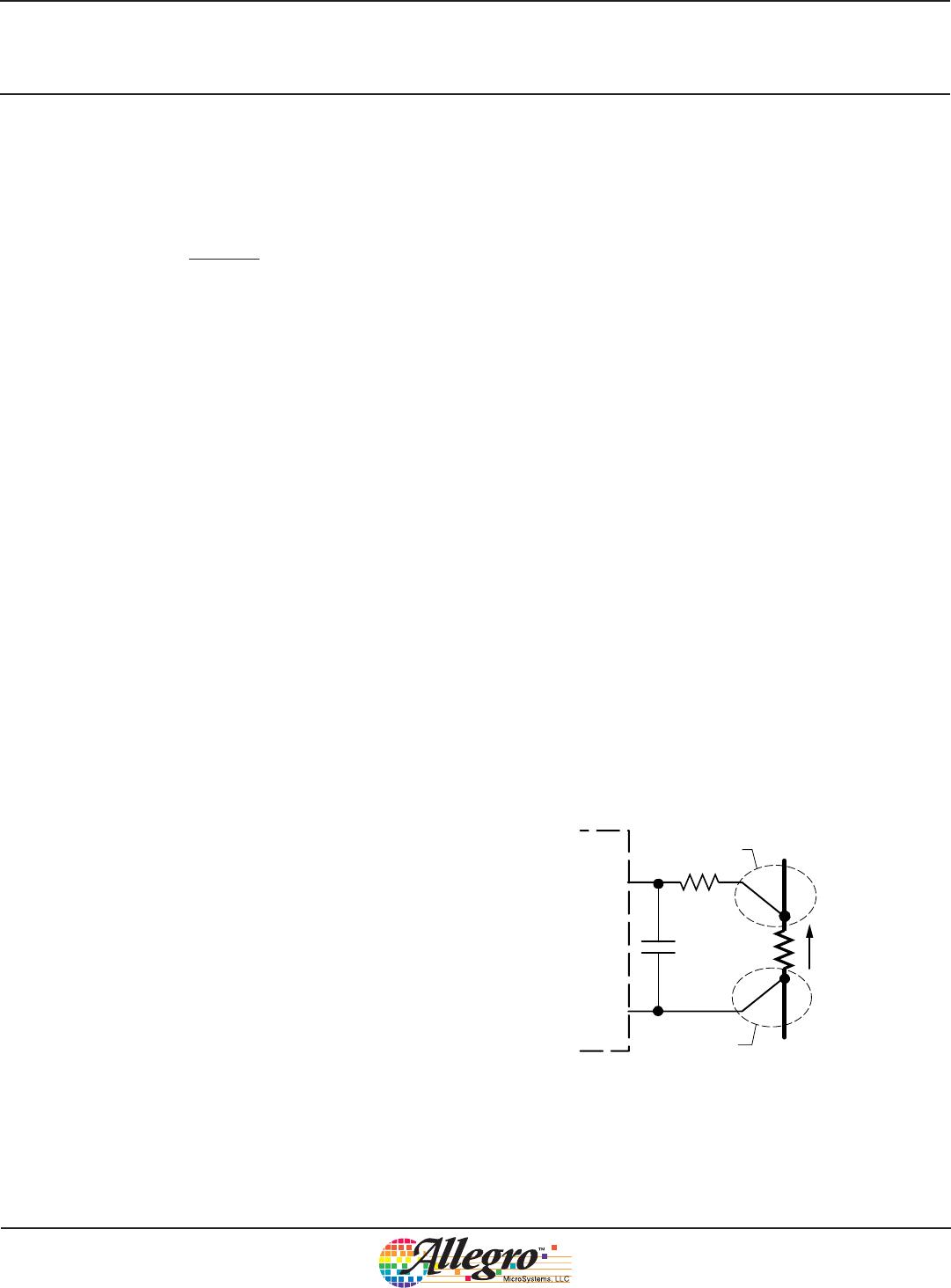

Sense Resistor The sense resistor should be a surface mount

package, with low inductance. On no account should a wire-

wound or through hole package be used. To prevent potential

mistriggering problems from occurring in noisy systems, it is

recommended that an R-C filter be applied across the sense resis-

tor, as shown in figure 3.

The sense resistor value is selected depending on the maximum

output load current. The typical sense voltage that causes a cur-

rent limit is 180 mV. So, for example, a 50 m value would be

appropriate for a maximum load of 3 A, as it allows for margin

between maximum load and the current limit. A tolerance of up to

±5% is acceptable.

The power rating of the resistor has to be considered. The current

flowing in the resistor is essentially the same as the current flow-

ing through the recirculation diode, although the power dissipa-

tion is worked out using the RMS current.

To a first approximation, the sense resistor dissipation can be

worked out as:

P

SENSE

= I

LOAD

2

× (1 – D (min)) × R

SENSE

. (18)

For a converter working with a load of 3 A, a very narrow duty

cycle, and a sense resistor of 50 m, the power dissipation would

be 450 mW.

The optimal solution from a cost perspective is to use two

100 m, 1206-style resistors connected in parallel. Each resistor

is generally rated at 250 mW at 70°C ambient. Check the vendor

datasheet to verify the maximum ambient at full power.

When laying out the PCB, it is essential that the sense resistor

connections, carrying the power current (see figure 3), are as

short and wide as possible to minimize the effects of leakage

inductance noise. In addition, the Kelvin sense circuit connec-

tions should be as close to the sense resistor pads as possible.

Figure 3. R-C filter added to the current sense circuit

ISEN

Kelvin

connection

Kelvin

connection

A4403

SGND

47

R

FILTER

R

SENSE

Power

current

1 nF

C

FILTER