Valley Current Mode Control Buck Converter

A4403

13

Allegro MicroSystems, LLC

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

To avoid ground offset issues in the output voltage, it is highly

recommended that the ground-referenced feedback resistor R6

should be connected directly to the GND connection of the

A4403. In other words, the R6 ground return should avoid the use

of the internal ground plane.

All ground-referenced support components (C5 and the DIS

switch) should also be located as close to the GND connection as

possible. A “local quiet” ground plane around these components

can be implemented; however, this ground plane should have a

high impedance connection to the star ground connection of the

power stages, as referenced below.

The sense resistor connections should be connected in a Kelvin

circuit (see figure 3) to the corresponding pins on the A4403

(ISEN and SGND). Note that it is imperative that the PCB traces

between the sense resistor pads and the sense connections are as

short as possible to minimize the effects of leakage inductance.

In noisy systems, it is highly recommended that an R-C filter be

used to filter the signal produced across the ISEN pin. See the

Sense Resistor section and the Typical Application schematic.

If an internal ground plane is used, it is recommended that it

does not overlap the switching node, LX, to avoid the possibility

of noise pick up. To minimize the possibility of noise injection

issues, it is recommended to isolate the ground plane around the

high impedance nodes, such as FB and SS.

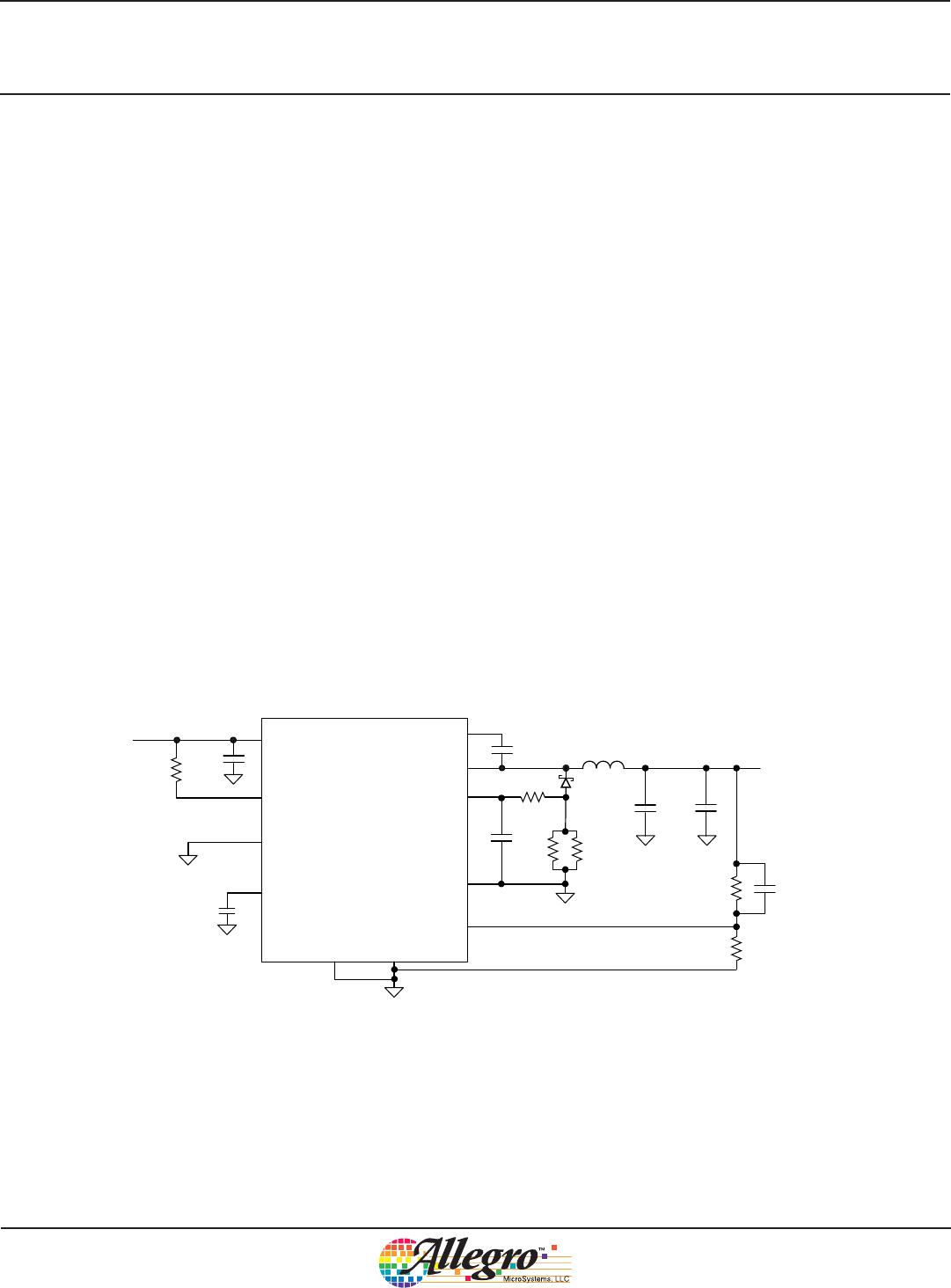

Q

L

R

LOAD

VIN

V

OUT

D

C

OUT

C

IN

LX

Star Connection

R

Input

Voltage

Figure 5. FET on-cycle current conduction paths

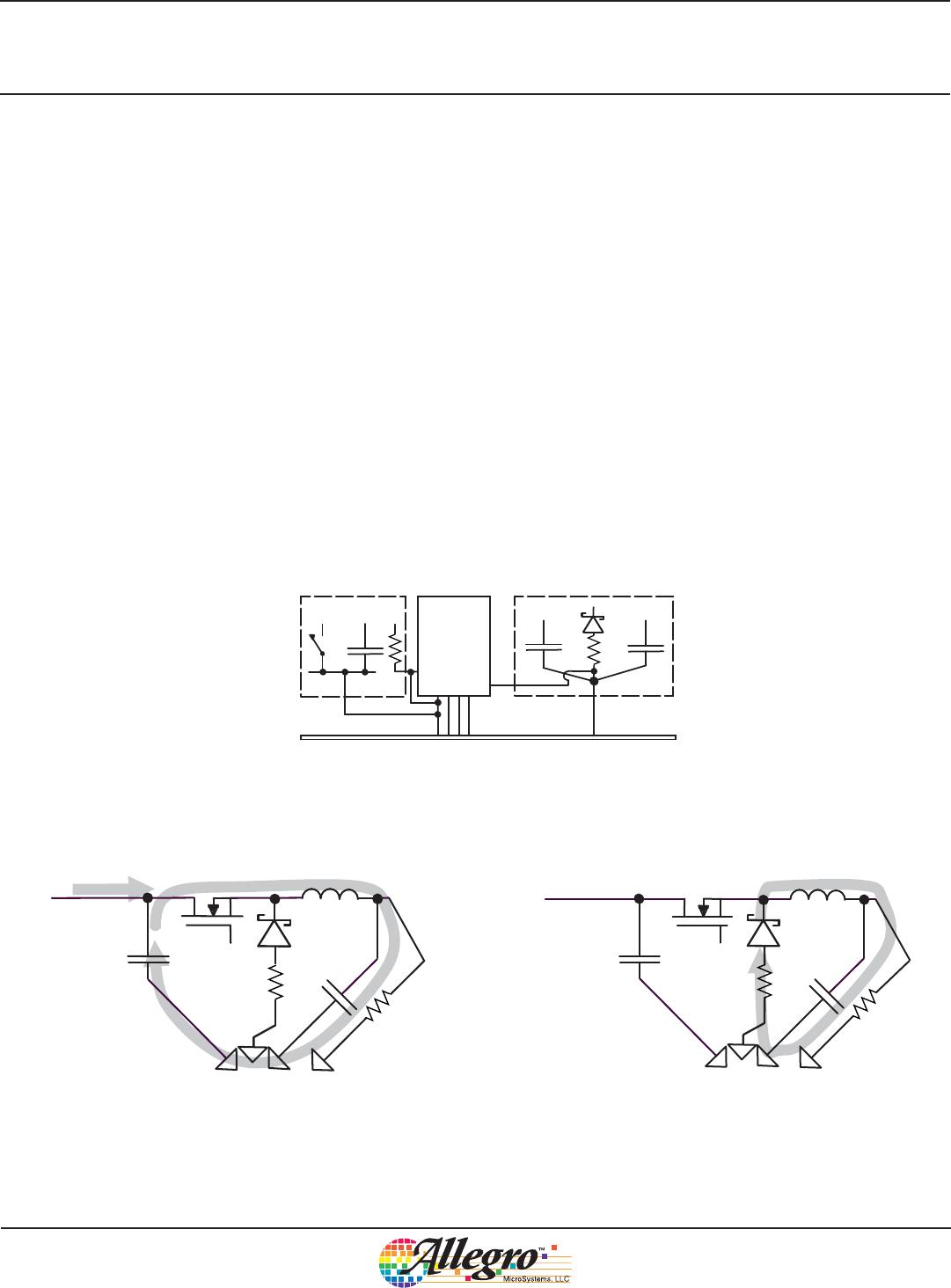

Q

L

VIN

LX

Star Connection

D

R

Input

Voltage

R

LOAD

V

OUT

C

OUT

C

IN

Figure 6. FET off-cycle current conduction paths

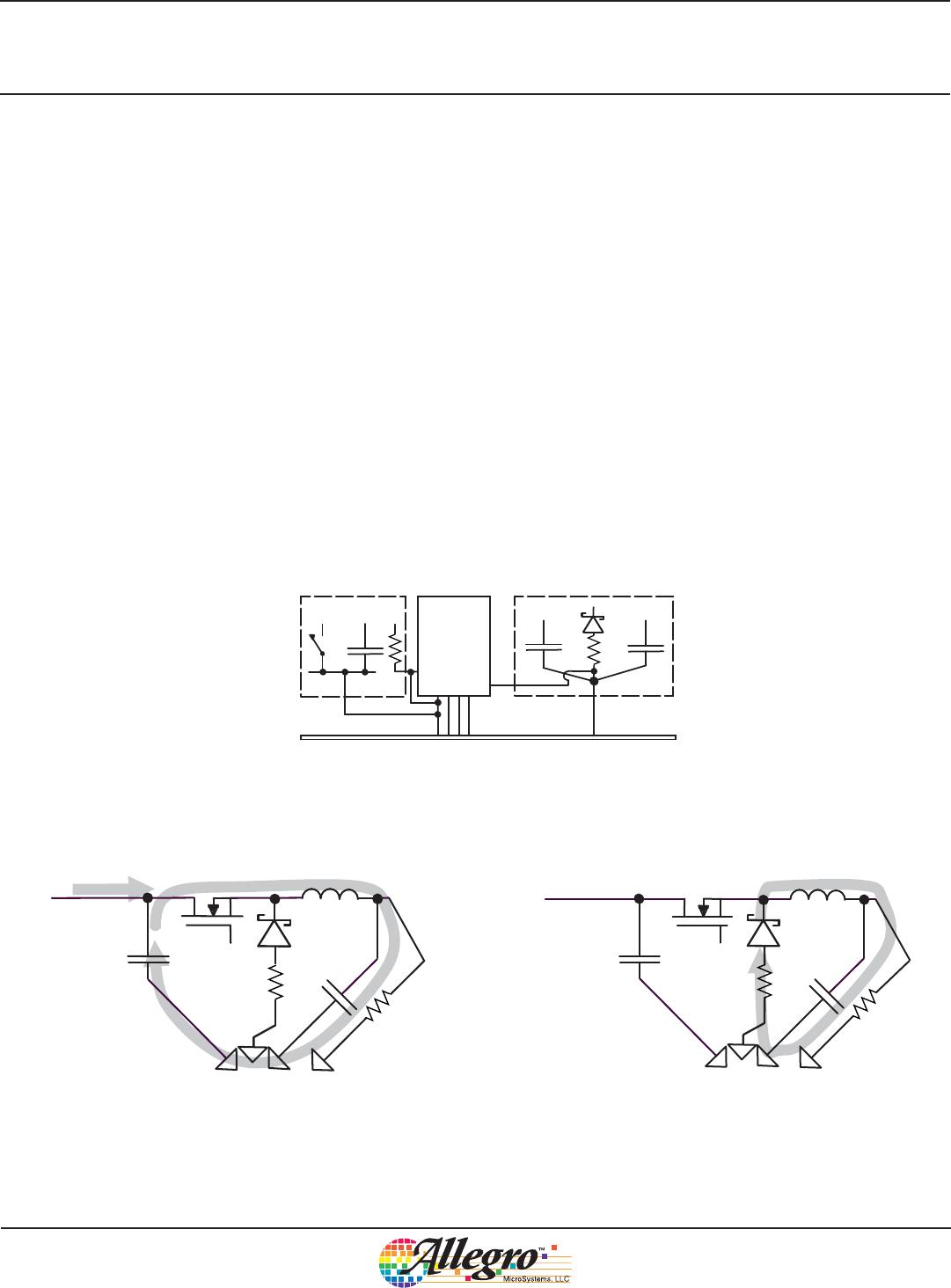

Cin

Cout

D

Star Connection

A4403

Internal Ground Plane

Thermal Vias

Power Circuitry

A4403 Support

Com

onents

Local ‘quiet’

Ground Plane

GND

R

R6

Switch

C5

SGND

Figure 4. Ground plane configurations