ADF4113HV Data Sheet

Rev. B | Page 10 of 20

PHASE FREQUENCY DETECTOR (PFD) AND

CHARGE PUMP

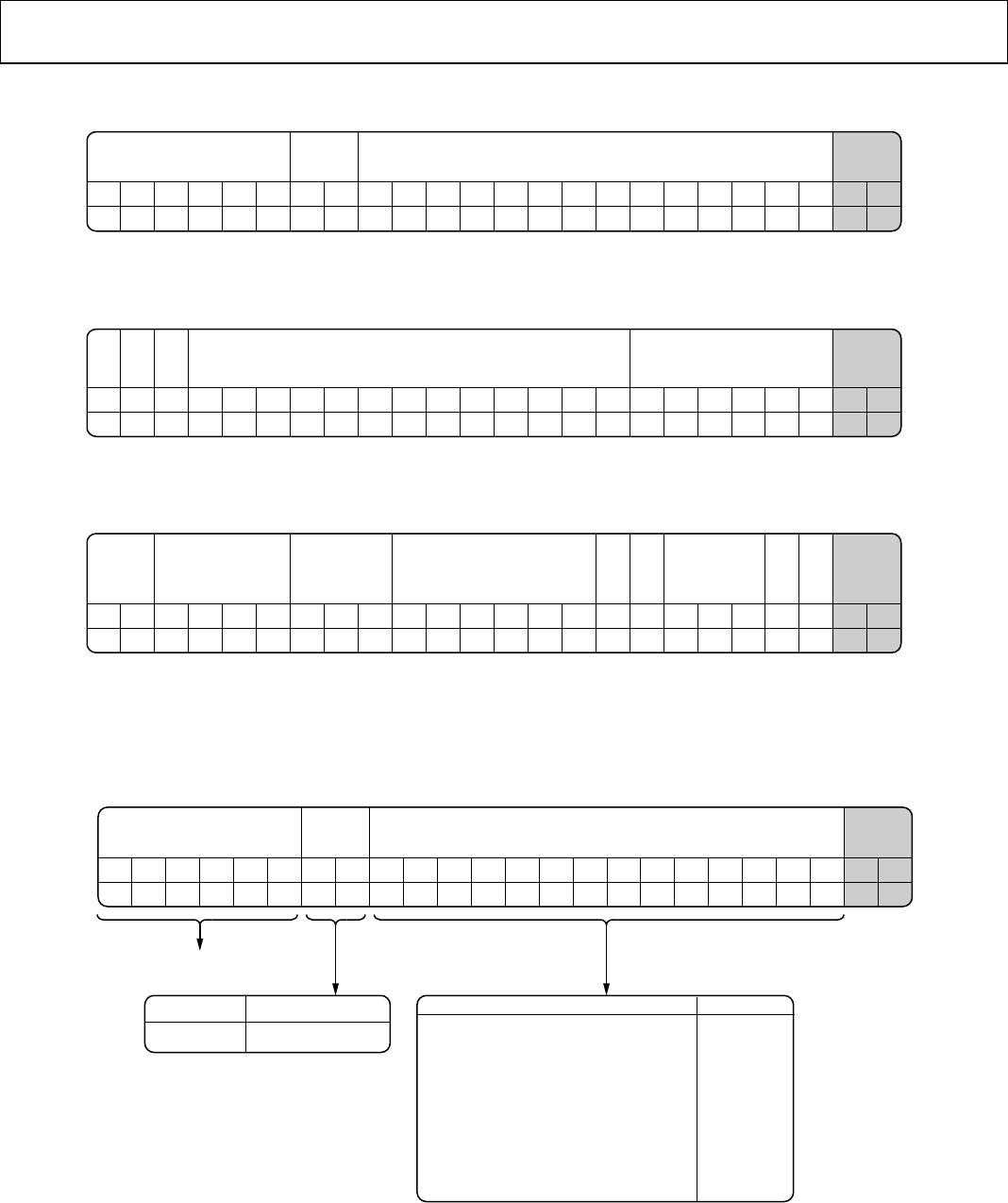

The PFD takes inputs from the R counter and N counter and

produces an output proportional to the phase and frequency

difference between them. Figure 17 is a simplified schematic.

The PFD includes a programmable delay element that controls

the width of the antibacklash pulse. This pulse ensures that

there is no dead zone in the PFD transfer function and mini-

mizes phase noise and reference spurs. Two bits in the reference

counter latch, ABP2 and ABP1, control the width of the pulse.

See Figure 20. The only recommended setting for the antiback-

lash pulse width is 7.2 ns.

PROGRAMMABLE

DELAY

U3

CLR2

Q2

D2

U2

CLR1

Q1

D1

CHARGE

PUMP

DOWN

UP

HIGH

HIGH

U1

ABP1 ABP2

R DIVIDER

N DIVIDER

CP OUTPUT

R DIVIDER

N DIVIDER

CP

CPGND

V

P

06223-017

Figure 17. PFD Simplified Schematic and Timing (in Lock)

MUXOUT AND LOCK DETECT

The output multiplexer on the ADF4113HV allows the user to

access various internal points on the chip. The state of MUXOUT

is controlled by M3, M2, and M1 in the function latch. Figure 22

shows the full truth table (function latch map). Figure 18 shows

the MUXOUT section in block diagram form.

CO

NT

R

OL

MUX

DV

D

D

MUXOU

T

DGND

ANA

L

OG L

OCK

DETECT

D

IGI

T

A

L

L

O

CK

DE

TE

C

T

R

CO

UN

T

E

R

O

U

T

P

U

T

N

CO

UN

TE

R O

U

TP

U

T

S

DO

UT

06223-018

Figure 18. MUXOUT Circuit

Lock Detect

MUXOUT can be programmed for two types of lock detect:

digital lock detect and analog lock detect.

Digital lock detect is active high. When LDP in the AB counter

latch is set to 0, digital lock detect is set high when the phase

error on five consecutive phase detector (PD) cycles is less than

10 ns. With LDP set to 1, five consecutive cycles of less than

3 ns are required to set the lock detect. It stays high until a phase

error greater than 25 ns is detected on any subsequent PD cycle.

Operate the N-channel, open-drain, analog lock detect with a

10 kΩ nominal external pull-up resistor. When lock has been

detected, this output is high with narrow low-going pulses.

INPUT SHIFT REGISTER

The ADF4113HV digital section includes a 24-bit input shift

register, a 14-bit R counter, and a 19-bit N counter comprising

a 6-bit A counter and a 13-bit B counter. Data is clocked into

the 24-bit shift register on each rising edge of CLK, MSB first.

Data is transferred from the shift register to one of three latches

on the rising edge of LE. The destination latch is determined by

the state of the two control bits (C2, C1) in the shift register.

These are the two LSBs, DB1 and DB0, as shown in Figure 2.

The truth table for these bits is shown in Table 6. Figure 19

shows a summary of how the latches are programmed.

Table 6. C2, C1 Truth Table

Control Bits

C2 C1 Data Latch

0 0 R counter

0 1 N counter (A and B)

1 0 Function latch (including prescaler)