© Semiconductor Components Industries, LLC, 2016

January, 2016 − Rev. 4

1 Publication Order Number:

NB3H63143G/D

NB3H63143G

3.3 V / 2.5 V Programmable

OmniClock Generator

with Single Ended (LVCMOS/LVTTL) and

Differential (LVPECL/LVDS/ HCSL/CML)

Outputs with Individual Output Enable

and Individual VDDO

The NB3H63143G, which is a member of the OmniClock family, is

a one−time programmable (OTP), low power PLL−based clock

generator that supports any output frequency from 8 kHz to 200 MHz.

The device accepts fundamental mode parallel resonant crystal or a

single ended (LVCMOS/LVTTL) reference clock as input. It

generates either three single ended (LVCMOS/LVTTL) outputs, or

one single ended output and one differential

(LVPECL/LVDS/HCSL/CML) output. The output signals can be

modulated using the spread spectrum feature of the PLL

(programmable spread spectrum type, deviation and rate) for

applications demanding low electromagnetic interference (EMI).

Individual output enable pins OE[2:0] are available to enable/disable

the outputs. Individual output voltage pins VDDO[2:0] are available

to independently set the output voltage of each output. Up to four

different configurations can be written into the device memory. Two

selection pins (SEL[1:0]) allow the user to select the configuration to

use. Using the PLL bypass mode, it is possible to get a copy of the

input clock on any or all of the outputs. The device can be powered

down using the Power Down pin (PD#). It is possible to program the

internal input crystal load capacitance and the output drive current

provided by the device. The device also has automatic gain control

(crystal power limiting) circuitry which avoids the device overdriving

the external crystal.

Features

• Member of the OmniClock Family of Programmable

Clock Generators

• Operating Power Supply: 3.3 V ±10%, 2.5 V ±10%

• I/O Standards

♦ Inputs: LVCMOS/LVTTL, Fundamental Mode

Crystal

♦ Outputs: 1.8 V to 3.3 V LVCMOS/LVTTL

♦ Outputs: LVPECL, LVDS, HCSL and CML

• 3 Programmable Single Ended (LVCMOS/LVTTL)

Outputs from 8 kHz to 200 MHz

• 1 Programmable Differential Clock Output up to

200 MHz

• Input Frequency Range

♦ Crystal: 3 MHz to 50 MHz

♦ Reference Clock: 3 MHz to 200 MHz

• Configurable Spread Spectrum Frequency Modulation

Parameters (Type, Deviation, Rate)

• Individual Output Enable Pins

• Independent Output Voltage Pins

• Programmable Internal Crystal Load Capacitors

• Programmable Output Drive Current for Single Ended

Outputs

• Power Saving Mode through Power Down Pin

• Programmable PLL Bypass Mode

• Programmable Output Inversion

• Programming and Evaluation Kit Available for Field

Programming and Quick Evaluation

• Temperature Range −40°C to 85°C

• Packaged in 16−pin QFN

• These are Pb−Free Devices

Typical Applications

• eBooks and Media Players

• Smart Wearables, Smart Phones, Portable Medical and

Industrial Equipment

• Set Top Boxes, Printers, Digital Cameras and

Camcorders

www.onsemi.com

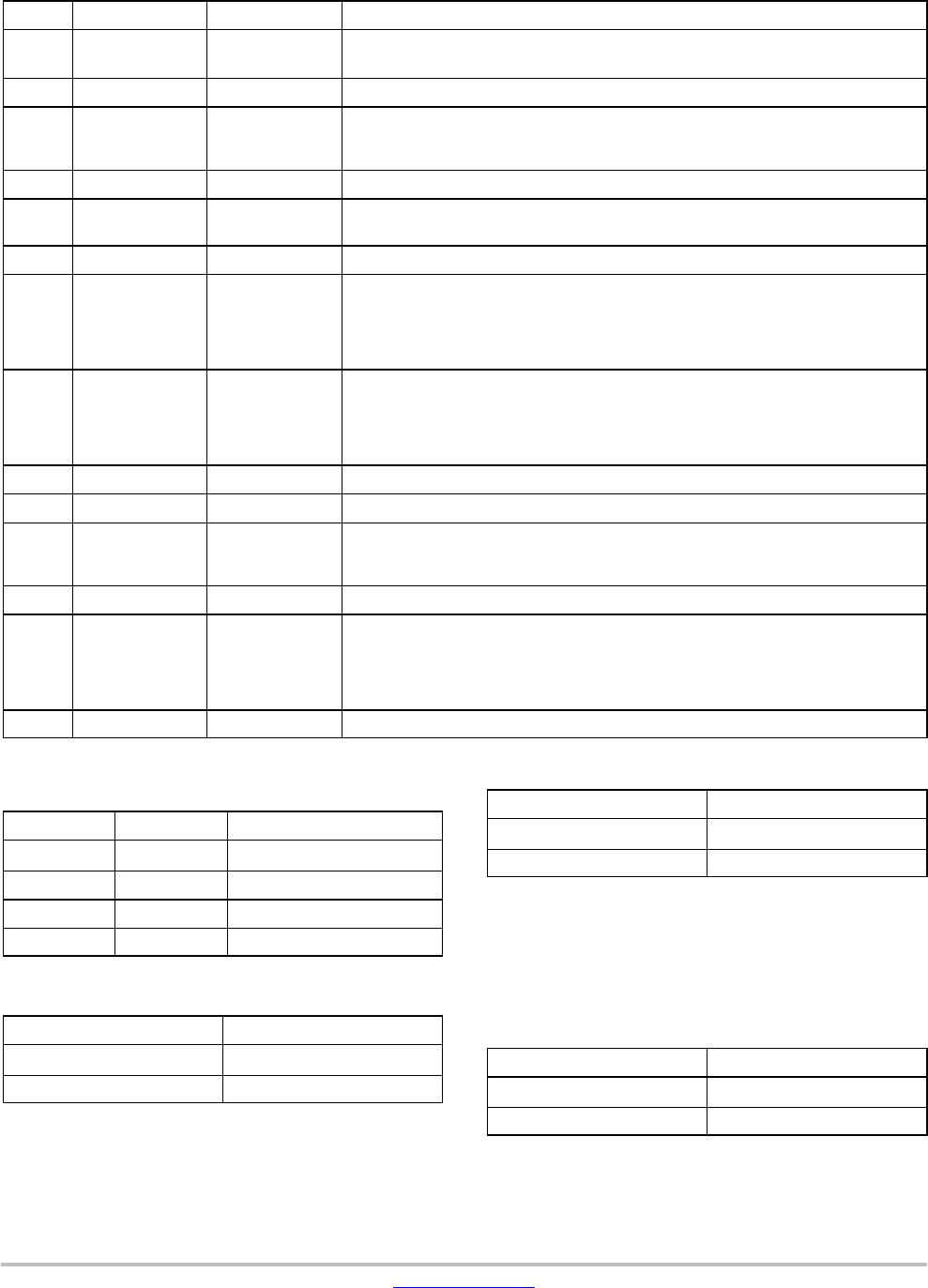

QFN16

CASE 485AE

MARKING DIAGRAM

See detailed ordering and shipping information on page 23 o

this data sheet.

ORDERING INFORMATION

1

3H63143G = Specific Device Code

xx = Specific Program Code (Default

‘00’ for Unprogrammed Part)

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

3H631

43Gxx

ALYWG

G

(Note: Microdot may be in either location)