NB3H63143G

www.onsemi.com

22

amplitude of the overshoots and subsequent ripples. The

ripple frequency is dependant on the signal travel time from

the receiver to the source. Shorter traces results in higher

ripple frequency, as the trace gets longer the travel time

increases, reducing the ripple frequency. The ripple

frequency is independent of signal frequency, and only

depends on the trace length and the propogation delay. For

eg. On an FR4 PCB with approximately 150 ps/inch of

propogation rate on a 2 inch trace, the ripple frequency = 1

/ (150 ps * 2 inch * 5) = 666.6 MHz; [5 = number of times

the signal travels, 1 trip to receiver plus 2 additional round

trips].

PCB traces should be terminated when trace length >= tr/f

/ (2* tprate); tf/t = rise/ fall time of signal, tprate =

propagation rate of trace.

Ringing

Overshoot

(Positive)

Overshoot

(Negative)

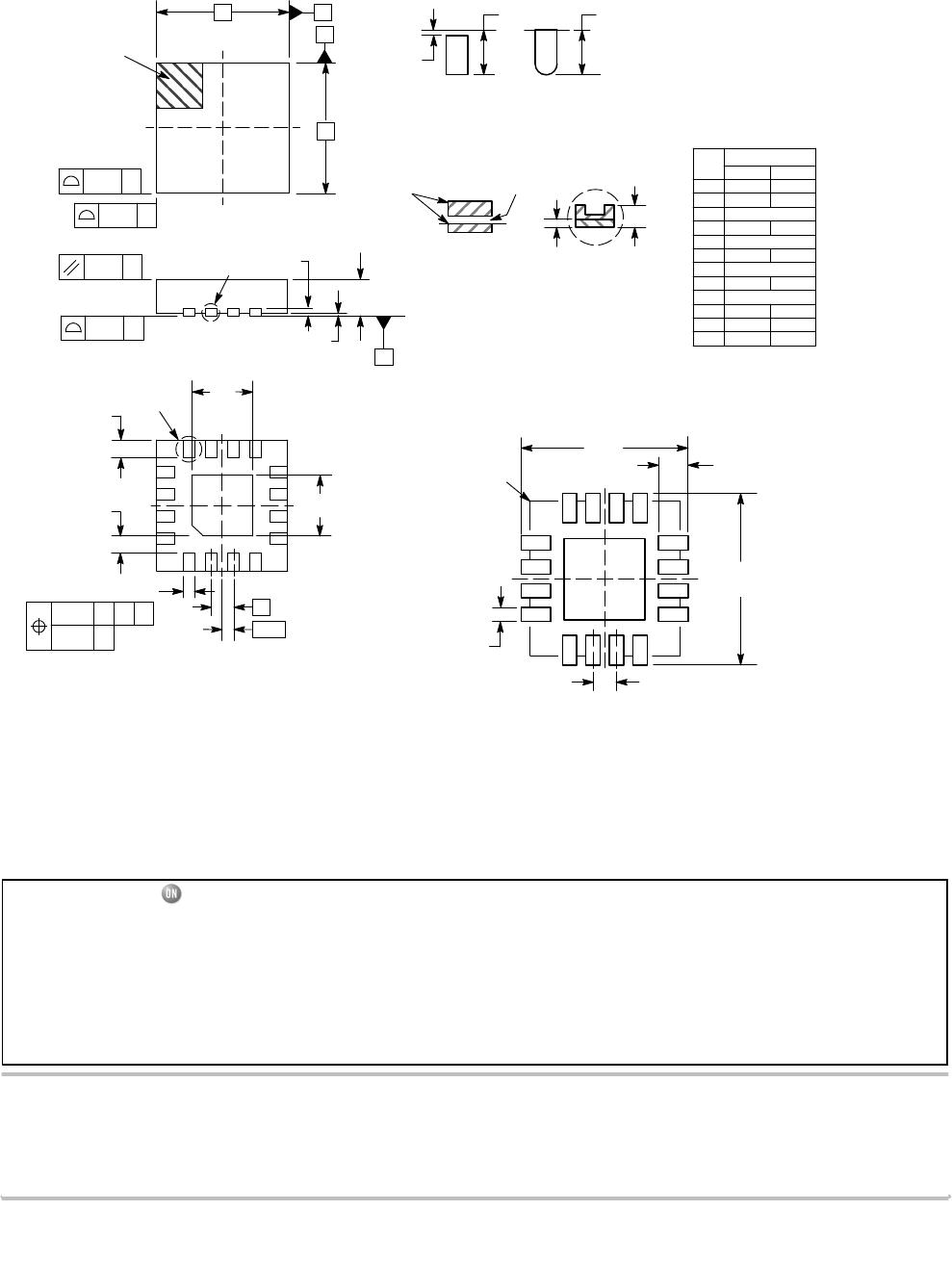

Figure 24. Signal Reflection Components

PCB Design Recommendation

For a clean clock signal waveform it is necessary to have

a clean power supply for the device. The device must be

isolated from system power supply noise. A 0.1 mF and a

2.2 mF decoupling capacitor should be mounted on the

component side of the board as close to the VDD pin as

possible. No vias should be used between the decoupling

capacitor and VDD pin. The PCB trace to VDD pin and the

ground via should be kept as thick and as short as possible.

All the VDD pins should have decoupling capacitors.

Stacked power and ground planes on the PCB should be

large. Signal traces should be on the top layer with minimum

vias and discontinuities and should not cross the reference

planes. The termination components must be placed near the

source or the receiver. In an optimum layout all components

are on the same side of the board, minimizing vias through

other signal layers.

Device Applications

The NB3H63143G is targeted mainly for the Consumer

market segment and can be used as per the examples below.

Clock Generator

Consumer applications like a Set top Box, have multiple

sub−systems and standard interfaces and require multiple

reference clock sources at various locations in the system.

This part can function as a clock generating IC for such

applications generating a reference clock for interfaces like

USB, Ethernet, Audio/Video, ADSL, PCI etc.

Figure 25. Application as Clock Generator

Phase

Detector

Charge

Pump

VCO

CMOS/

DIFF

buffer

CMOS /

DIFF

buffer

CMOS

buffer

Feedback

Divider

XIN/CLKIN

XOUT

Crystal

CLK0

VDD

GND

Reference

Clock

Output

Divider

Output

Divider

Output

Divider

PLL Block

VDDO0

CLK1

VDDO1

CLK2

VDDO2

PLL Bypass Mode

Clock Buffer/

Crystal

Oscillator And

AGC

SEL1SEL0

Configuration

Memory

Frequency

and SS

Output control

PD#

Input

Decoder

Crystal /Clock Control

OE0

OE1

OE2

GNDO

25MHz

27MHz

48MHz

25MHz

Video

USB

Ethernet

Buffer and Logic/Level Translator

The NB3H63143G is useful as a simple CMOS Buffer in

PLL bypass mode. One or more outputs can use the PLL

Bypass mode to generate the buffered outputs. If the PLL is

configured to use spread spectrum, all outputs using PLL

Bypass feature will not be subjected to the spread spectrum.

The device can be simultaneously used as logic translator for

converting the LVCMOS input clock to LVPECL, LVDS,

HCSL, CML, or LVCMOS (with different output voltage

level).

For instance in applications like an LCD monitor, for

converting the LVCMOS input clock to LVDS output.