CS3301

DS595F3 7

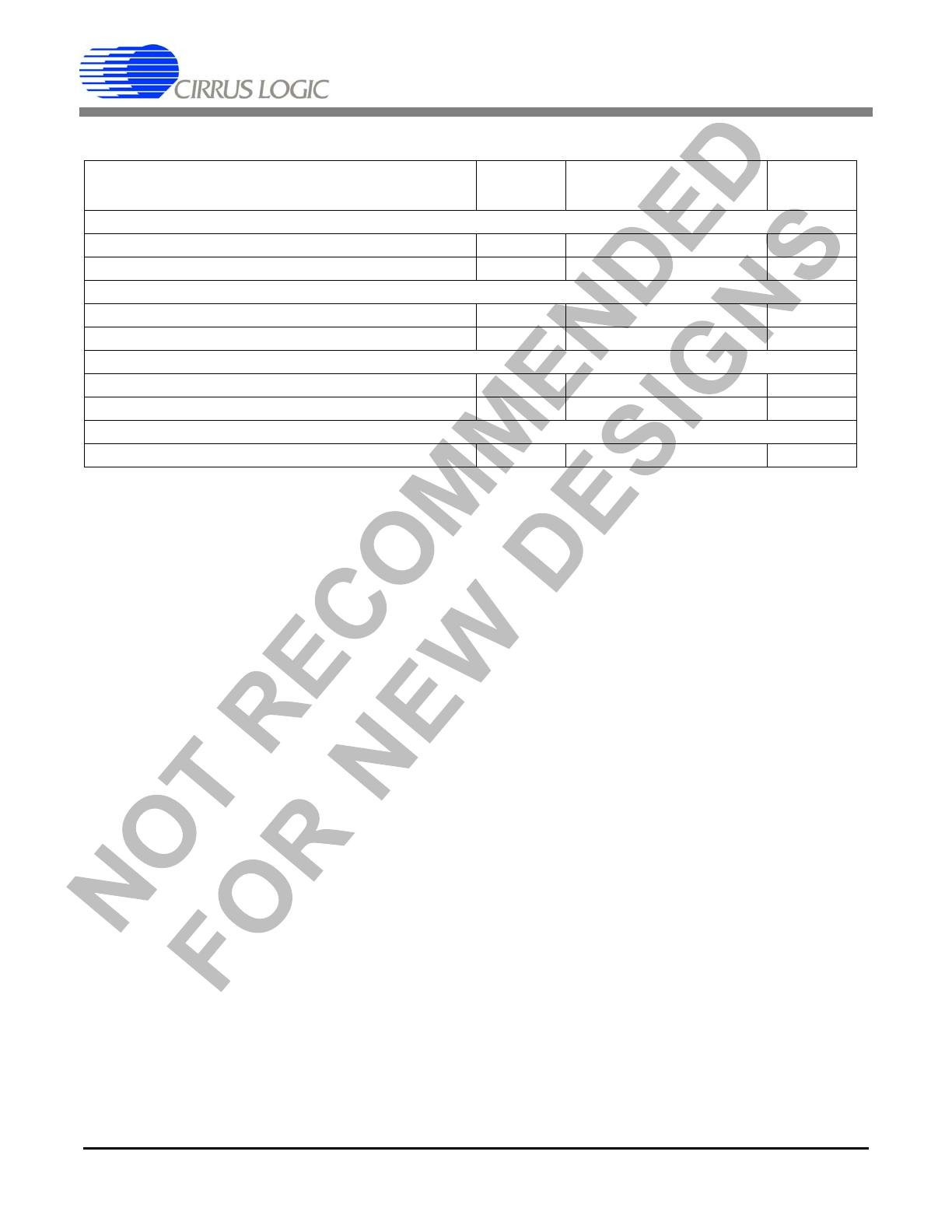

ANALOG CHARACTERISTICS (CONT.)

Notes: 14. No signals operating from external power supplies should be applied to pins of the device prior to its

own supplies being established. Connecting any terminal to voltages greater than VA+ or less than VA-

may cause destructive latch-up.

15. Ratio of common mode input amplitude vs. differential mode output amplitude for a perfectly matched

common mode input signal. Characterized with a 50 Hz, 500 mV

peak

common mode sine wave applied

to the analog inputs.

16. Output impedance characteristics are primarily determined by the integrated anti-alias resistors. Values

are approximate and can vary up to +/- 10% depending on process parameters.

Parameter Symbol

CS3301

UnitMin Typ Max

Analog Input Characteristics

Input Signal Frequencies BW DC - 2000 Hz

Input Voltage Range (Signal + Vcm) x1

(Note 14) x2 - x64

V

IN

(VA-)+0.7

(VA-)+0.7

-

-

(VA+)-1.25

(VA+)-1.75

V

Full Scale Input, Differential x1

x2

x4

x8

x16

x32

x64

V

INFS

-

-

-

-

-

-

-

-

-

-

-

-

-

-

5

2.5

1.25

625

312.5

156.25

78.125

V

p-p

V

p-p

V

p-p

mV

p-p

mV

p-p

mV

p-p

mV

p-p

Input Impedance, Differential Z

INDIFF

-1, 50- GΩ, pF

Input Impedance, Common Mode Z

INCM

-1- MΩ

Input Bias Current I

IN

- 500 1200 pA

Crosstalk, Multiplexed Inputs (Note 4)XT - -130 - dB

Common to Differential Mode Rejection (Note 4, 15)CDMR 90 100 - dB

Analog Output Characteristics

Full Scale Output, Differential V

OUT

--5V

p-p

Output Voltage Range (Signal + Vcm) V

RNG

(VA-)+0.5

-

(VA+)-0.5

V

Output Impedance (Note 16)Z

OUT

-680- Ω

Output Impedance Drift (Note 16)Z

TC

-0.24- Ω/°C

Output Current I

OUT

- - 3.33 mA

Load Capacitance C

L

--100nF