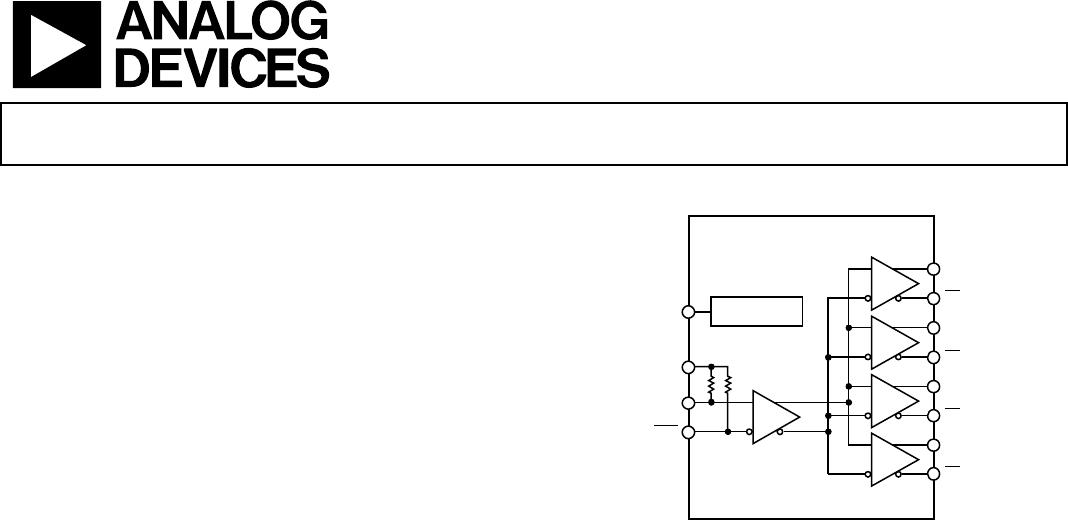

2.5 V/3.3 V, Four LVPECL Outputs,

SiGe Clock Fanout Buffer

ADCLK944

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

FEATURES FEATURES

Operating frequency: 7.0 GHz Operating frequency: 7.0 GHz

Broadband random jitter: 50 fs rms Broadband random jitter: 50 fs rms

On-chip input terminations On-chip input terminations

Power supply (V

CC

− V

EE

): 2.5 V to 3.3 V Power supply (V

CC

− V

EE

): 2.5 V to 3.3 V

APPLICATIONS APPLICATIONS

Low jitter clock distribution Low jitter clock distribution

Clock and data signal restoration Clock and data signal restoration

Level translation Level translation

Wireless communications Wireless communications

Wired communications Wired communications

Medical and industrial imaging Medical and industrial imaging

ATE and high performance instrumentation ATE and high performance instrumentation

FUNCTIONAL BLOCK DIAGRAM FUNCTIONAL BLOCK DIAGRAM

LVPECL

ADCLK944

REFERENCE

REF

V

T

Q0

Q0

Q1

Q1

Q2

CLK

Q2

Q3

Q3

CLK

8770-001

Figure 1.

GENERAL DESCRIPTION

The ADCLK944 is an ultrafast clock fanout buffer fabricated on

the Analog Devices, Inc., proprietary XFCB3 silicon germanium

(SiGe) bipolar process. This device is designed for high speed

applications requiring low jitter.

The device has a differential input equipped with center-tapped,

differential, 100 Ω on-chip termination resistors. The input can

accept dc-coupled LVPECL, CML, 3.3 V CMOS (single-ended),

and ac-coupled 1.8 V CMOS, LVDS, and LVPECL inputs. A V

REF

pin is available for biasing ac-coupled inputs.

The ADCLK944 features four full-swing emitter-coupled logic

(ECL) output drivers. For LVPECL (positive ECL) operation,

bias V

CC

to the positive supply and V

EE

to ground. For ECL

operation, bias V

CC

to ground and V

EE

to the negative supply.

The ECL output stages are designed to directly drive 800 mV

each side into 50 Ω terminated to V

CC

− 2 V for a total differen-

tial output swing of 1.6 V.

The ADCLK944 is available in a 16-lead LFCSP and is specified

for operation over the standard industrial temperature range of

−40°C to +85°C.