5 kV, 7-Channel,

SPIsolator Digital Isolators for SPI

Data Sheet

ADuM4151/ADuM4152/ADuM4153

FEATURES

Supports up to 17 MHz SPI clock speed

4 high speed, low propagation delay, SPI signal isolation

channels

Three 250 kbps data channels

20-lead SOIC_IC package with 8.3 mm creepage

High temperature operation: 125°C

High common-mode transient immunity: >25 kV/µs

Safety and regulatory approvals

UL recognition per UL 1577

5000 V rms for 1 minute SOIC long package

CSA Component Acceptance Notice 5A

VDE certificate of conformity

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

Maximum working insulation voltage (V

IORM

): 849 V peak

APPLICATIONS

Industrial programmable logic controllers (PLCs)

Sensor isolation

GENERAL DESCRIPTION

The ADuM4151/ADuM4152/ADuM4153

1

are 7-channel,

SPIsolator™ digital isolators optimized for isolated serial peripheral

interfaces (SPIs). Based on the Analog Devices, Inc., iCoupler®

chip scale transformer technology, the low propagation delay in

the CLK, MO/SI, MI/SO, and

SS

SPI bus signals supports SPI

clock rates of up to 17 MHz. These channels operate with 14 ns

propagation delay and 1 ns jitter to optimize timing for SPI.

The ADuM4151/ADuM4152/ADuM4153 isolators also provide

three additional independent low data rate isolation channels in

three different channel direction combinations. Data in the slow

channels is sampled and serialized for a 250 kbps data rate with

up to 2.5 µs of jitter in the low speed channels.

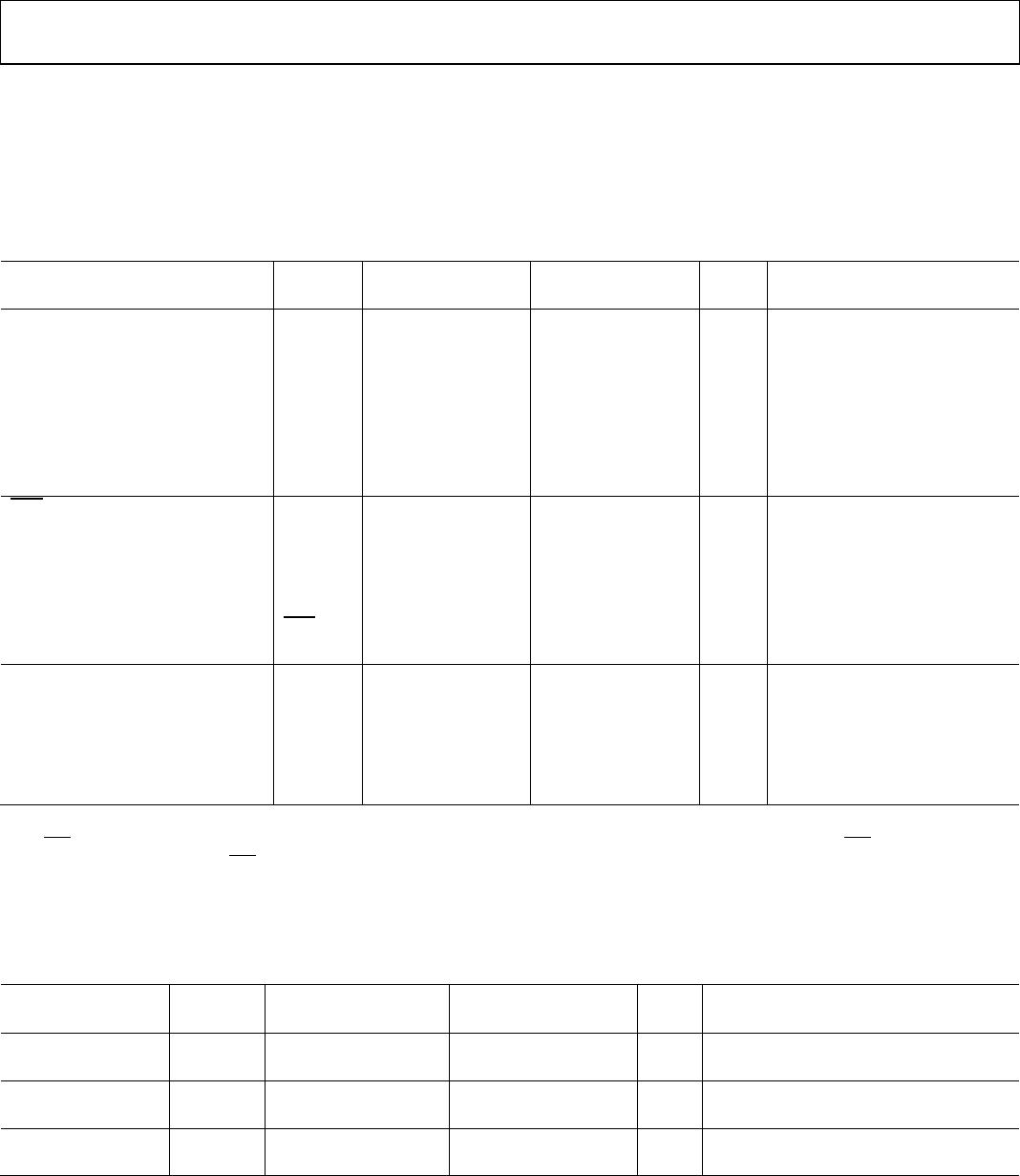

FUNCTIONAL BLOCK DIAGRAMS

ENCODE

CONTROL

BLOCK

DECODE

DECODE ENCODE

ENCODE DECODE

ENCODE

DECODE

V

DD1

GND

1

MCLK

MO

MI

MSS

V

IA

V

IB

V

OC

V

DD2

GND

2

SCLK

SI

SO

SSS

V

OA

V

OB

V

IC

1

2

3

4

5

6

7

8

20

19

18

17

16

15

14

13

GND

1

GND

2

9

10

12

11

ADuM4151

CONTROL

BLOCK

12370-001

Figure 1. ADuM4151 Functional Block Diagram

ENCODE

DECODE

DECODE

ENCODE

ENCODE

DECODE

ENCODE

DECODE

V

DD1

GND

1

MCLK

MO

MI

MSS

V

IA

V

OB

V

OC

V

DD2

GND

2

SCLK

SI

SO

SSS

V

OA

V

IB

V

IC

1

2

3

4

5

6

7

8

20

19

18

17

16

15

14

13

GND

1

GND

2

9

10

12

11

ADuM4152

CONTROL

BLOCK

CONTROL

BLOCK

12370-002

Figure 2. ADuM4152 Functional Block Diagram

ENCODE

DECODE

DECODE ENCODE

ENCODE DECODE

ENCODE DECODE

V

DD1

GND

1

MCLK

MO

MI

MSS

V

OA

V

OB

V

OC

V

DD2

GND

2

SCLK

SI

SO

SSS

V

I

A

V

IB

V

IC

1

2

3

4

5

6

7

8

20

19

18

17

16

15

14

13

GND

1

GND

2

9

10

12

11

ADuM4153

CONTROL

BLOCK

CONTROL

BLOCK

12370-003

Figure 3. ADuM4153 Functional Block Diagram

1

Protected by U.S. Patents 5,952,849; 6,873,065; 6,262,600; and 7,075,329. Other patents are pending.

Rev. A

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2014–2015 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com