ADuM4151/ADuM4152/ADuM4153 Data Sheet

For example, at a magnetic field frequency of 1 MHz, the

maximum allowable magnetic field of 0.5 kgauss, induces a

voltage of 0.25 V at the receiving coil. This voltage is about 50%

of the sensing threshold and does not cause a faulty output

transition. If such an event occurs, with the worst-case polarity,

during a transmitted pulse, the interference reduces the

received pulse from >1.0 V to 0.75 V. This voltage is still well

above the 0.5 V sensing threshold of the decoder.

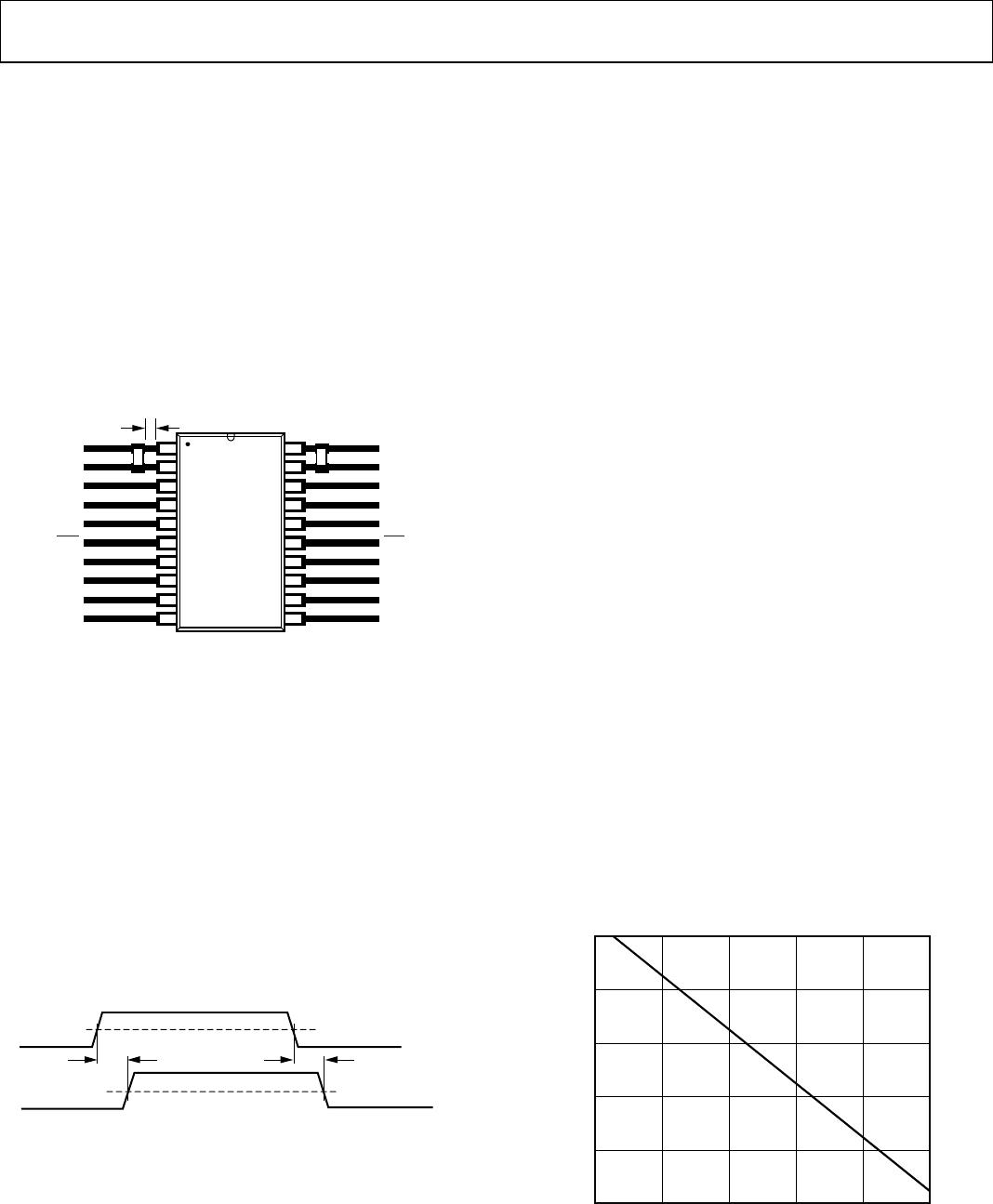

The preceding magnetic flux density values correspond to

specific current magnitudes at given distances away from the

ADuM4151/ADuM4152/ADuM4153 transformers. Figure 18

expresses these allowable current magnitudes as a function of

frequency for selected distances. The ADuM4151/ADuM4152/

ADuM4153 are insensitive to external fields. Only extremely

large, high frequency currents, very close to the component are

a concern. For the 1 MHz example noted, placing a 1.2 kA

current 5 mm away from the ADuM4151/ADuM4152/

ADuM4153 affects component operation.

MAGNETIC FIELD FREQUENCY (Hz)

MAXIMUM ALLOWABLE CURRENT (kA)

1000

100

10

1

0.1

0.01

1k 10k 100M100k 1M 10M

DISTANCE = 5mm

DISTANCE = 1m

DISTANCE = 100mm

12370-018

Figure 18. Maximum Allowable Current for Various Current to

ADuM4151/ADuM4152/ADuM4153 Spacings

At combinations of strong magnetic field and high frequency,

any loops formed by the PCB traces may induce sufficiently

large error voltages to trigger the thresholds of succeeding

circuitry. Take care to avoid PCB structures that form loops.

POWER CONSUMPTION

The supply current at a given channel of the ADuM4151/

ADuM4152/ADuM4153 isolators is a function of the supply

voltage, the data rate of the channel, and the output load of the

channel and whether it is a high or low speed channel.

The low speed channels draw a constant quiescent current

caused by the internal ping-pong datapath. The operating

frequency is low enough that the capacitive losses caused by

the recommended capacitive load are negligible compared to

the quiescent current. The explicit calculation for the data rate

is eliminated for simplicity, and the quiescent current for each

side of the isolator due to the low speed channels can be found

in Table 3, Table 6, Table 9, and Table 12 for the particular

operating voltages.

These quiescent currents add to the high speed current as is

shown in the following equations for the total current for each

side of the isolator. Dynamic currents are taken from Table 3

and Table 6 for the respective voltages.

For Side 1, the supply current is given by

I

DD1

= I

DDI(D)

× (f

MCLK

+ f

MO

+ f

MSS

) +

f

MI

× (I

DDO(D)

+ ((0.5 × 10

−3

) × C

L(MI)

× V

DD1

)) + I

DD1(Q)

For Side 2, the supply current is given by

I

DD2

= I

DDI(D)

× f

SO

+

f

SCLK

× (I

DDO(D)

+((0.5 × 10

−3

) × C

L(SCLK)

× V

DD2

)) +

f

SI

× (I

DDO(D)

+((0.5 × 10

−3

) × C

L(SI)

× V

DD2

)) +

f

SSS

× (I

DDO(D)

+((0.5 × 10

−3

) × C

L(

SSS

)

× V

DD2

)) + I

DD2(Q)

where:

I

DDI(D)

, I

DDO(D)

are the input and output dynamic supply currents

per channel (mA/Mbps).

f

x

is the logic signal data rate for the specified channel (Mbps).

C

L(x)

is the load capacitance of the specified output (pF).

V

DDx

is the supply voltage of the side being evaluated (V).

I

DD1(Q)

, I

DD2(Q)

are the specified Side 1 and Side 2 quiescent

supply currents (mA).

Figure 8 and Figure 11 show the typical supply current per

channel as a function of data rate for an input and unloaded

output. Figure 9 and Figure 12 show the total I

DD1

and I

DD2

supply

currents as a function of data rate for the ADuM4151/ADuM4152/

ADuM4153 channel configurations with all high speed channels

running at the same speed and the low speed channels at idle.

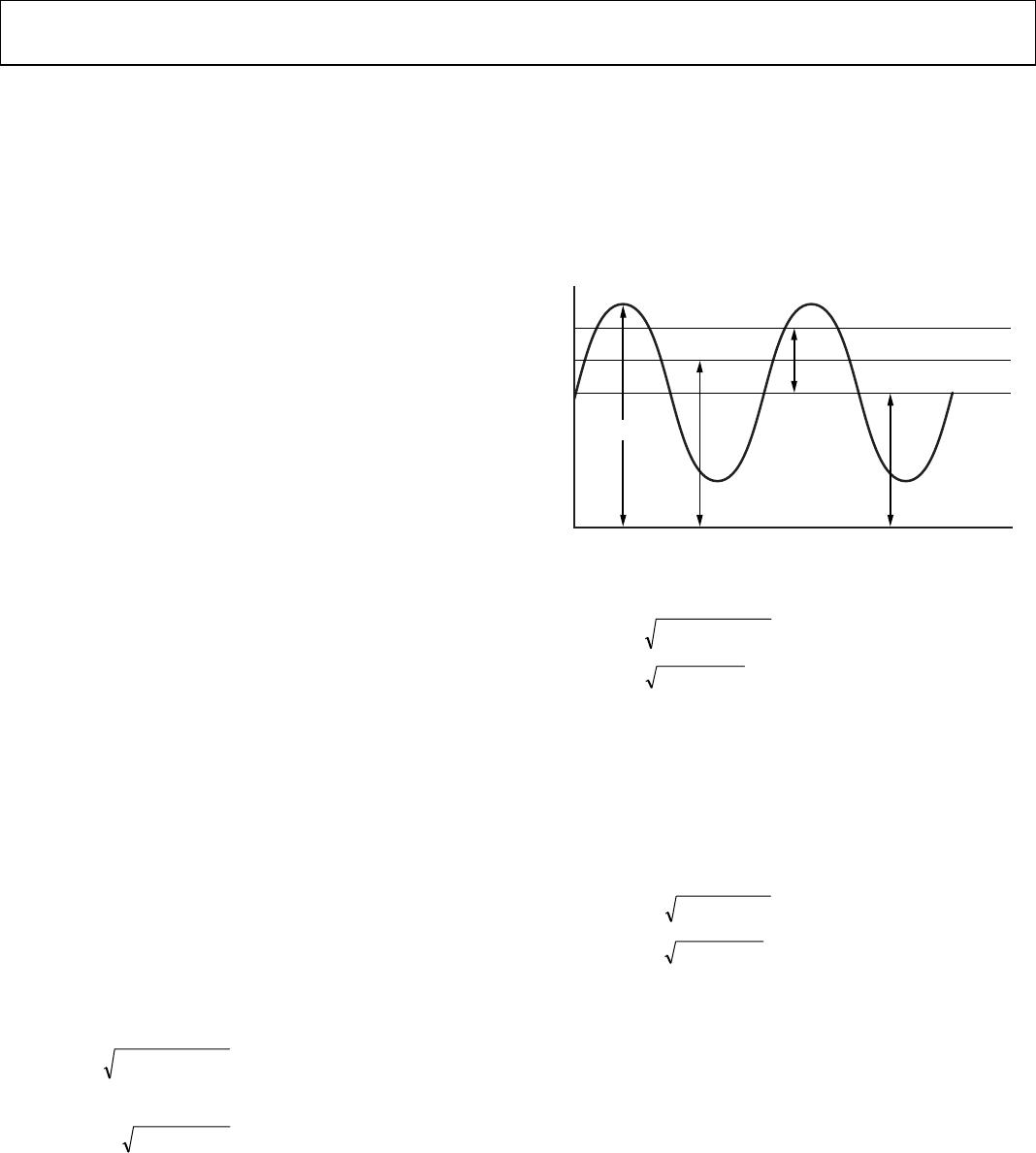

INSULATION LIFETIME

All insulation structures eventually break down when subjected

to voltage stress over a sufficiently long period. The rate of

insulation degradation is dependent on the characteristics of the

voltage waveform applied across the insulation as well as the

materials and material interfaces.

Two types of insulation degradation are of primary interest:

breakdown along surfaces exposed to the air and insulation

wear out. Surface breakdown is the phenomenon of surface

tracking and the primary determinant of surface creepage

requirements in system level standards. Insulation wear out is

the phenomenon where charge injection or displacement

currents inside the insulation material cause long-term

insulation degradation.

Rev. A | Page 20 of 22